用于流水線ADC的無采樣保持運放前端電路

陳迪平 張仁梓 曹倫武 陳卓俊 曾健平

摘? ?要:為了降低流水線模數(shù)轉(zhuǎn)換器功耗與提升輸入信號范圍,設(shè)計了一種無采樣保持運放前端電路. 移除采樣保持運放降低了功耗,并改進(jìn)開關(guān)時序進(jìn)一步降低電路功耗;同時改進(jìn)傳統(tǒng)開關(guān)電容比較器輸入,使得模數(shù)轉(zhuǎn)換器可達(dá)到0 ~ 3.3 V滿電源電壓的量化范圍. 將設(shè)計的無采樣保持運放前端電路應(yīng)用在一款低功耗12位50 MS/s流水線模數(shù)轉(zhuǎn)換器進(jìn)行驗證,采用0.18 μm 1P6M工藝進(jìn)行流片,芯片面積為1.95 mm2. 測試結(jié)果表明:3.3 V電壓下,采樣率為50 MS/s、輸入信號頻率為5.03 MHz時,信噪失真比(SNDR)為64.67 dB,無雜散動態(tài)范圍(SFDR)為72.9 dB,功耗為65 mW.

關(guān)鍵詞:流水線模數(shù)轉(zhuǎn)換器;無采樣保持運放;孔徑誤差;開關(guān)電容比較器

中圖分類號:TN495? ? ? ? ? ? ? ? ? ? ? ? ? ?文獻(xiàn)標(biāo)志碼:A

Front-end Circuit without Sample-and-hold

Amplifier for Pipelined ADC

CHEN Diping1,ZHANG Renzi1?,CAO Lunwu2,CHEN Zhuojun1,ZENG Jianping1

(1. College of Physics and Microelectronics Science,Hunan University,Changsha? 410082,China;

2. Hunan Advancechip Electronic Technology Company,Changsha 410205,China)

Abstract:A front-end circuit without Sample-and-Hold Amplifier(SHA)? is presented for reducing power consumption and increasing input range of pipelined ADC. Removing Sample-and-Hold Amplifier and improving switching timing reduce the circuit power consumption,while improving the traditional switched-capacitor comparator inputs to make ADC achieve a 0-3.3V full supply voltage quantization range. The front-end circuit without Sample-and Hold Amplifier is verified in a low power 12 bit 50 MS/s pipelined ADC. The circuit is implemented in a 0.18 μm 1P6M process,and occupies a chip area of 1.95 mm2. The test? results with a 5.03 MHz input wave under a sampling rate of 50 MS/s show that the ADC achieves a 64.67 dB signal-to-noise and distortion ratio(SNDR)? as well as a 72.9 dB spurious-free dynamic range(SFDR),while it consumes the power consumption of 65 mW.

Key words:pipelined Analog to Digital Converter(ADC);Sample-and-Hold Amplifier(SHA)-less;aperture error;switched-capacitor comparator

高速高精度模數(shù)轉(zhuǎn)換器(Analog to Digital Converter,ADC)是如今眾多高性能數(shù)模混合電路系統(tǒng)中不可或缺的部分[1-4].隨著工藝水平的提高以及便攜式電子設(shè)備的興起,高速低功耗ADC[5-6]也正成為研究熱點. 常見的ADC有流水線型(Pipelined)[7-8]、逐次比較型(Successive Approximation Register,SAR)[9]、混合型(Pipelined-SAR)[10]、過采樣型(Sigma Delta,Δ-Σ)[11]等,而Pipelined ADC因其較快的速度、較高的精度以及適中的功耗而被廣泛應(yīng)用.

為達(dá)到低功耗Pipelined ADC設(shè)計要求,研究者們提出了許多降低功耗方法,如運放共享技術(shù)[12]、無前端采樣保持運放技術(shù)(Sample-and-Hold Amplifier-less,SHA-less)[13-14]等. 傳統(tǒng)Pipelined ADC設(shè)計中,為使子ADC和余量增益電路(Multiplying Digital-to-Analog Converter,MDAC)兩條路徑傳輸信號一致,信號通過采樣保持電路(Sample-and-Hold Amplifier,SHA)后才開始逐級量化. 由于SHA電路位于ADC最前端,為達(dá)到高速高精度目的,系統(tǒng)對SHA中運放的增益與帶寬具有很高要求,從而消耗巨大功耗. 因此,降低Pipelined ADC功耗的一種有效方法是移除采樣保持運放. SHA電路具有穩(wěn)定兩條信號路徑一致性和電平轉(zhuǎn)移功能,移除采樣保持運放會帶來孔徑誤差[14]及輸入信號范圍變小等問題. 因此,采用SHA-less電路,需要進(jìn)一步優(yōu)化設(shè)計.

本文設(shè)計了一種適用于低功耗高精度SHA-less Pipelined ADC的前端電路,改進(jìn)開關(guān)時序減小首級ADC比較器導(dǎo)通時間來降低功耗和消除孔徑誤差,同時改進(jìn)傳統(tǒng)開關(guān)電容比較器輸入,使得ADC可量化輸入信號電平達(dá)到0~3.3 V滿電源電壓. 所設(shè)計的電路應(yīng)用在一款中低端DSP芯片中的低功耗12位50MS_s_Pipelined ADC進(jìn)行驗證,采用0.18 μm 1P6M工藝進(jìn)行電路設(shè)計仿真及流片,測試結(jié)果良好.

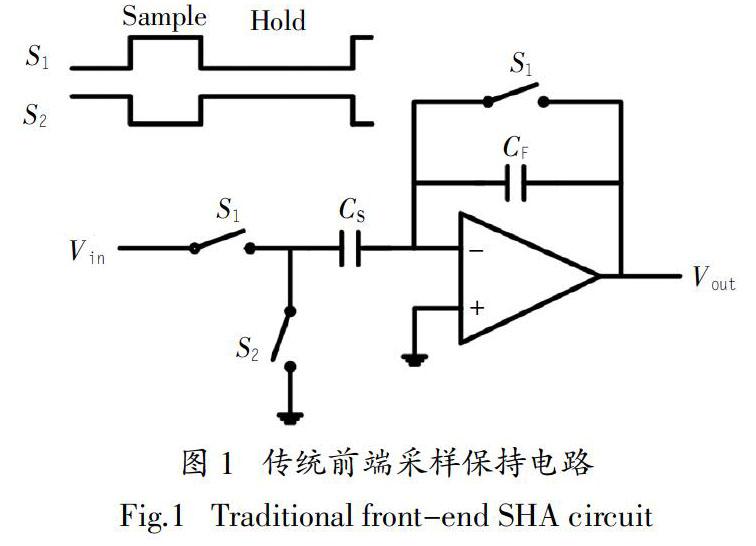

1? ?傳統(tǒng)前端SHA電路

圖1所示為傳統(tǒng)前端SHA電路原理圖. 采樣相時,開關(guān)S1閉合,S2斷開,采樣電容CS對輸入信號進(jìn)行采樣;保持相時,開關(guān)S1斷開,S2閉合,電容CS上的電荷往反饋電容CF上進(jìn)行轉(zhuǎn)移,最終得到輸出Vout = Vin CS /CF. 在下一次采樣時刻到來前,輸出將保持不變. 因此,在保持相,信號往首級子ADC與MDAC傳輸時,兩條路徑不會存在偏差. 同時,若輸入信號電平超出首級ADC量化范圍時,可以通過設(shè)置合理的CS /CF比值,將輸入信號進(jìn)行電平變換后再進(jìn)行量化.

由于SHA電路位于Pipelined ADC最前端,因此系統(tǒng)對SHA電路中運放的增益與帶寬具有很高要求,導(dǎo)致SHA電路消耗巨大功耗,通常占據(jù)整個系統(tǒng)功耗的30%[15]以上. 因此,在低功耗Pipelined ADC設(shè)計中,移除前端SHA電路中的運放顯得很有必要. SHA-less的前端電路信號傳輸路徑如圖2所示,輸入信號傳輸存在兩條路徑,一條為信號直接送入首級ADC進(jìn)行量化,另一條為送入采樣電路. 若兩條通道時間常數(shù)不匹配,將會產(chǎn)生孔徑誤差,從而降低整個系統(tǒng)量化精度.

由式(1)和圖3可知,ADC可量化的最大信號輸入電平為ΔVREF = VREFP - VREFN. 增大ADC可量化的輸入信號電平,只能增大基準(zhǔn)電壓VREFP、VREFN差值,但不能達(dá)到滿電源電壓輸入. 考慮到Pipelined ADC由多級子ADC組成,若保持圖3中電阻串阻值不變,增大基準(zhǔn)電壓VREFP - VREFN差值將會明顯增加功耗,同時對基準(zhǔn)電壓VREFP、VREFN產(chǎn)生電路的電流驅(qū)動能力要求也增高,從而導(dǎo)致基準(zhǔn)電壓產(chǎn)生電路面積大幅增加;若增大電阻串阻值以降低功耗和基準(zhǔn)電壓產(chǎn)生電路的電流驅(qū)動能力,由圖4所示保持相比較器等效輸入可知,時間常數(shù)τ = Rep·VREFP、Co將會大幅增加,比較器工作速度降低,從而降低ADC量化速度. 因此,圖3所示比較器電路不適合高輸入信號電平的SHA-less Pipelined ADC.

2? ?SHA-less Pipelined ADC前端電路

圖5為本文設(shè)計的SHA-less前端電路結(jié)構(gòu)圖,電路為全差分結(jié)構(gòu),為簡化這里只給出單端電路圖. 電路共有16個比較器,可實現(xiàn)4 bit首級子ADC功能. 圖中給出了部分開關(guān)時序,ADC采樣開關(guān)φ1在采樣電容CS開關(guān)φs后導(dǎo)通,降低了比較器導(dǎo)通工作時間,進(jìn)一步減小部分電路功耗. 因為采樣時刻不一致產(chǎn)生的誤差,可以通過兩條采樣路徑阻抗不匹配誤差進(jìn)行抵消以達(dá)到數(shù)字邏輯可校準(zhǔn)范圍. 比較器改進(jìn)輸入可實現(xiàn)滿電源電壓輸入,具體工作原理后面將做詳細(xì)討論.

2.1? ?孔徑誤差的消除

根據(jù)校正原理,總誤差需滿足式(2):

其中,總誤差包括比較器輸入失調(diào)、孔徑誤差、基準(zhǔn)源誤差等;VFS是ADC滿輸入量程;AV是MDAC增益. 本文設(shè)計中,ADC輸入為滿電源電壓量程,即0~3.3 V;首級MDAC增益為8. 假設(shè)因為兩條信號路徑不匹配帶來的孔徑誤差Verror_mismatch占總誤差的一半,則可得:

Verror_mismatch < 51.56 mV? ? ? (3)

圖5給出的部分開關(guān)時序圖,與傳統(tǒng)開關(guān)時序不同,為了減少比較器導(dǎo)通時間以降低ADC功耗,比較器采樣開關(guān)φ1在采樣電容開關(guān)φS后導(dǎo)通. 此處引起的誤差可以通過采樣路徑不匹配進(jìn)行抵消. 假設(shè)輸入信號為一正弦波:

Vin = A0 sin ωt? ? ? (4)

采樣電容CS和ADC分別在t1、t2時刻對輸入信號進(jìn)行采樣,兩條路徑產(chǎn)生的延遲分別為τ1、τ2 . 因此產(chǎn)生的誤差為:

Verror_mismatch ≌ A0 [sin ω(t1+τ1)-sin ω(t2+τ2)]? (5)

輸入正弦波信號在過零處,式(5)所示的誤差將會呈現(xiàn)最大值:

Verror_mismatch_max ≌ A0 [sin ω(t1-t2)+sin ω(τ1-τ2)]? (6)

通過合理設(shè)置開關(guān)φS和φ1尺寸,使得Δτ = τ1-τ2 = Rons CS - Ron1 CO與Δt = t1 - t2相抵消,以使誤差最小. 其中,Rons、Ron1分別為開關(guān)φS和φ1的導(dǎo)通阻抗. 本設(shè)計通過不斷提取參數(shù)進(jìn)行后仿真來優(yōu)化電路設(shè)計與版圖匹配,使得在50 MS/s采樣率下,輸入正弦波頻率達(dá)10 MHz時,孔徑誤差為11 mV,滿足式(3)要求且有較大余量.

2.2? ?首級子ADC可量化輸入信號電平的提升

由第1節(jié)的分析可知,采用SHA-less結(jié)構(gòu)后,首級ADC能量化的最大輸入信號電平將會變小. 如圖5所示,本設(shè)計對傳統(tǒng)電容開關(guān)比較器輸入進(jìn)行改進(jìn),通過設(shè)置合理的VREFP、VREFN值,可以使得ADC達(dá)到0 ~ 3.3 V的滿電源電壓輸入.

比較器輸出如式(7)所示.

由式(7)可知,輸入信號ΔVin = Vinp - Vinn,減去一個固定直流量ΔVREF = VREFP - VREFN后再與參考電壓做比較,實現(xiàn)了輸入信號電平變換的功能. 因此,合理設(shè)置VREFP、VREFN的值,可以實現(xiàn)ADC滿電源電壓的輸入. 本設(shè)計中,Vrefp - Vrefn的取值為:

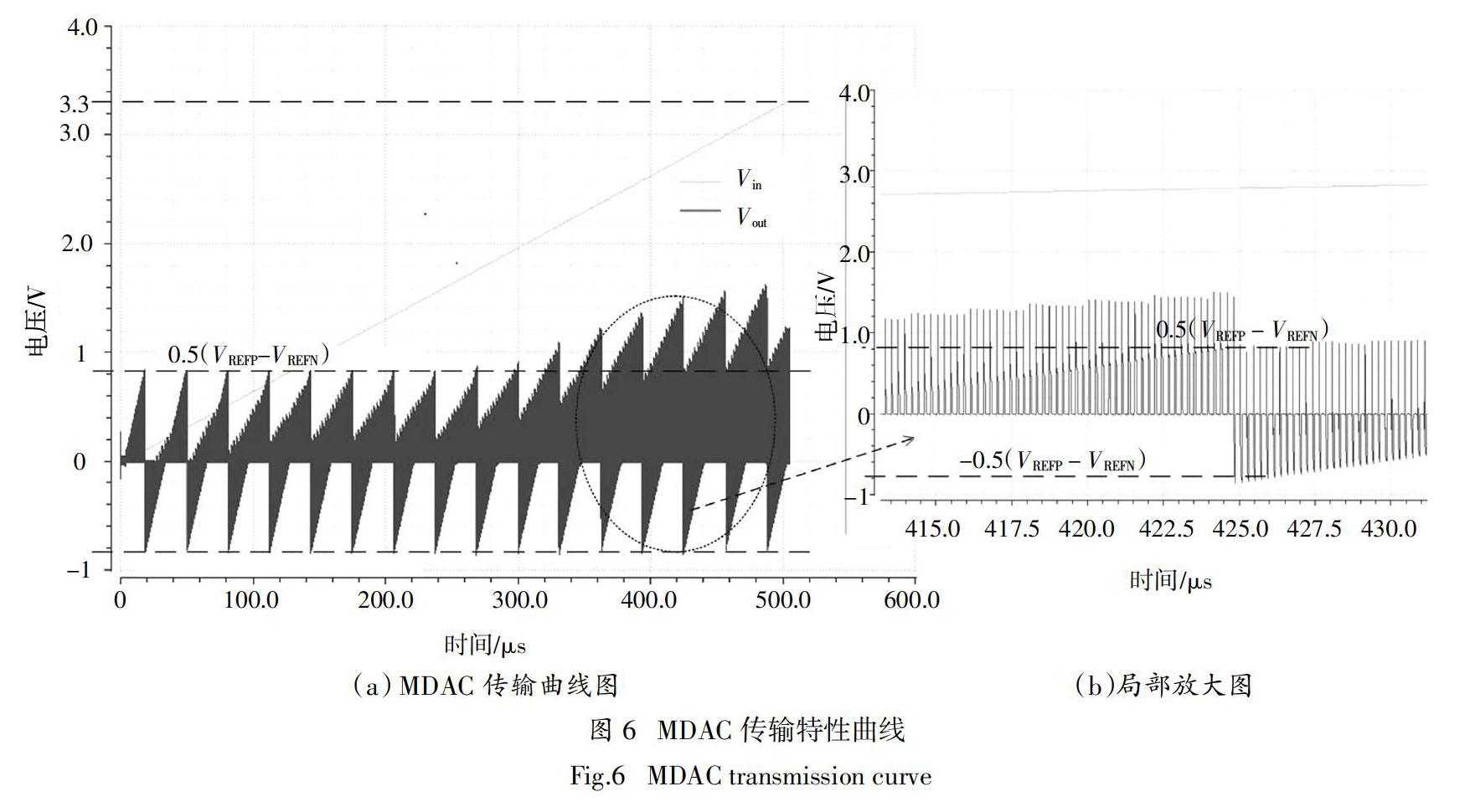

因此可得VREFP - VREFN? = 1.65 V,結(jié)合電路設(shè)計的VREFP + VREFN共模值,便可確定VREFP、VREFN的值. 圖6為0 ~ 3.3 V滿幅輸入時,運放輸出的曲線圖. 由圖可以看出,ADC可以實現(xiàn)0 ~ 3.3 V滿電源電壓量化范圍.

3? ?SHA-less前端電路應(yīng)用及測試結(jié)果

本文設(shè)計的SHA-less前端電路已成功應(yīng)用于一款12位50 MS/s的pipelined ADC芯片中,結(jié)構(gòu)圖如圖7所示. 12位50 MS/s的pipelined ADC采用4+3+3+3的四級流水結(jié)構(gòu),為降低ADC整體功耗,首級采用了本文設(shè)計的4bit SHA-less結(jié)構(gòu),電路0.18 μm 1P6M工藝進(jìn)行設(shè)計及流片.

圖8為芯片照片圖,面積為1.95 mm2.

圖9為ADC測試的線性度曲線,微分非線性(Differential NonLinearity,DNL)誤差為-0.61/+0.61LSB,積分非線性(Integral NonLinearity INL)誤差為-0.82/+0.7LSB.

圖10顯示了在3.3 V電源電壓下,采樣率為50 MS/s、輸入信號為5.03 MHz時的測試FFT頻譜圖,信噪比(Signal to Noise Ratio,SNR)為65.03 dB,信噪失真比(Signal to Noise and Distoration Ratio,SNDR)為64.67 dB,無雜散動態(tài)范圍(Spurious Free Dynamic Range,SFDR)為72.9 dB,整體功耗為65 mW. 功耗與具有采樣保持運放的相似架構(gòu)流水線ADC相比[3],降低了40%.

表1給出了文中所設(shè)計ADC與部分參考文獻(xiàn)提出的ADC性能對比,可以看出本文設(shè)計具有較小的功耗與精度、面積以及最大的輸入范圍.

4? ?結(jié)? ?論

本文提供了一種適用于低功耗Pipelined ADC設(shè)計的無采樣保持運放的前端電路. 改進(jìn)采樣開關(guān)時序減小了電路功耗,同時改進(jìn)傳統(tǒng)開關(guān)電容比較器輸入,使得ADC可量化0~3.3 V滿電源電壓輸入信號電平. 將所設(shè)計的SHA-less前端電路應(yīng)用在一款12位50MS/s Pipelined ADC進(jìn)行驗證,采用0.18 μm 1P6M工藝進(jìn)行流片,整體ADC面積為1.95 mm2,測試結(jié)果良好.

參考文獻(xiàn)

[1]? ? MOHAMED M Y,HEGAZI E,EI-NOZAHI M. A 0.35 mW 8-bit 140MS/s asynchronous hybrid ADC for low energy radio applications[C]// 2019 36th National Radio Science Conference. Piscataway: IEEE,2019:315—323.

[2]? ? JEON B K,HONG S K,KWON O K. A low-power 12-Bit extended counting ADC without calibration for CMOS image sensors[J]. IEEE Transactions on Circuits and Systems II:Express Briefs,2018,65(7):824—828.

[3]? ? MATHUR S,DAS M,TADEPARTHY,et al. A 115mW 12-bit 50 MSPS pipelined ADC[C]// 2002 IEEE International Symposium on Circuits and Systems. Piscataway:IEEE,2002:913—916.

[4]? ? CHEN T,PENG L L,LI H B,et al. A 2-V 40-MS/s 14-bit pipelined ADC for CMOS image sensor[C]// 2015 IEEE 11th International Conference on ASIC. Piscataway:IEEE,2015:1—4.

[5]? ? OHHATA K,HAYAKAWA D,SEWAKI K,et al. A 900-MHz,3.5-mW,8-bit pipelined subranging ADC combining flash ADC and TDC[J]. IEEE Transactions on Very Large Scale Integration(VLSI) Systems,2018,26(9):1777—1787.

[6]? ? ZHOU Y,XU B W,CHIU Y. A 12-b 1-GS/s 31.5-mW time-interleaved SAR ADC with analog HPF-Assisted skew calibration and randomly sampling reference ADC[J]. IEEE Journal of Solid-State Circuits,2019,54(8):2207—2218.

[7]? ? 陽輝,何怡剛,黃姣英. 0.25μm CMOS工藝10位150MHz流水線型ADC設(shè)計[J]. 湖南大學(xué)學(xué)報(自然科學(xué)版),2010,37(8):45—48.

YANG H,HE Y G,HUANG J Y.A 10-b 150MHz pipeline ADC in 0.25μm CMOS[J]. Journal of Hunan University(Natural Sciences),2010,37(8):45—48.(In Chinese)

[8]? ? WU H J,CHEN Z H,YU Z G,et al. A 12-bit 250MSPS pipeline ADC with 4Gbps serial output interface[C]//2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology. Piscataway:IEEE,2016:1464—1466.

[9]? ? OKUNO K,OBATA K,KATO T,et al. An 800-MHz 8-bit high speed SAR ADC in 16nm FinFET process[C]//2017 IEEE International Meeting for Future of Electron Devices,Kansai. Piscataway:IEEE,2017:24—25.

[10]? LIU H Z,LIU M L,ZHU Z M. A 12-bit 200MS/s pipelined-SAR ADC in 65-nm CMOS with 61.9 dB SNDR[C]//2019 IEEE International Conference on Electron Devices and Solid-State Circuits. Piscataway:IEEE,2019:1—2.

[11]? 于健海,尹亮. 用于微機械加速度計的亞微米工藝ADC設(shè)計[J]. 西安電子科技大學(xué)學(xué)報,2019,46(3):140—147.

YU J H,YIN L. Design of an ADC with the submicron process for micromechanical accelerometers[J]. Journal of Xidian University,2019,46(3):140—147. (In Chinese)

[12]? CHO J K. A 2.24-mW,61.8-dB SNDR,20-MS/s pipelined ADC with charge-pump-based dynamic biasing for power reduction in Op AMP sharing[J]. IEEE Transactions on Circuits and Systems I:Regular Papers,2017,64(6):1368—1379.

[13]? XU W G,GAO Y F,LIU X D,et al. A 18 mW 12 bit 50MS/s SHA-less pipelined ADC[C]//2017 IEEE 12th International Conference on ASIC. Piscataway:IEEE,2017:776—779.

[14]? WANG C W,WANG X,DING Y,et al. A 14-bit 250MS/s low-power pipelined ADC with aperture error eliminating technique[C]//2018 IEEE International Symposium on Circuits and Systems. Piscataway:IEEE,2018:1—5.

[15]? 張凌東,魏敬和,陳珍海,等. 用于16位125MS_s ADC的無采樣保持運放前端電路[J]. 中國電子科學(xué)研究院學(xué)報,2018,13(3):331—334.

ZHANG L D,WEI J H,CHEN Z H,et al. Front-end circuit without sample-and-hold amplifier for 16bit 125MS/s ADC[J]. Journal of CAEIT,2018,13(3):331—334. (In Chinese)