一種基于AD9266和AD9361的衛星中頻信道設計

宋 穎,朱小流

(南京熊貓漢達科技有限公司,江蘇 南京 210000)

1 應用背景

隨著衛星通信技術發展,對設備的體積、功耗、集成化程度要求越來越苛刻,這必然需要在一個較小的空間同時實現中頻下行接收通道和中頻上行發送通道,完成AD/DA的轉換;進行數字信號處理,并完成與外部設備的通信交互。由于數字電路“0/1”跳變的特性,隨著處理頻率的提高,其對模擬信號電路的影響越來越大,且不可忽略[1-2]。在設計模擬中頻通道時,必須采取保護措施,屏蔽來自數字電路的干擾;或采取合理的設計,增強模擬電路自身的抗干擾能力。

2 設計實現

本設計可分為中頻下行接收通道、中頻上行發送通道、AD/DA轉換電路3部分組成。

2.1 中頻下行接收通道能力

(1)中心頻率:2 180~2 200 MHz,步進100 Hz。

(2)信號帶寬:30 kHz。

(3)輸入電平:-100~-70 dBm。

2.2 中頻上行發送通道能力

(1)中心頻率:1 970~2 010 MHz,步進100 Hz。

(2)輸出電平:-15~-15 dBm。

(3)相位噪聲:

≤-60 dBc/@100 Hz;

≤-70 dBc/@1 kHz;

≤-80 dBc/@10 kHz;

≤-90 dBc/@100 kHz。

(4)輸出雜散:≤-70 dBc。

(5)載波泄露:≤-40 dBc。

2.3 AD/DA轉換電路

A/D轉換電路由高性能的AD芯片AD9266實現,D/A轉換由芯片AD9361實現。AD9361既能實現A/D轉換,又能實現D/A轉換,但本設計中只使用其D/A轉換部分功能。這是由于AD9361的下行接收濾波帶寬只有200 kHz,而本設中下行接收信號帶寬為30 kHz,未減小數字信號處理的難度,故未使用AD9361設計下行接收通道。

本設計在有限的空間內,同時實現了高靈敏度、大動態范圍的下行接收通道和具有高質量相位噪聲、雜散、載波泄露性能的上行發送通道。最小接收電平“-100 dBm”和最大輸出電平“+15 dBm”之間的電平差達“115 dBm”。這使得本設計具有更廣泛的應用范圍,可以應用在多種衛星通信環境中,同時也增加了設計的難度。

3 方案原理

3.1 下行接收通道

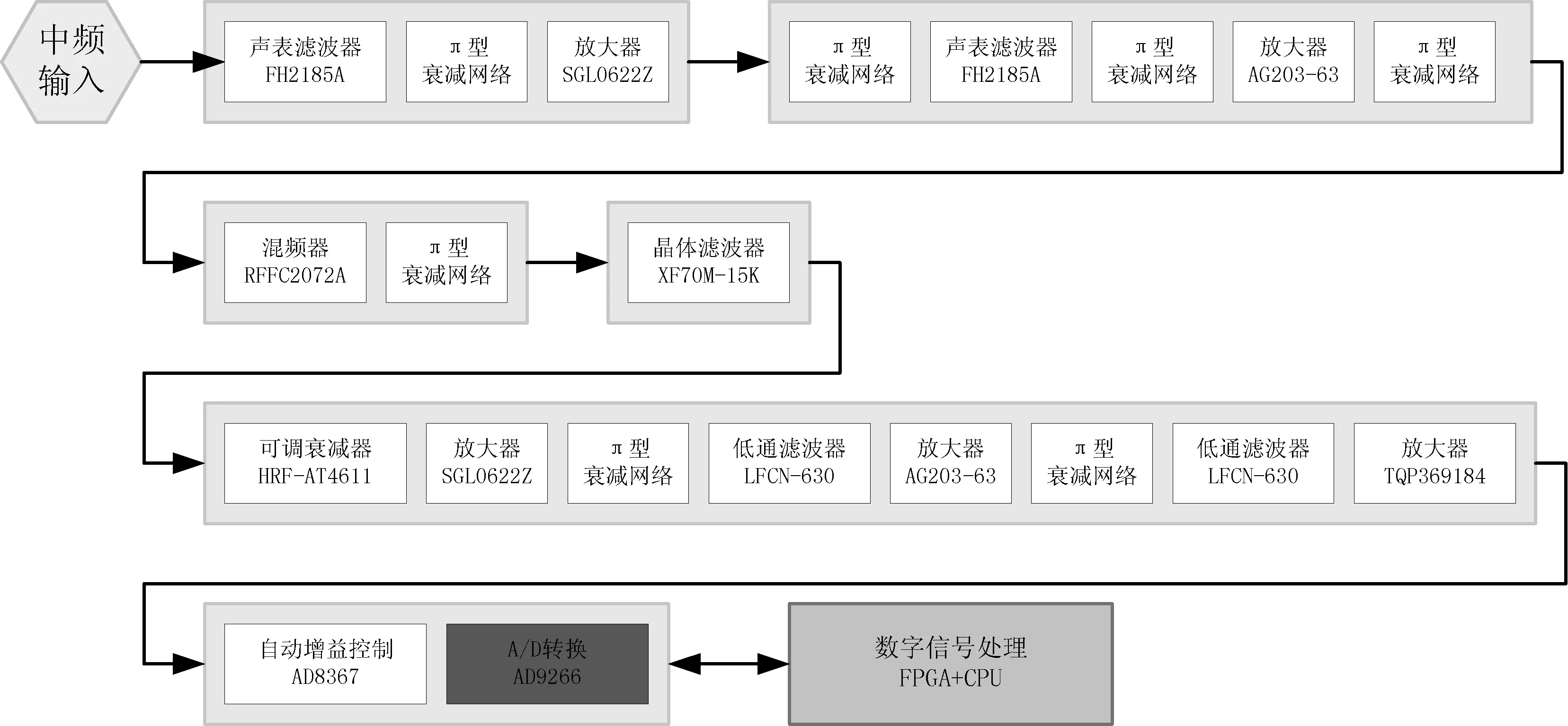

下行接收通道采用超外差架構技術,主要由放大器、數控衰減器、混頻器、鎖相本振源、聲表面濾波器、中頻放大器和低通濾波器等部分組成[3]。來自射頻前端組件輸入的中頻信號,經過放大和濾波后,通過混頻器將其搬移至70 MHz處,濾波器帶寬為30 kHz。由于單個聲表面濾波器抑制帶外干擾能力有限,在本設計中采用了兩級級聯聲表面濾波器抑制帶外干擾;混頻后通過晶體濾波器和低通濾波器共同抑制本振信號泄露信號和其他干擾噪聲;最后經過自動增益控制AGC電路調整后,將70 MHz低中頻信號傳送至AD9266轉換成數字信號,發送給基帶FPGA、CPU等處理。下行接收通道方案設計如圖1所示。

圖1 下行接收通道方案原理

由于下行接收通道的輸入信號最低只有“-100 dBm”,因此必須經過足夠的放大處理,才能被A/D轉換芯片AD9266處理。如果采用一級放大電路,放大倍數必然很大,容易造成自激,故在本設計中采用了多級級聯放大濾波的方案,且在硬件設計中每級均用屏蔽罩蓋住,以阻止本級電路向外的輻射電磁干擾,并屏蔽外部電磁輻射干擾。在上圖中每個框均為一級,每級均用屏蔽罩蓋住;在混頻前有兩級,混頻后有3級。下行接收通道的增益分配如圖2所示。

圖2 下行接收通道增益分配

3.2 上行發送通道

上行發送通道采用零中頻方案,即基帶直接調制至中頻工作頻點,主要由AD9361、聲表面濾波器、放大器和可控衰減器組成。AD9361是一款優秀的數模轉換芯片,其上行通道中集成了放大器、高性能鎖相環和IQ調制/解調器,這無疑減小了設計的復雜度和印制板布局空間需求。聲表面濾波器用于濾除中頻信號帶外干擾,使得發送的信號更純凈。數控衰減器用于調整發送信號的電平大小。上行發送通道方案設計如圖3所示。

圖3 上行發送通道設計方案

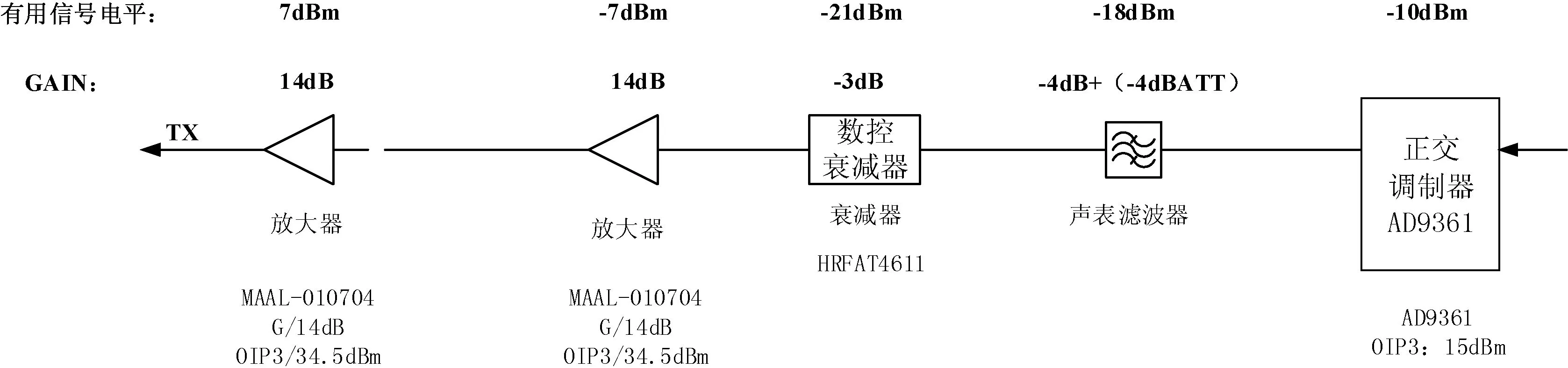

因為AD9361集成了小數N分頻鎖相環,IQ調制/解調等功能,因此其電路比下行接收通道簡潔得多。但是仍然不能忽視最大發送電平“+15 dBm”這一指標。首先,最大發送電平信號易干擾具有高靈敏度的下行小信號接收通道;其次,要滿足這么大的發送電平,必然需要高增益的發送器,處理不好,易產生自激。在本設計中上行發送通道采用三級級聯放大濾波結構,每級均用屏蔽罩蓋住,減少輻射和干擾。上行發送通道增益分配如圖4所示。

圖4 上行發送通道增益分配

4 結語

本文只給出了一路下行接收通道和一路上行通道的設計方案,但該方案的適用范圍不僅限于一收一發的應用。在實際應用中,采用本設計方案,在190 mm×140 mm的印制板上同時實現了3路下行通道和2路上行通道,并具有高速的FPGA,CPU數字信號處理電路。