IC工藝技術研究生教學創新實例設計研究

王秀宇 徐江濤 高志遠 聶凱明 高靜

摘 ?要:創新實踐教學對集成電路(IC)專業研究生人才培養極其重要。文章根據CMOS圖像傳感器像素與NMOS器件在結構上的相似性,通過科教融合設計了創新實例用于IC工藝技術課的研究生教學,取得了較好的效果。該教學改革一方面激發了學生的學習興趣、調動了他們自主學習該課的積極性,另一方面在創新實踐教學中加深了學生對該課基礎知識的理解,培養了他們的創新實踐能力。

關鍵詞:科教融合;IC工藝技術;研究生教學;創新實踐

中圖分類號:TN4;G643.2 文獻標識碼:A文章編號:2096-4706(2021)14-0182-04

Abstract: Innovative practice teaching is very important for the cultivation of graduate students majoring in integrated circuit (IC). According to the structural similarity between CMOS image sensor pixels and NMOS devices, this paper designs an innovative example through science and education integration, which is used in the graduate teaching of IC process technology course, and has achieved good results. On the one hand, the teaching reform has stimulated students’ interest in learning and mobilized their enthusiasm to study the course independently. On the other hand, it has deepened students’ understanding of the basic knowledge of the course and cultivated their innovative practice ability in innovative practice teaching.

Keywords: integration of science and education; IC process technology; postgraduate teaching; innovative practice

0 ?引 ?言

“新工科”建設行動路線(“天大行動”)明確指出:要大力發展大數據、智能制造和集成電路等新產業相關的新興工科專業和特色專業集群;培養造就一大批多樣化、創新型卓越工程科技人才,為我國產業發展和國際競爭提供智力和人才支撐[1];而研究生創新人才培養和教學改革是“新工科”建設的重要組成部分,也是“天大行動”的一個重要體現。本文針對集成電路(IC)專業研究生課程—IC工藝技術,從科教融合方面進行教學改革,通過教學質量提升以加強創新人才的培養。

IC是電子信息產品的核心和基石,沒有IC產業的支撐,信息化社會就失去了“根基”。因此,IC常被喻為電子整機設備的“心臟”、現代工業的“糧食”。IC制造工藝按摩爾定律快速發展,目前7 nm工藝已成熟并用于芯片生產。在臺積電(TSMC)和三星(Samsung)等先進IC制造公司宣布5 nm和3 nm工藝即將成熟之際,2021年5月IBM公司宣布,采用環繞柵極晶體管(GAA)技術造出全球第一顆2 nm制程芯片的實驗產品;在同樣的電力消耗下,其性能比7 nm工藝芯片高出45%,輸出同樣性能則功耗減少75%。由此可見,工藝技術節點減小對IC性能提高和發展具有重要的價值。IC制造行業被喻為高端制造的“皇冠明珠”,其技術代表著當今世界微細加工的最高水平,因此IC制造工藝是一個國家高端制造能力的綜合體現,是各國高科技國力競爭的戰略必爭制高點。

目前我國IC產業的14 nm工藝已量產,正研發7 nm工藝。與國際先進技術相比,我國IC制造工藝技術還較落后,其根本原因是核心技術“受制于人”,而解決這一問題離不開技術創新和人才培養。由于IC是知識密集型行業,對從業人員的學歷要求較高,因此在加大海外IC高層次人才引進的同時,本土IC專業研究生人才培養也極其重要,他們是推動IC產業發展的主力軍。當前IC工藝技術的研究生教學以專業基礎知識學習為主,雖然在課程中引入了一些當前最先進的IC制造工藝技術介紹(如10 nm以下CMOS器件結構及工藝),但與之相應的創新實踐教學仍是該課的薄弱環節,這顯然不利于“新工科”建設中研究生創新能力的培養。本文結合我們團隊CMOS圖像傳感器(CIS)方面的國家級科研項目(如國家重點研發計劃課題“低電壓高量子效率微光探測器及陣列(2019YFB2204301)”和“二維/三維兼容的圖像傳感器設計與芯片測試驗證(2019YFB2204302)”等),通過科教融合進行創新實例設計探索,使之適用于IC工藝技術研究生教學,以培養學生的創新實踐能力。

1 ?CMOS器件及在IC工藝技術課中的地位

由于CMOS器件在功耗和集成度等方面優于雙極型器件,在應用市場上占主導地位,因此IC工藝技術課中的器件介紹通常以CMOS器件為主。

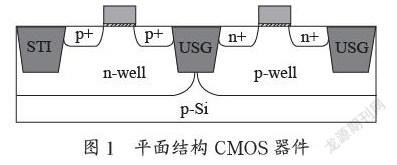

傳統的CMOS器件是平面(Planar)結構晶體管,如圖1所示,它由PMOS和NMOS管構成。IC芯片中包含大量的PMOS和NMOS管,其制備工藝常稱為CMOS工藝。當器件特征尺寸低于25 nm時,平面結構的P/NMOS器件面臨穩定性和可靠性問題,無法滿足IC應用要求。針對這一問題,鰭式結構場效應晶體管(FinFET)[2,3]改進了柵對MOS管溝道的控制,減小了小尺寸MOS器件的短溝道效應,降低了漏電流。2011年初英特爾公司(Intel)使用22 nm工藝首先推出了商業化FinFET[4],Intel Core i7-3770之后的22 nm處理器均采用了FinFET技術。但是當FinFET特征尺寸進一步降低(<7 nm),再次面臨穩定性和可靠性問題[5]。最近IBM公司推出了全球首創的2 nm芯片技術,該芯片通過環繞柵極晶體管結構(GAA)[6]的設計解決了小尺寸MOS器件穩定性和可靠性問題。

本課程選用Hong Xiao(蕭宏)編著的原版英文教材《Introduction to Semiconductor Manufacturing Technology》[7]。作者蕭宏曾作為高級制造工程師工作于摩托羅拉公司半導體公司,在奧斯汀社區大學講授過半導體制造技術,為IEEE會員和華美半導體協會終身會員,在IC制造工藝方面具有較高的學術水平和豐富的實踐經驗。該書是一本關于半導體工藝技術的優秀教材,被全球多所著名大學微電子專業選為教材。與本科生所用教材(如硅集成電路工藝基礎)不同的是,該書并不強調很深的理論和數學知識,而是重點關注半導體關鍵加工技術概念的理解,因此比較適合作為研究生教材。該書繁體中文譯本被臺積電(TSMC)作為員工必讀培訓教材。

基于研究生教學的IC工藝技術授課內容主要由單項工藝、工藝集成和先進CMOS工藝三部分組成[7]。此外,在授課時還將行業最新研究進展和行業動態引入IC工藝技術課中(如FinFET)以及邀請行業專家作報告,以培養學生國際化視野。該課中的先進CMOS工藝體現為新材料(如SOI襯底、銅互聯和高/低k介質等)和新工藝(如大馬士革工藝和介質工藝等),器件結構仍為平面結構。但在課程學習后,由學生利用所學知識進行的創新實踐較少,存在人才培養與創新實踐脫節的問題。針對這一問題,本文基于科教融合設計了創新實例用于研究生教學,彌補了IC工藝技術課創新實踐教學的不足。

2 ?基于科教融合CIS創新實例設計

CIS是攝像頭模組的核心器件,目前在汽車、安防監控和智能手機等方面有著廣泛的應用[8]。由于CIS是采用標準CMOS工藝制備,與IC工藝技術課關聯較密切,因此將與之有關的創新實例用于研究生教學,不僅能加深學生對所學知識的理解,同時還有助于培養學生的創新能力。

2.1 ?創新實例1—PD結構CIS光敏單元設計

由于CIS能利用標準CMOS工藝,在一個芯片上集成一個相機系統的全部電路(包括像素、讀出放大器、模數轉換器、數字儲存器、驅動控制器和數字信號處理器等)而不只是一個圖像傳感器,因此CIS常被稱為芯片上相機[9],它在小型化和低功耗等方面是其他圖像傳感器所無法比擬的。目前CIS常采用4T-APS有源像素結構(圖2),以便對光敏單元和像素電路進行靈活設計[10]。圖2中4T-APS像素具有如下特點:(1)每個像素由4個晶體管構成,分別為傳輸管(MTG)、復位管(MRST)、源跟隨器(MSF)和選通管(MSEL);(2)光敏單元為光電二極管(PD)結構,負責收集光生電荷;(3)浮空擴散區FD(floating diffusion)為電荷-電壓轉換節點;(4)PD與FD被傳輸管MTG隔開,其在結構上與NMOS管相似(圖2),這里PD與FD分別相當于NMOS管的源區和漏區;(5)不同的是,NMOS管的源區和漏區在結構上是對稱的,而PD與FD基于光電子收集和光電信號轉換的性能要求,在結構上是不對稱的;在設計上通常PD面積大(獲得靈敏度高),FD面積小(獲得高轉換增益)。通過這一結構差異性對比,使學生領悟到在用所學知識時解決實際工程問題時,需根據性能要求靈活變通。

本文以圖2中4T-APS為研究對象,進行創新實例設計。4T-APS有源像素的性能指標主要有量子效率、靈敏度、轉換增益、滿阱容量和動態范圍等,影響這些性能參數的因素主要有PD/FD尺寸、光照強度、摻雜濃度和結深等。可用Sentaurus TCAD軟件對設計的像素進行仿真,獲得相關性能參數。該創新實例與NMOS器件在結構上存在著關聯性,易于理解,并能用仿真軟件評價自己的設計,因此是可行的。由于圖2中PD與FD在結構上與NMOS管的源區和漏區有差別,因此學生在對這一創新實例進行練習時有利于培養創新思維。

2.2 ?創新實例2—PPD結構CIS光敏單元設計

在圖2基礎上對PD進行改進,如圖3所示。在PD上方進行p+摻雜(稱為p+鉗位層),形成鉗位光電二極管(PPD)[10]。該p+鉗位層設計有助于降低Si-SiO2界面缺陷引起的閃爍噪聲(1/f噪聲)。這里p+鉗位層屬于淺結離子注入,在進行工藝設計時需考慮是采用B+離子還是采用BF2+離子,通過創新實踐練習有助于加深學生對所學IC工藝知識的理解。

在創新實踐教學中,基于相同的工藝參數可讓學生對實例1和實例2的像素仿真結果進行對比分析,理解p+鉗位層的作用及性能差異性的原因;在進行機理分析時,需用到半導體物理的相關知識。由于設計和仿真工作量較大,在對比分析研究中,可以團隊的形式協作進行;這一方面有利于得出正確的結論,另一方面還能培養團隊協作精神。圖4是在實際教學中,一些學生對CIS像素仿真的結果,實現了創新實踐的預期目標。

在實際教學引入創新實例后,發現學生能更加積極主動地學習IC工藝技術課;不僅主動查資料、在課堂上認真聽講,而且課后問問題的同學較以前顯著增多,這表明學生在學習本課時,結合創新實例認真思考了。

2.3 ?基于創新實例科學思維和批判性思維的培養

上述創新實例練習中,像素設計(PD/FD尺寸)、工藝參數(摻雜濃度和結深等)和工作條件(電壓、光照強度)與CIS性能(滿阱容量、靈敏度和轉換增益等)密切相關。例如,在PD設計時需考慮光照強度、曝光時間和阱容量之間的關系;對于高低、光強的寬動態光照環境,PD面積及摻雜需折中考慮;PD摻雜濃度不能過高,否則復位時在≤3.3 V低壓下不易全耗盡,這些在設計時需辯證性思考。上述創新實例涉及半導體物理、光學和IC工藝等相關知識,要求在器件和工藝設計中能運用科學思維和批判性思維進行綜合考慮,以兼顧各種限制條件;只有這樣,在創新實踐時才能根據工程應用條件進行合理的分析和設計。總之,在IC工藝技術課中結合科研項目引入上述創新實例,有助于培養研究生的科學思維和批判性思維以及靈活應變能力。

2.4 ?基于創新實例教學方法的改變

由于在授課過程中引入了創新實例,因此授課方法須做出相應的改變。對于基礎知識,要求學生先按教材課下自學,然后在課堂上通過提問檢查自學效果、討論存在的問題,并進行學習總結。由于本科階段已進行IC工藝原理的學習,具有一定的基礎,因此研究生階段自學英文原版教材上的IC工藝技術基礎知識,是可行的。對于英文教材中有難度的知識點(如工藝集成),由老師引導完成,學生通過查資料、獨立思考和相互討論,掌握相關知識。通過創新實例中CIS像素與NMOS器件在結構上的相似性,引導學生從器件結構和制備工藝等方面進行比較、思考,激發學生的學心興趣。教學實踐表明,在IC工藝技術教學中引入創新實例,不僅能使學生從被動聽課轉變為主動思考學習,同時在創新實踐中還加深了學生對所學專業知識的理解,提高了學習效果。

3 ?結 ?論

本文依托我們研究團隊在CIS方面的科研項目,通過科教融合將創新實例引入研究生的IC工藝技術課,以提高課程質量。所設計的創新實例與NMOS器件在結構上相似,相關性強,并能通過Sentaurus TCAD軟件對設計的器件性能進行仿真驗證,因此是可行的。教學實踐表明,上述創新實例在實際教學中受到學生的歡迎,激發了學生學習的積極性。總之,基于科教融合在教學中引合適的創新實例,不僅有助于學生掌握扎實的專業基礎知識,同時還能培養他們的創新實踐能力。

參考文獻:

[1] 高教司.“新工科”建設行動路線(“天大行動”) [EB/OL].(2017-04-08).http://www.moe.gov.cn/s78/A08/moe_745/201704/t20170412_302427.html.

[2] KATARIA S,SANDHU P,BILANDI A,et al. STEALTH LIPOSOMES:A REVIEW [J].International Journal of Research in Ayurveda & Pharmacy,2011,2(5):35-36.

[3] JURCZAK M,COLLAERT N,VELOSO A,et al. Review of FINFET technology [C]//2009 IEEE International SOI Conference. Foster City:IEEE,2009 :1-4.

[4] LEE H J,RAMI S,RAVIKUMAR S,et al. Intel 22nm FinFET (22FFL) Process Technology for RF and mm Wave Applications and Circuit Design Optimization for FinFET Technology [C]//2018 IEEE International Electron Devices Meeting (IEDM).IEEE,2018:316-319.

[5] PAL R S,SHARMA S,DASGUPTA S. Recent trend of FinFET devices and its challenges:A review [C]//2017 Conference on Emerging Devices and Smart Systems (ICEDSS),2017:150-154.

[6] NARENDAR V,SHREY,REDDY N K. Performance Enhancement of Multi-Gate MOSFETs Using Gate Dielectric Engineering [C]//2018 International Conference on Computing,Power and Communication Technologies(GUCON),2018:924-928.

[7] XIAO H. Introduction to Semiconductor Manufacturing Technology [M].Spie Press,2012.

[8] BIGAS M,CABRUJA E,FOREST J,et al. Review of CMOS image sensors [J].Microelectronics Journal,2005,37(5):433-451.

[9] FOSSUM E R. CMOS image sensors:electronic camera-on-a-chip [J].IEEE Transactions on Electron Devices,1997,44(10):1689-1698.

[10] FOSSUM E R,HONDONGWA D B. A Review of the Pinned Photodiode for CCD and CMOS Image Sensors [J].IEEE Journal of the Electron Devices Society,2014,2(3):33-43.

作者簡介:王秀宇(1978—),男,漢族,安徽阜陽人,副教授,博士,研究方向:微電子與固體電子教學科研。