分形塔分抗逼近電路

——標度拓展與優化設計原理

張月榮, 袁 曉, 郭釗汝

(1.四川大學電子信息學院, 成都 610064; 2.新疆農業大學計算機與信息工程學院, 新疆 830052)

1 引 言

分數階微積分已逐步發展為數學分析中的一個重要領域[1]. 近年來,隨著分數階微積分研究的深入,分數階線性系統,分數階混沌系統,分數階流變模型,分數階憶阻器[2]等相關電路模型的研究與應用越來越廣泛[3]. 分數階電路與系統更能刻畫實際的物理工程現象. 分數階電路與系統中的核心電路元件就是分抗(元)[4]. 理想分抗(元)的阻抗(或導納)函數可表示為

I(μ)(s)=F(μ)·sμ,(0<|μ|<1),s∈

(1)

式中,s為拉普拉斯變量,也稱頻率運算變量;μ表示分抗元的運算階,當運算階取值為分數時,稱sμ為分數階算子;F(μ)為分抗元的集總特征參量,稱為分抗值(簡稱分抗,fractance). 為便于數學分析而又不失一般性,往往將分抗元的阻抗函數進行歸一化處理. 定義歸一化運算變量

(2)

式中,τ=RC,表示時間常數; Ωτ為特征頻率值. 歸一化后分抗元的阻抗函數為

(3)

鑒于實際因素和現有的工藝制作手段,工程上主要考慮由整數階電路元件(電阻,電容,電感)構建具有分數階運算性能的無源網絡來近似實現分抗元的運算功能[5],這類電路模型被稱為分抗逼近電路. 現有的許多經典無源分抗逼近電路(例如Oldham分形鏈分抗,Sierociuk分形鏈分抗,Carlson分形格分抗等)都能在特定的頻率范圍或條件下實現分數階運算性能. 這種在特定頻率范圍或一定條件下逼近理想分抗的過程被稱為非理想分抗逼近過程.

文獻[6]在對比分析Oldham分形鏈分抗與Liu-Kaplan分形鏈分抗的基礎上,發現描述Liu-Kaplan分形鏈分抗的代數迭代方程可由描述Oldham分形鏈分抗的代數迭代方程標度化得到. 由此,袁曉提出標度拓展理論. 標度拓展可將原負半階逼近的分抗拓展為任意階分抗逼近,降低電路設計成本. 另外,逼近性能的提升也可由對原電路的優化實現[7-8]. 例如改進Oldham I型分形鏈分抗[4],對比原電路,改變第一個電阻的取值能夠極大提高逼近效益. 經典的分抗大多為容性分抗(運算階為負),感性分抗(運算階為正)具有同等應用價值. 然而電感自身具有不適宜集成的特性,尤其單片集成電路不能制作電感,因此感性分抗極少被研究及應用. 如何構造感性分抗逼近電路也是分抗實際應用時急需解決的問題[9].

本文在分析負半階B型分形塔分抗電路的基礎上,根據標度拓展理論,分析原電路標度拓展后的分數階運算性能,得到具有任意分數算子的標度分形塔分抗逼近電路. 并針對標度拓展后的電路在一定頻段處逼近失真的問題,探尋標度分形塔分抗的優化原理及方法. 分析標度拓展后電路的振蕩現象. 提出由電阻,電容和運算放大器構建的有源電路網絡實現感性分抗(0<μ<2)的方法. 通過理論分析與仿真實驗,證明塔形分抗標度拓展的運算有效性和電路優化方法的可行性.

2 標度拓展——任意階標度分形塔分抗

2.1 B型分形塔分抗逼近電路及其標度拓展

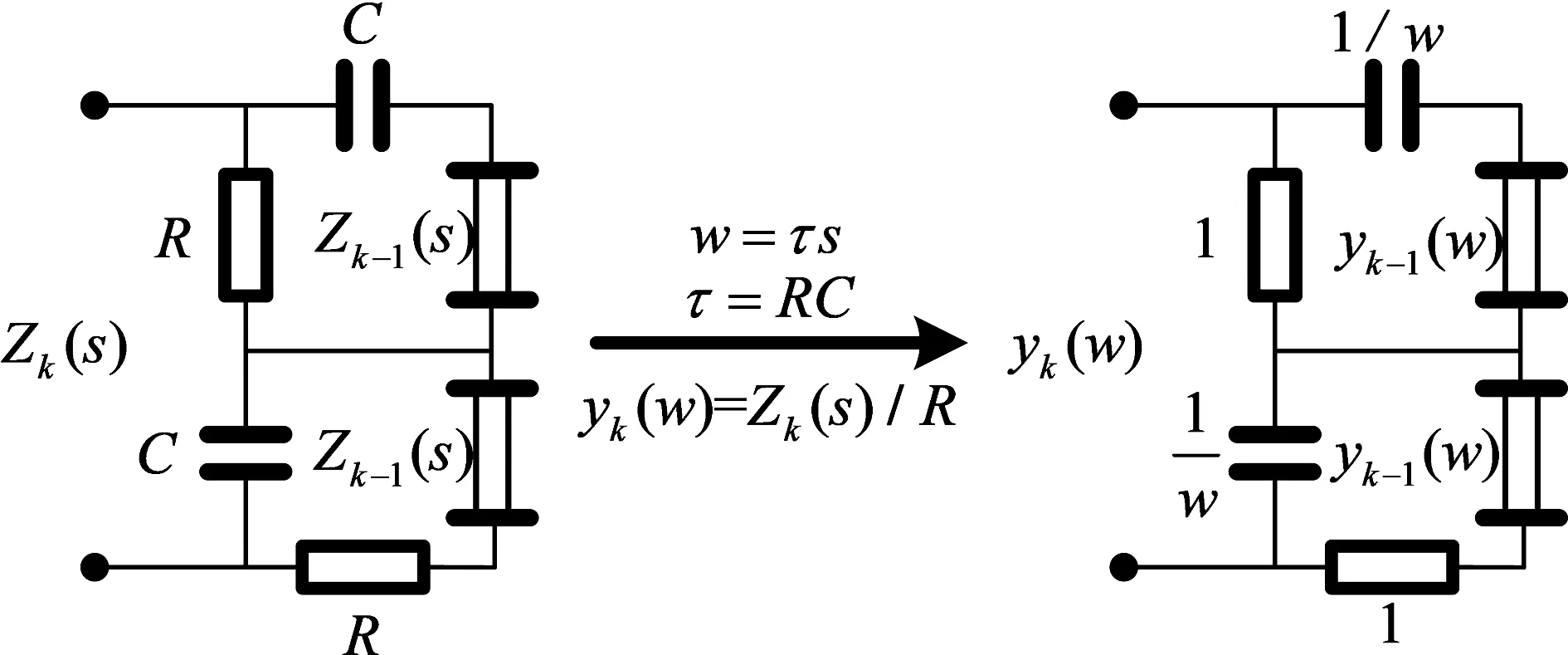

文獻[5]提出了一種不同于經典Oldham分形鏈分抗和Carlson分形格分抗的負半階分抗逼近電路——B型分形塔分抗逼近電路. 該RC分抗逼近電路是實現負半階積分算子的理想逼近,其迭代電路原理圖及歸一化迭代電路如圖1.

B型分形塔分抗迭代算法公式為

(4)

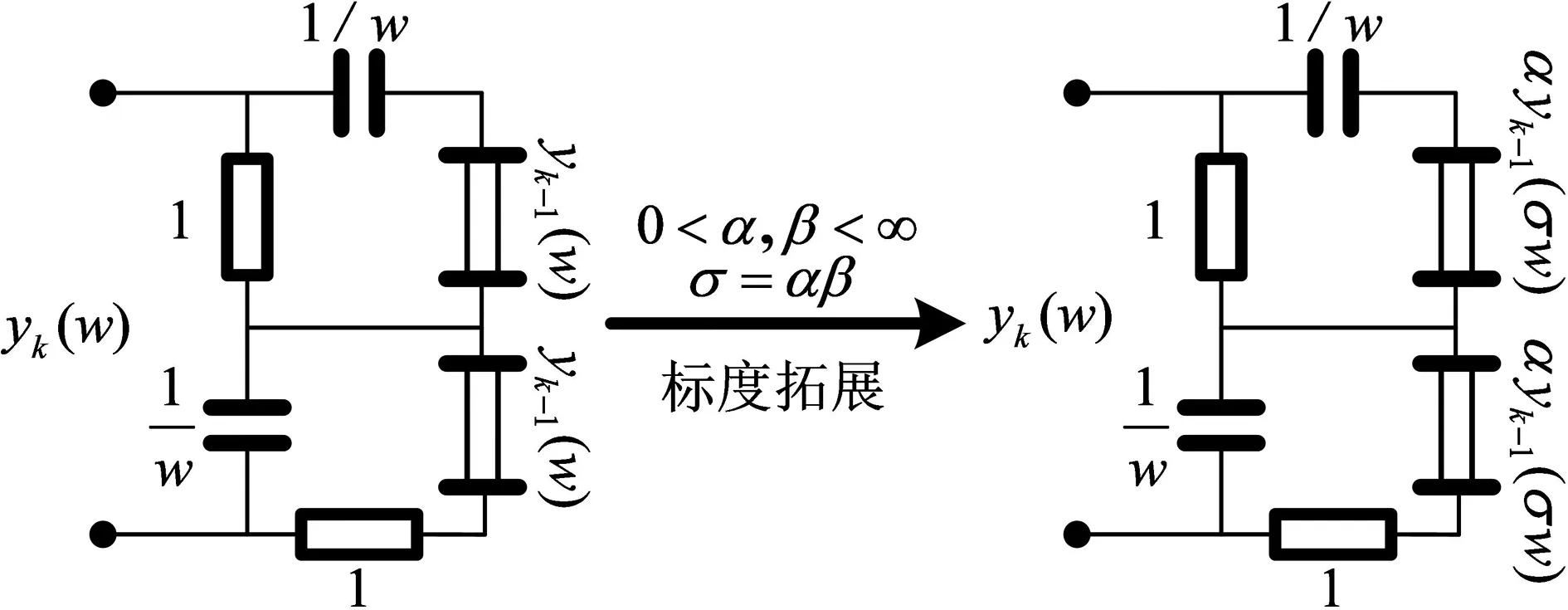

式中,k表示電路的迭代次數,也是電路級數. 正如Oldham分形鏈分抗與Liu-Kaplan分形鏈分抗,標度拓展后,描述半階算子的代數迭代方程可轉化為描述任意階算子的非正則標度方程.

代數迭代方程非正則標度方程

F(α±1y(σ±1w))

(5)

式(5)中的α,β稱為電路的標度特征參量,取正實數.σ=αβ稱為標度因子. 當1<σ<∞時為正比標度拓展,簡稱正比拓展;當0<σ<1時為反比標度拓展,簡稱反比拓展. 根據拓展理論,B型分形塔分抗標度拓展后,理論上可以實現任意階分數算子的有理逼近. B型分形塔分抗歸一化迭代電路及其標度拓展后的迭代電路如圖2,對應的非正則標度方程如式(6).

圖1 B型分形塔分抗迭代電路與歸一化迭代電路Fig.1 B-type fractal-pyramid fractance iterating circuit and normalized iterating circuit

圖2 B型分形塔分抗標度拓展電路圖Fig.2 Scaling extension circuit diagram of B-type fractal pyramid fractance approximation circuit

圖2在正文沒有描述,請先描述再有圖出現.

(6)

非正則標度方程(6)是一種雙重標度方程. 該代數迭代方程完全表征和描述了標度分形塔分抗逼近電路的運算性能和電氣響應特征[10],標度分形塔分抗逼近電路的結構特征蘊含在該雙重標度方程中. 該電路的極限阻抗必定為式(6)中方程的一個真實解. 求解該方程對分析分抗電路特征具有重要作用[11].

2.2 分形塔分抗的運算有效性及頻域特征函數

yk(j·10?)=Ak(?)·ejθk(?),k∈,?∈

(7)

式中幅頻特征函數:

Ak(?)=|yk(j·10?)|

(8a)

或Λk(?)=lg(Ak(?)),?∈

(8b)

相頻特征函數

θk(?)=arg {yk(j·10?)},?∈

(9)

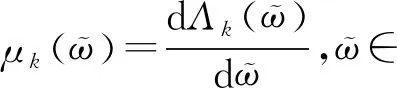

階頻特征函數

(10)

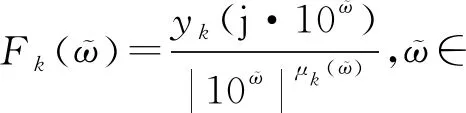

為便于在頻域定量分析分抗逼近電路的集總特征值F(μ),文獻[12]提出F特征函數:

(11)

幅頻特征函數和相頻特征函數表征了分抗逼近電路阻抗函數的頻域特征. 階頻特征和相頻特征可完全表征分抗逼近電路的運算特征. 對于一個給定的分數階系統,首先應該考慮它的運算階[9]. 階頻特征是幅頻特征的微分,因此階頻特征包含了幅頻特征的信息. F特征描述分抗集總特征參量與頻率?的依存關系,在分抗逼近電路具體設計及實際應用中具有重要作用.

運算有效性[4]是指給定的分抗逼近電路,其極限阻抗,即描述其有理逼近過程的非正則標度方程

y(w)=F(αy(σw))

(12)

的解y(w)中,是否含有代數因子wμ(0<|μ|<1)也即分數算子. 標度分形塔分抗逼近電路顯然是物理可實現的. 運算有效性的判定是研究分抗有理逼近問題或研究標度方程描述的過程或系統的核心問題之一. 判定標度分形塔分抗的運算有效性需求解方程(6),該非正則標度方程的解析求解[13]具有一定的挑戰性,還不知道如何實現. 因此,可考慮近似求解法.

2.3 近似求解與數值求解

根據近似求解結果可從理論上判斷標度拓展后的B型標度分形塔分抗的運算有效性[14]. 數值求解[15]則可驗證近似求解的正確性,并利于直觀分析運算性能和逼近性能. 當電路迭代次數k→∞,在較低頻段時|w|→0,電路中的電容容抗1/w→∞,此時電容近似開路狀態. 根據歸一化迭代電路,此時的歸一化阻抗函數

(13)

在較高頻段時,電路中的電容容抗1/w→0,此時電容近似為短路狀態. 由歸一化迭代電路近似求解的阻抗函數為:

(14)

正則標度方程(13),(14)有近似解析解——Liu氏粗解

(15)

近似解(15)表明拓展后,標度分形塔分抗理論上可實現任意負分數階算子的有理逼近. 運算階只與α,β有關.

分抗逼近電路阻抗函數的數值求解常用算法有三種:傳輸參量矩陣法[10],系數矢量迭代法[16]和標度矩陣迭代法[17]. 鑒于標度分形塔分抗電路結構特點,傳輸參量矩陣法不易于求解,因此考慮系數矢量迭代法或標度矩陣迭代法[18].不同初始阻抗下,兩種算法的初始迭代參數如表1.

表1 初始阻抗對應的初始迭代參數

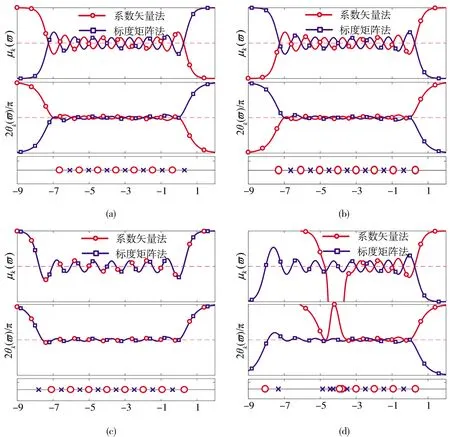

初始阻抗取值會影響標度分形塔分抗的零極點個數和分布情況,進而影響運算特征曲線的形狀[19]. 初始阻抗為開路和短路時,兩種算法求解的正比拓展時負半階標度分形塔分抗運算特征曲線關于直線μLiu=-1/2對稱(圖3(a)和(b)). 當y0(w)=1/w時,由系數矢量迭代法求解的運算特征曲線偏離真實值(圖3(d)),此時求解的零極點分布極不均勻.y0(w)=1時,兩種算法求解的運算特征曲線幾乎重合(圖3(c)).

圖3 正比拓展時不同初始阻抗下運算特征和零極點分布(μLiu=-0.5,k=12,σ=5σ=10)

對比分析發現,系數矢量迭代法計算速度較快[15],當電路迭代次數k的取值較大時,標度矩陣迭代法將不太適用. 且表1中標度矩陣迭代法的初始阻抗迭代參數與電路迭代次數k有關,當迭代次數變化時,需要對初始阻抗中的σk進行指數調整[19]. 考慮到標度調整,優先選用系數矢量迭代法. 取y0(w)=1,由系數矢量迭代法求解拓展前后的分抗運算特征曲線如圖4.

數值仿真結果表明,標度拓展前B型分形塔分抗是全頻有效的半階積分算子的理想逼近. 標度拓展后,該分抗可實現任意階負分數算子的非理想逼近.

3 標度分形塔分抗的優化

很多經典的半階分形分抗標度拓展后都能實現任意階分數算子的逼近. 例如標度分形格分抗[1],標度分形梯分抗[2-3],標度分形串分抗[9],標度分形鏈分抗類[16]等. 這些標度拓展后分抗的逼近效果都有待優化.圖4(b)中的運算特征曲線表明,正比拓展較高頻段(反比拓展較低頻段)時,逼近效率不甚理想. 因此,通過電路優化[4]改善分抗逼近性能顯得尤為必要[5]. 例如改進Oldham I型分形鏈分抗,電路上的微小改進便可獲得逼近性能的極大改善.

3.1 電路優化理論分析

正比拓展時,隨著迭代次數k的增加,逼近帶寬向低頻段延伸. 且頻率取值越小,逼近性能越好. 反比拓展時,隨迭代次數的增加,逼近帶寬向高頻段延伸. 頻率取值越大,逼近性能越好. 但兩種拓展情況下在w=1(頻率指數?=0)附近的逼近效果都有待優化. 根據不同運算階下運算特征曲線的形狀不同,結合運算階μLiu及不同頻段內電阻和電容的電學特性,分正,反比拓展兩個方面理論分析標度分形塔分抗逼近電路的優化原理.

正比拓展(1<α,β,σ<∞)逼近頻段向低頻延伸. 當-0.5<μLiu<0時,在逼近頻帶的較高頻段,運算特征曲線向μLiu=-0.5方向偏移,偏向電容的運算特征(電容的運算階為-1階),優化補償元件選用電阻(電阻的運算階為0階). 當-1<μLiu<-0.5時,在較高頻段運算特征曲線向μLiu=-0.5方向偏移,偏向電阻的運算特征,優化補償元件選擇電容. 考慮較高頻段時串聯電容的容抗幾乎可忽略,故選用并聯電容,串聯電阻的優化補償網絡.

反比拓展(0<α,β,σ<1)逼近頻段向高頻延伸. 當-0.5<μLiu<0時,在較低頻段運算特征曲線向μLiu=-0.5方向偏移,即偏向電容的運算特征,優化元件選用電阻. 當-1<μLiu<-0.5時,在較低頻段運算特征曲線向μLiu=-0.5方向偏移,偏向電阻的運算特征,優化元件選擇電容. 而較低頻段時并聯電容的容抗幾乎可忽略,故采用串聯電容,并聯電阻的優化補償網絡.

3.2 優化電路及優化頻域曲線

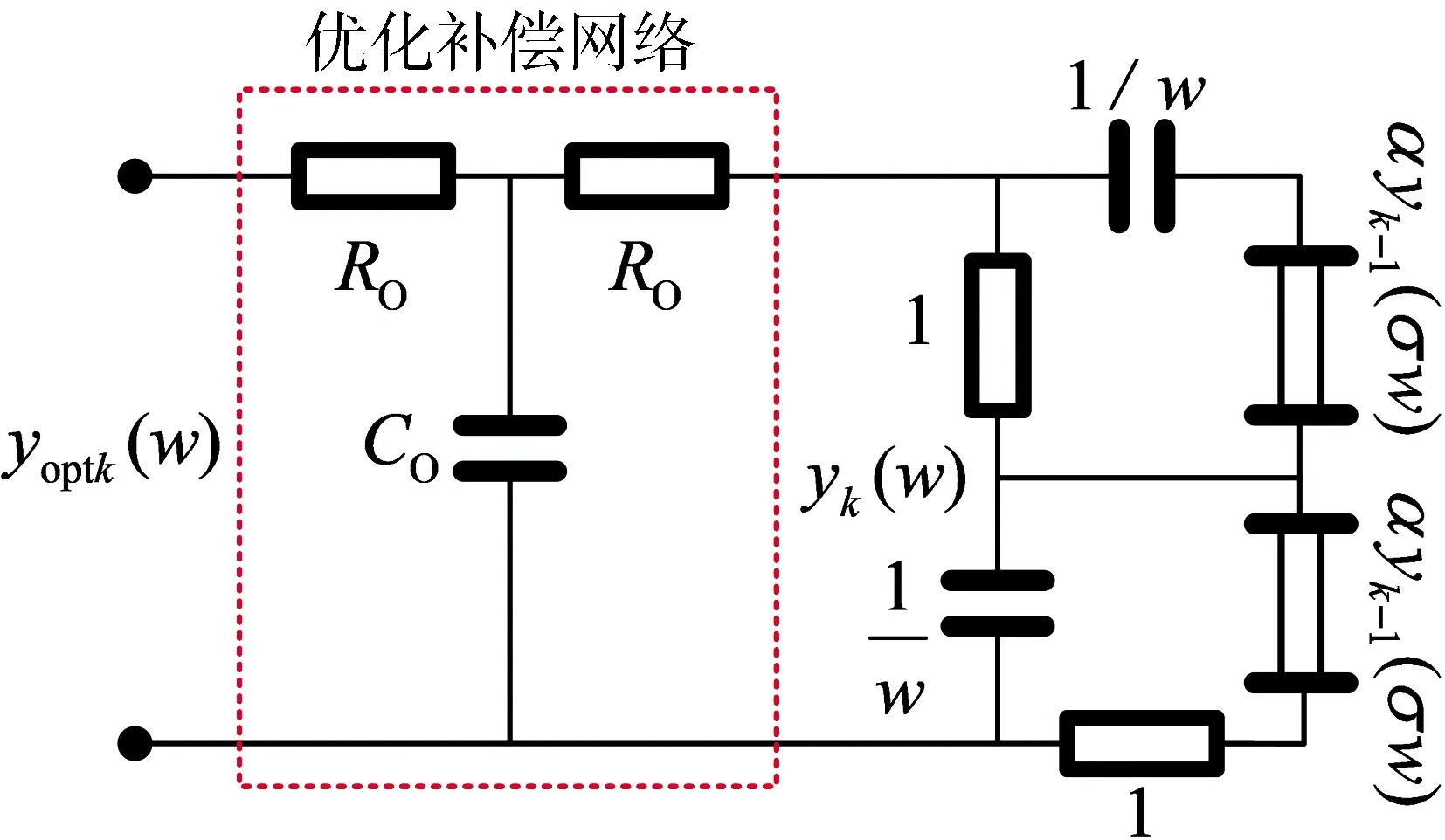

選擇對稱阻容T型節對原電路進行補償(如圖5所示),正比拓展時優化電路的補償元件參數

(16)

反比拓展時電路優化原理圖如圖6,優化元件參數

(17)

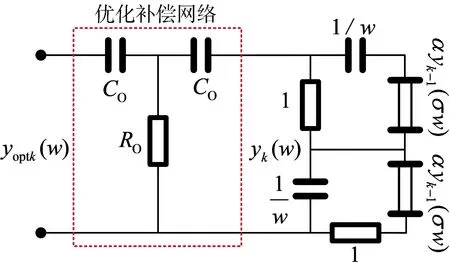

取初始阻抗y0(w)=1,正比拓展時優化后的運算特征曲線如圖7,其中黑色曲線為標度分形塔原型電路的運算特征曲線,紅色為電路優化后的運算特征曲線.反比拓展時優化電路具有相同的頻域優化效果.

圖 5 正比拓展優化原理圖Fig.5 Optimization schematic diagram of direct proportion extension

圖6 反比拓展優化原理圖Fig.6 Optimization schematic diagram of inverse proportion extension

4 優化標度分形塔分抗的頻域特征及逼近性能

對比分析圖7, 優化后的電路相比原型電路逼近理想分抗元的效果更好[6]. 尤其是運算階μLiu≠-0.5時,優化后的逼近性能得到顯著提升.

4.1 頻域特征——運算振蕩現象

電路的優化并無法消除或減弱逼近頻帶內的振蕩現象,振蕩現象是標度分形塔分抗所固有的[7]. 在工程應用中,必須考慮頻域的振蕩現象帶來的逼近誤差,因此需定性與定量分析標度分形塔分抗的運算振蕩現象[8].

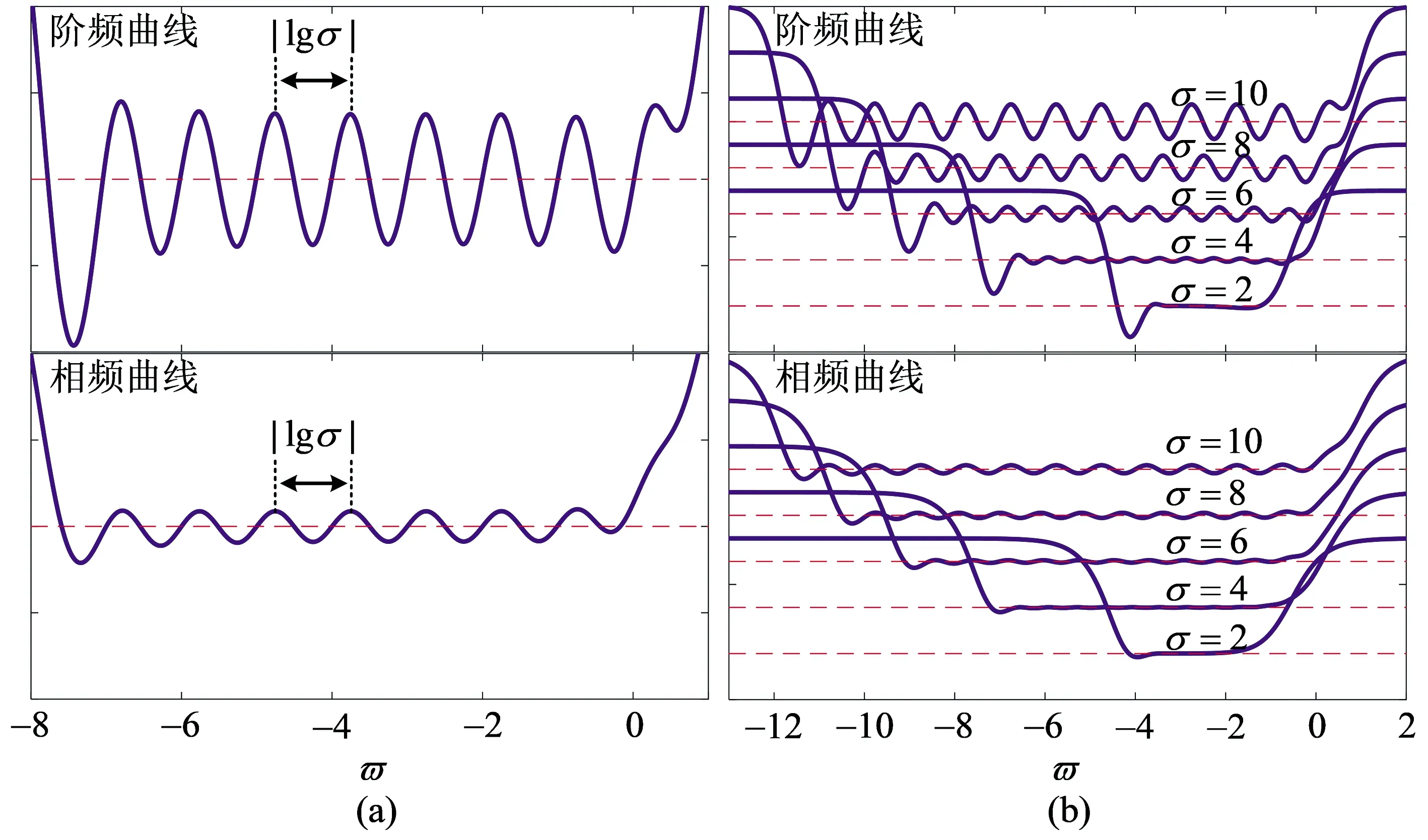

以正比拓展為例,在有效逼近頻帶范圍內(如圖8所示),優化前后頻域振蕩波形具有固定振蕩周期W=|lgσ|.

圖7 正比拓展優化前后運算特征曲線對比圖(k=12,σ=5)

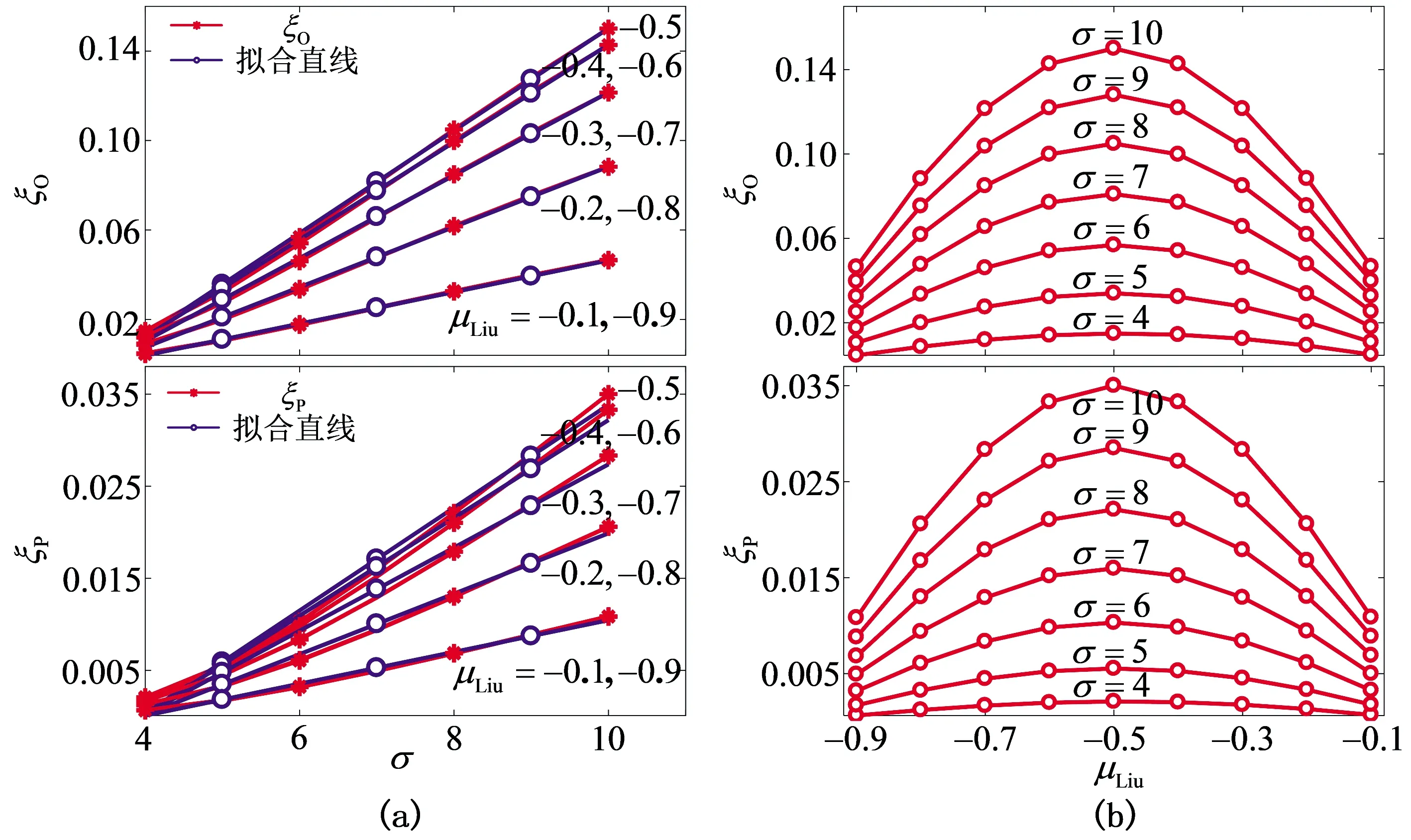

隨著標度因子的增加,逼近頻帶內波形振蕩幅度也在增加(圖8(b)). 標度因子σ取定值時振蕩波形的幅度ξ與運算階μLiu有關(圖4(b)).圖9分別展示了頻域振蕩波形幅度ξ與標度因子σ和運算階μLiu之間的關系曲線.

運算階μLiu一定時,振蕩波形的幅度ξ與標度因子σ近似為線性關系(圖9(a)). 且運算階μLiu為(-1<μLiu<0)與(-1-μLiu)時運算特征曲線的振蕩幅度曲線幾乎重合. 階頻特征曲線與相頻特征曲線的振蕩幅度的擬合直線函數表達式為

ξO(μLiu,σ)=KO(μLiu)·σ+bO(μLiu)

(18a)

ξP(μLiu,σ)=KP(μLiu)·σ+bP(μLiu)

(18b)

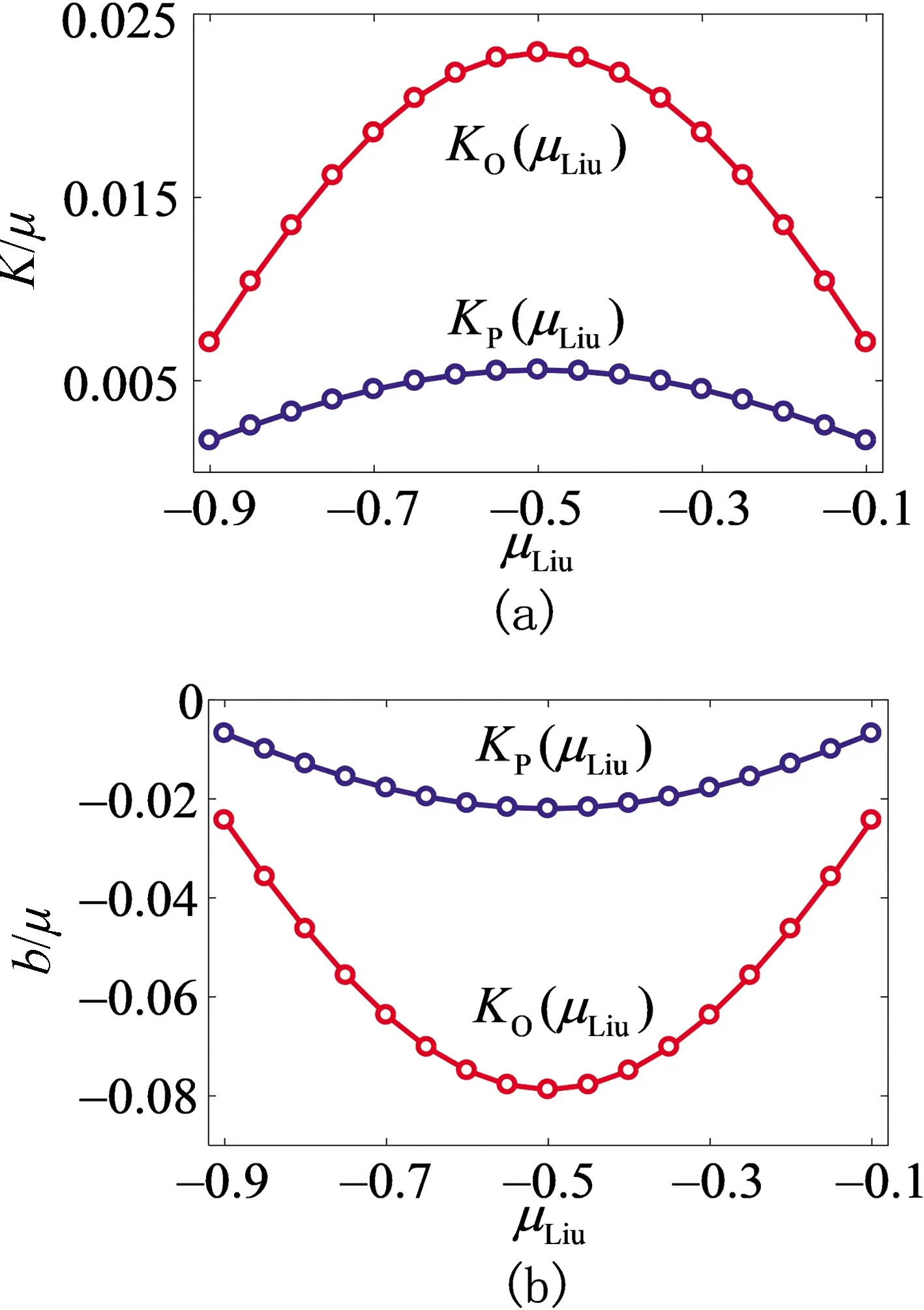

式中,K(μLiu)為擬合直線的斜率;b(μLiu)為擬合直線與縱軸的交點. 擬合直線函數的斜率KO(μLiu),KP(μLiu),截距bO(μLiu),bP(μLiu)與運算階μLiu的函數關系擬合式為

KO(μLiu)=0.0228·sin(π(μLiu-1))

(19a)

bO(μLiu)=-0.0787·sin(π(μLiu-1))

(19b)

KP(μLiu)=0.0055·sin(π(μLiu-1))

(19c)

bP(μLiu)=-0.0220·sin(π(μLiu-1))

(19d)

函數表達式中參數的取值由數值擬合求得. 擬合函數中參數的圖像如圖10.

圖8 優化標度分形塔分抗的運算特征曲線的振蕩現象

圖9 振蕩幅度與標度因子和運算階的關系

當標度因子一定時,運算階為μLiu(-1<μLiu<0)時振蕩幅度與-1-μLiu時相等(圖9(b)). 振蕩幅度關于μLiu=-0.5對稱分布. 已知頻域振蕩曲線的振蕩周期W和振蕩幅度(18),階頻振蕩曲線與相頻振蕩振蕩曲線可表示為

μk(?)≈μLiu+ξO(μLiu,σ)·

(20)

(21)

式中,初相位φO(μLiu,σ),φP(μLiu,σ)的取值可由數值仿真精確求解. 當標度因子σ的取值小于4時,負半階標度分形塔分抗的階頻特征曲線的振蕩幅度小于0.012 8,相頻特征曲線的振蕩幅度小于3.363 5×10-4. 階頻和相頻特征曲線在一個周期內的積分為

(22)

(23)

運算特征曲線的積分特性表明,盡管式(15)是阻抗函數在特定極限頻率條件下的近似取值,但該計算結果同時表示逼近頻帶內運算階的平均值[4].

圖10 振蕩幅度函數表達式中的參數

(a) slopeK;(b) interceptb

在研究分抗逼近性能的相關問題時,通常需要考慮相對誤差函數和4種逼近精度取值[4].

階頻相對誤差函數:

(24)

相頻相對誤差函數:

(25)

逼近精度ri:

r0=1%;r1=5%;r2=10%;r3=20%

(26)

優化前后的電路復雜度與迭代次數的關系分別為

ζσ[k]=2k+1-2

(27a)

ζσ-O[k]=2k+1-2+2=2k+1

(27b)

μLiu=-0.5時,由圖7和圖8可得標度分形塔分抗優化前后的逼近帶寬指數為

πσ[k]=πσ-O[k]≈(k-1)·|lgσ|

(28)

由此可求出優化前后的逼近效益——逼近帶寬指數與電路復雜度之比

(29a)

(29b)

式(29)表明當k取值較大時,負半階標度分形塔分抗優化前后的逼近效益近似相等. 因為當μLiu=-0.5時,標度分形塔分抗的運算特征曲線能夠較好地逼近理想分抗.μLiu≠-0.5時,該分抗逼近電路有待優化.

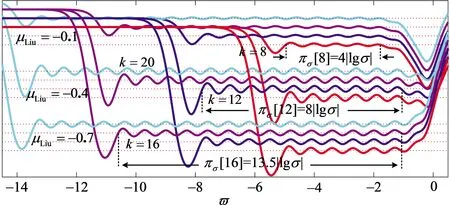

μLiu≠-0.5時,由圖4(b)可知,優化前的逼近帶寬指數為

πσ[k]≈[k-κ(μLiu)]·|lgσ|

(30)

κ(μLiu)是由μLiu確定的正實數. 優化后,以正比拓展不同運算階μLiu下的階頻特征曲線為例,根據圖11可知逼近帶寬指數.

πσ-O[k]≥(k-4)·|lgσ|

(31)

圖11 正比拓展時階頻曲線的逼近帶寬指數:σ=5Fig.11 The approximate frequency bandwidth exponent of order-frequency curves in direct proportion extension:σ=5

此時求出的優化前后標度分形塔分抗的逼近效益為

(32a)

(32b)

顯然κ(μLiu)>4,即μLiu≠-0.5時,優化后的標度分形塔分抗逼近效益值明顯大于優化前.

5 優化標度分形塔分抗電路的實現與運算階擴展

5.1 電路設計與仿真

當標度因子σ一定時,運算階為μLiu(-0.5<μLiu<0)時運算特征曲線的振蕩幅度與運算階為-1-μLiu時的相同(圖9(b)). 當-0.5<μLiu<0時,振蕩幅度隨運算階μLiu的增大而減小. 因此,可先分析-0.5<μLiu<0的情形.

在實際的工程應用中,往往需要在指定頻段內運算有效的分抗元[1]. 對于給定的逼近帶寬,若要降低分抗的電路復雜度,減少電路規模和設計成本,必須考慮合適的標度特征參量取值[2]. 尤其在給定逼近精度的條件下,標度因子σ太大將無法滿足實際需求. 由式(20), 式(21), 式(24) 和式(25)知,標度因子的取值必須滿足條件.

(33a)

(33b)

該不等式可由式(34)等價變換得到.

(34)

當-0.5<μLiu<0時,根據式(15)、式(33),可求出不同逼近精度下給定運算階時,標度特征參量對數lgαO,lgαP的最大取值. 數值擬合得到的函數關系為

r0:lgαO≈-0.6536·μLiu-0.0291,

lgαP≈-0.9213·μLiu-0.0766

(35a)

r1:lgαO≈-0.9456·μLiu-0.0939,

lgαP≈-1.4314·μLiu-0.1646

(35b)

r2:lgαO≈-1.1599·μLiu-0.1328,

lgαP≈-1.7100·μLiu-0.1958

(35c)

r3:lgαO≈-1.4156·μLiu-0.1702,

lgαP≈-2.0027·μLiu-0.2174

(35d)

當-1<μLiu<-0.5時,α的取值同樣可由式(35)確定,此時(35)式中的μLiu需替換為-1-μLiu. 優化標度分形塔分抗逼近電路的應用設計步驟如下.

(1) 由工程需求選擇運算階μLiu.

(2) 根據實際問題中逼近精度要求,由式(35)計算標度特征參量α;或根據振蕩幅度要求,由式(33)計算標度因子σ,然后由式(15)求解標度特征參量α,β.

(3) 由工程應用中工作頻段要求,計算逼近帶寬. 根據公式(31)計算優化標度分形塔分抗的電路級數k.

(4) 根據特定電路的頻率下限和阻抗范圍,確定R和C的取值.

(5) 根據α,β,R和C的取值,設計優化標度分形塔分抗逼近電路.

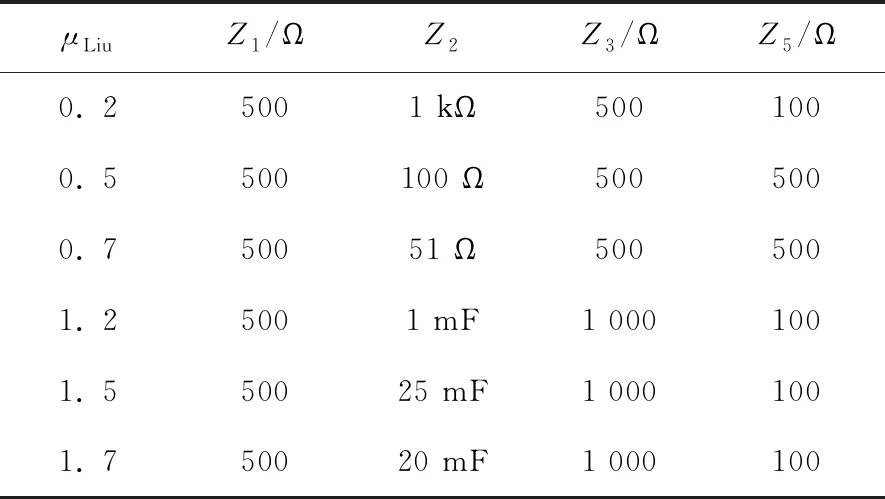

由上述步驟,以μLiu=-0.2,-0.5,-0.7為例,根據逼近帶寬和逼近精度等條件參數計算電路參數,設計實際優化標度分形塔分抗逼近電路. 條件參數及計算參數如表2.

Multisim14中仿真的幅頻特征曲線和相頻特征曲線(如圖12)表明,設計的優化標度分形塔分抗逼近電路可逼近具有目標運算階的理想分抗.

表2 標度分形塔分抗逼近電路設計參數表

圖12 不同運算階的頻域仿真曲線

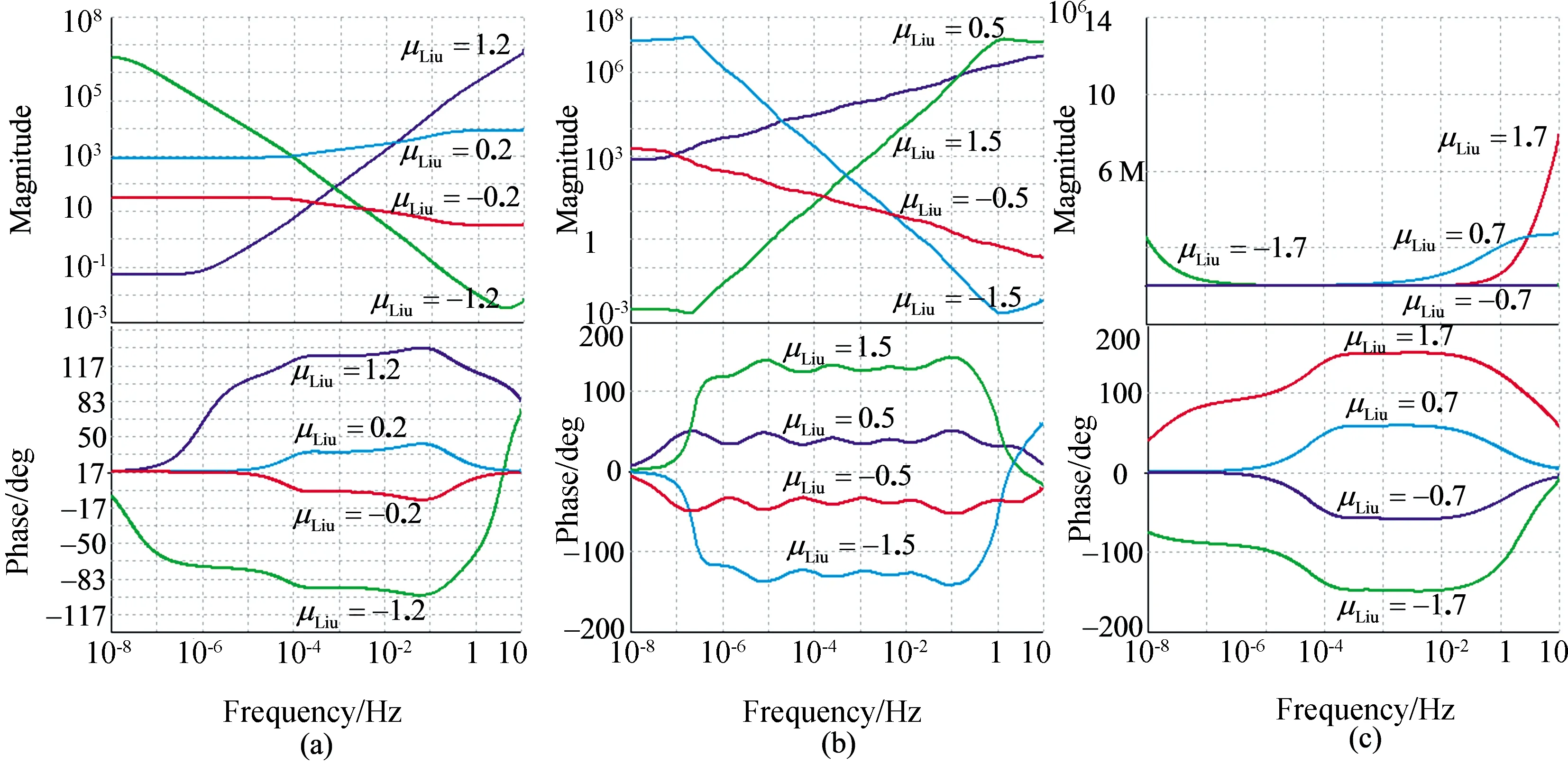

5.2 運算階的擴展

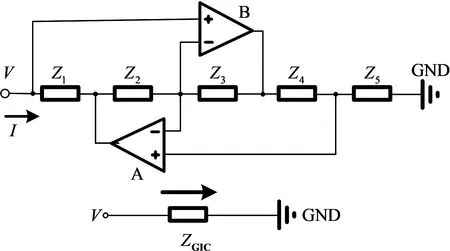

以上討論的標度分形塔分抗都是容性分抗且運算階-1<μLiu<0. 結合通用阻抗轉換器[20-24],使用電阻,電容和優化標度分形塔分抗構成有源電路網絡,便可實現運算階為-2<μLiu<-1的容性分抗及0<μLiu<2的感性分抗. 通用阻抗轉換器的典型電路和等效阻抗表達式為

(36)

A,B為理想運算放大器. 當Z5為μLiu階優化標度分形塔分抗,Z3為電容時便可構成(μLiu-1)階分抗. 將Z4替換為優化標度分形塔分抗,能夠實現(-μLiu)階分抗. 若將Z2替換為電容,Z4為優化標度分形塔分抗可實現(1-μLiu)階分抗. 以運算階為μLiu=-0.2,-0.5,-0.7的優化標度分形塔分抗為基礎,設計運算階為-2<μLiu<2的分抗. 設計參數如表3和表4.

圖13 接地通用阻抗轉換器(GIC)典型電路

模擬電路的頻域仿真曲線(如圖14)表明,以優化標度分形塔分抗為基礎,結合通用阻抗轉換器設計感性分抗的方法是有效的,該方法克服了實際電路設計中電感不易集成等問題.

表3 運算階為-2<μLiu<-1的設計參數

表4 運算階為0<μLiu<2的設計參數

圖14 不同運算階的頻域仿真曲線圖:-2<μLiu<2Fig.14 Frequency-domain simulation curves of different operational orders-2<μLiu<2

6 結 論

標度拓展B型分形塔分抗逼近電路,獲得具有任意分數階運算性能的標度分形塔分抗逼近電路,并由雙重標度方程(6)式描述. 根據(16)式選擇合適的標度特征參量α、β能夠設計任意階分抗逼近電路. 定量分析標度拓展后的頻域振蕩波形并給出振蕩模型函數. 根據標度因子取值,結合頻域曲線的形狀特征及電阻電容的電氣響應特性,理論分析標度分形塔分抗逼近電路的優化方法. 對比分析優化前后分抗的逼近性能. 由于電感不適宜集成,提出不使用電感的條件下將優化標度分形塔分抗的運算階由-1<μLiu<0推廣到0<|μLiu|<2的設計方法0<|μ|<2. 由實際工程需求介紹優化標度分形塔分抗實際應用設計方案并給出實例. 理論和實驗證明,本文提出的標度分形塔分抗的優化方法可行,優化標度分形塔分抗具有優良的應用價值.

標度分形塔分抗只是分抗逼近電路的一種,關于該分抗電路的優化還有如下需深入研究的問題:

(1) 是否存在優于本文的標度分形塔優化方法及優化元件參數值.

(2) 其他標度分形分抗電路同樣存在頻域曲線優化問題.

(3) 本文提出的優化方法是否具有普適性. 其他如四類Liu-Kaplan分形鏈分抗,標度分形格分抗等具有與標度分形塔分抗類似的頻域曲線形狀特征,本文的對稱T型節是否同樣可用于這些分抗的優化.

(4) 如何解析求解非正則標度方程(6). 如果能夠獲得該非正則標度方程解的解析表達式,或許可從數學解析的角度探討電路優化方法及優化參數.