國產JRAX1000型反熔絲FPGA應用演示系統設計

于躍,雋揚,曹靚,趙桂林,孫杰杰,楊霄壘

(中科芯集成電路有限公司,江蘇無錫,214072)

1 概述

中電五十八所研制的百萬門級JRAX1000型反熔絲FPGA內部邏輯資源等效門數100萬門,帶三模冗余加固的寄存器單元有6048個,時鐘資源包括4個硬線時鐘(Hardwired)和4個布線時鐘(Routed),此外芯片還內嵌了162Kbit帶自刷新(EDAC)功能的RAM塊[2]。JRAX1000型FPGA通過燒寫相應位置的反熔絲,將程序代碼固化在芯片內部,上電即運行,所以不需要額外的配置芯片引導啟動。采用JRAX系列反熔絲FPGA在硬件設計上,較傳統SRAM型FPGA簡便。由于反熔絲FPGA屬于一次可編程器件,不能多次編程,因而在代碼設計和調試方面,較傳統SRAM型FPGA復雜。為了解決代碼設計和調試上的難度,通常采用SRAM型FPGA驗證和調試代碼的邏輯功能,在邏輯功能驗證通過后,再將源代碼移植到反熔絲FPGA開發壞境Libero軟件中,進行時序約束和布局布線等操作,在時序滿足要求后,再通過燒寫器對程序進行固化。

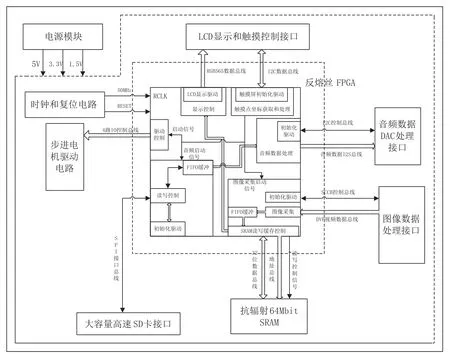

2 演示系統硬件設計

2.1 LCD顯示和觸摸控制電路

LCD顯示和觸摸控制電路作為整個系統的人機交互窗口,是兩個獨立功能的模塊。其中觸摸控制電路負責檢測人體在顯示屏上的觸點坐標,根據觸點在屏幕上不同區域的位置,系統開啟和關閉相應的功能。LCD顯示控制電路負責將系統運行的結果反饋在屏幕上,能直觀的看出演示效果。

反熔絲FPGA通過IIC總線與觸摸控制芯片FT5206進行通訊,完成對FT5206上電初始化,觸點坐標實時監測[3]。反熔絲FPGA對接收到的坐標信息,進行坐標變換,并判斷開啟或關閉相應功能操作。在系統運行結果顯示方面,反熔絲FPGA通過RGB565總線提供LCD液晶屏16位像素點數據,并按數據使能同步模式(DE MODE)、分辨率 1024×600,同步時鐘50MHz的方式顯示圖像。

2.2 音頻數據DAC處理電路

音頻數據處理電路采用WM8731芯片內部集成的數模轉換器DAC和運放,將存放在外部大容量SD卡內的無損音頻數據,轉換為采樣率48KHz的音頻模擬信號,并通過外部揚聲器播放出來。在音頻數據傳輸過程中,首先反熔絲FPGA通過SPI總線對外部SD卡初始化后,從SD卡中讀入音頻數據,并在FPGA內對數據進行處理,然后輸出到WM8731中進行模數轉換及信號放大[4]。其中FPGA通過IIS總線配置WM8731及數據傳輸,WM8731配置成從模式(Slave Mode)、過采樣率256×fs(fs為音頻數據采樣率48KHz)、20位采樣位數。因WM8731配置成從模式工作,所以WM8731的主時鐘MCLK和位時鐘BCLK都由反熔絲FPGA提供,這兩個時鐘頻率計算如下:

圖1 演示系統硬件組成框圖

2.3 圖像數據采集電路

圖像數據采集電路采用OV5640圖像傳感器,其內部集成感光陣列、增益放大器、10位模數轉換器ADC、圖像處理單元和時序發生器[5]。感光陣列將光信號轉換成模擬信號,經過增益放大后進入10位模數轉換器;ADC轉換器將模擬信號轉換為數字信號,圖像處理單元對數字信號進行壓縮、格式化等處理,在時序發生器的作用下,將圖像數據流按一定的時序輸出。

在圖像數據流傳輸過程中,首先反熔絲FPGA通過SCCB總線初始化OV5640圖像傳感器,設置傳感器內部系統時鐘、輸出圖像數據格式、水平和垂直像素點大小、曝光和白平衡等參數。在圖像傳感器初始化完成后,反熔絲FPGA通過DVP數字圖像接口采集圖像數據,并將采集到的數據存入外部64Mbit SRAM緩存。在一幀圖像數據緩存完后,將SRAM中的數據送入LCD驅動模塊并按相應時序進行顯示。在固定時間循環反復進行圖像數據采集、存儲,顯示等操作,完成圖像數據的更新。

3 反熔絲FPGA程序設計

反熔絲FPGA是一次可編程器件,不像其他可重復編程的FPGA,程序一旦燒錄進反熔絲FPGA中將無法修改,若程序運行不正確,則需要更換FPGA后重新固化程序,不利于代碼的調試,而且增加了設計成本。所以在代碼的前期設計和調試時,采用可反復擦寫的FPGA驗證代碼的邏輯功能,在邏輯功能驗證通過后,再將代碼移植到反熔絲FPGA開發平臺下。

反熔絲FPGA開發平臺是基于 Libero9.2 IDE軟 件,其 集 成Synplify編譯綜合、Modelsim仿真、時序約束、布局布線、以及生成反熔絲FPGA燒寫文件,最后通過專用燒錄器將程序文件固化到國產反熔絲FPGA中。反熔絲FPGA程序設計流程如下圖2所示。

圖2 反熔絲FPGA程序設計流程框圖

3.1 邏輯代碼設計與調試

在邏輯代碼前期設計與調試中,采用Altera公司EP2C20F484C8型FPGA作為邏輯代碼功能驗證FPGA。此SRAM型FPGA不僅可以反復擦寫,而且其內部自帶有SignalTap邏輯分析儀工具,便于程序的修改和調試,極大的提高了代碼開發的效率。

演示系統代碼設計采用自頂向下的模塊化分層設計,有利于功能劃分和模塊復用。具體的功能模塊設計如下圖3所示。

圖3 邏輯代碼模塊框圖

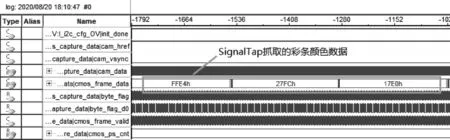

在代碼設計完成后,利用Altera公司FPGA自帶的SignalTap工具,對代碼進行調試。在圖3底部列出的圖像數據捕獲模塊中,為了便于觀測捕獲的圖像數據,先將圖像傳感器配置成輸出彩條模式,期望的輸出效果和采用SignalTap工具抓取到的圖像數據如圖4所示。由圖4可以看出,SignalTap抓取的彩條數據與期望的輸出數據一致,此模塊采用SignalTap調試正常。利用此工具調試完成所有邏輯模塊的功能。

圖4 SignalTap抓取圖像傳感器輸出彩條圖像數據

3.2 Libero時序約束及優化

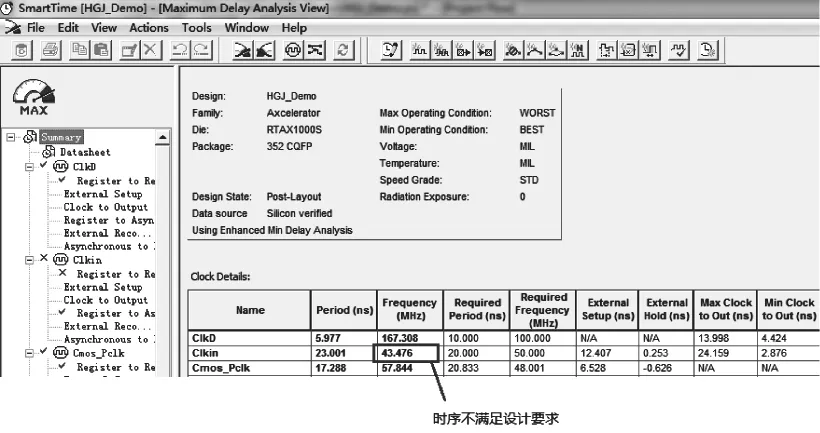

在代碼邏輯功能驗證通過后,將代碼移植到Actel公司的Libero IDE編程環境下,繼續完成反熔絲FPGA的后續設計工作。在Synplify綜合工具中添加FDC約束文件,其主要約束了程序的外部時鐘頻率、生成時鐘頻率以及IO端口[6]最大、最小延遲等參數。通過編譯綜合、布局布線后,時序報告顯示移植的源代碼最高頻率只能工作在43.476MHz,不滿足系統時鐘頻率50MHz的設計要求,如下圖5所示。而SRAM型FPGA在相同條件下,時序報告顯示工作頻率在66.42MHz,滿足系統設計要求,如下圖6所示。

圖5 反熔絲型FPGA時序分析報告

圖6 SRAM型FPGA時序分析報告

在Libero開發平臺下,基于反熔絲FPGA的代碼時鐘頻率不滿足設計要求,根據FPGA內部時序分析的基本原理,影響時鐘頻率的主要原因是部分路徑的延遲太長,造成FPGA內部寄存器的建立時間Tsu不滿足要求。所以為了提高設計的主頻,需要對建立時間Tsu違規的路徑進行分析和優化。通過以下三種優化方法和思路,可以將此演示系統代碼主頻提高40%左右。

(1)通過Libero平臺下的SmartTime時序分析工具,可以查看具體哪個路徑的建立時間余量最小,如下圖7所示。將此路徑對應到源代碼中分析,可以看出是代碼中構建的一個128位寬的寄存器變量,影響了整體的性能。所以對此寄存器變量的位寬進行拆分,將一個128位寬的寄存器拆分成兩個64位寬的寄存器變量。通過拆分的方法和思路,可以將此寄存器相關的路徑都約束至時序收斂。

圖7 部分違規路徑時序分析報告

(2)采用拆分的方法處理后,時序報告中還存在某些路徑建立時間Tsu不滿足要求,這時需要采用第二種方法:在延遲較大的組合邏輯路徑中插入寄存器,優化路徑的建立保持時間,使時序滿足設計要求,如下圖8所示。

圖8 插入寄存器優化時序路徑

(3)此外Libero開發軟件在布局布線過程中,也能設定布局布線的優化程度。布局布線優化程度越高,代碼的主頻速度越快,可是利用此方法提高速度效果有限。

除了對建立時間Tsu違規路徑優化外,還需要查看保持時間Th是否存在違規路徑。通常FPGA內部寄存器保持時間Th違規,主要是時鐘偏斜造成的。在程序設計過程中,盡量使用全局時鐘資源,避免使用分頻產生的時鐘作為寄存器的驅動時鐘,這樣可以有效減少時鐘偏斜,在時序分析時不會產生保持時間違規路徑。

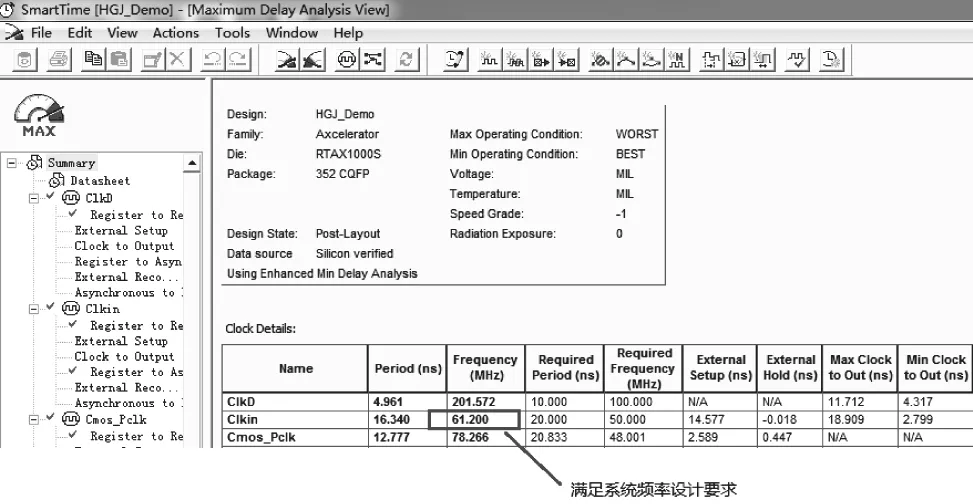

通過以上方法和思路,對時序約束不滿足要求的路徑逐一進行分析和優化,最終使程序穩定運行的頻率提高到61.2MHz,滿足50MHz的頻率設計要求,如下圖9所示。

圖9 優化后的時序分析報告

4 結束語

本文利用國產百萬門級反熔絲FPGA進行應用演示系統設計,從硬件功能劃分、程序設計、代碼優化等幾方面展開介紹,并最終將代碼固化到實際反熔絲FPGA中驗證,演示系統實現了幻燈片、圖像采集、音頻播放、電機驅動等功能,符合預期的演示效果。通過對比常用SRAM型FPGA和反熔絲型FPGA在時序分析時的差異,點明在反熔絲FPGA開發流程中時序約束的重要性。為將來國產百萬門級反熔絲FPGA的應用推廣,提供一定的實際參考意義。