基于性能匹配的SoC 自適應電壓調節系統

林勝楠,梁利平

(1.中國科學院 微電子研究所,北京 100029;2.中國科學院大學,北京 100049)

理論上電路的最佳運行電壓-頻率工作點取決于當前的運行環境,包括隨著芯片的集成溫度、壓降、老化、工藝差等,然而,芯片在設計階段就要考慮最壞情況下的運行條件,因此,設計人員往往在芯片設計階段,為了保證芯片的正常運行,使得最壞情況下依然能夠正常運行,留有較大的電壓余量[1],造成功耗的浪費。自適應電壓調節(Adaptive Voltage Scaling,AVS)技術可以顯著壓縮電壓余量,被廣泛研究。文獻[2-5]介紹了基于Razor 結構的AVS 系統。文獻[6]提出了一種基于可調復制電路(Tunable Replica Circuit,TRC)來監測電路溫度以及老化,TRC 觸發AVS 調節系統,電路運行時根據需要動態調整供電電壓,以保持在最小電壓下功能正常。文獻[7]將可配置的延時鏈用于數字低壓差線性穩壓器(DLDO)設計中,減少在電壓發生下過沖時產生的功能異常。文獻[8-12]也評估了擬合延時鏈技術應用于自適應電壓調節系統的可行性。

1 AVS系統設計

1.1 電壓對延時和功耗的影響

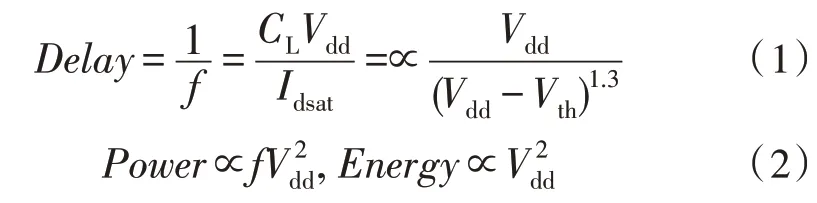

大多數的應用程序并不是總要求電路的頻率處于最高狀態,隨著處理器頻率的降低,電源電壓也可以降低。電壓與功耗以及延時的關系如式(1)、(2)[13]。當電路的頻率降低時,其電壓也可以降低,動態功耗與頻率以及電壓的二次方成正比,所以當頻率和電壓都降低時,功耗以三次方的速度降低,但是隨著頻率的降低,完成一項任務的時間增加,所以完成一項任務所需的總能耗以二次方的速度降低。故可知降低電壓對能耗的降低是非常有效的。

1.2 AVS系統整體結構

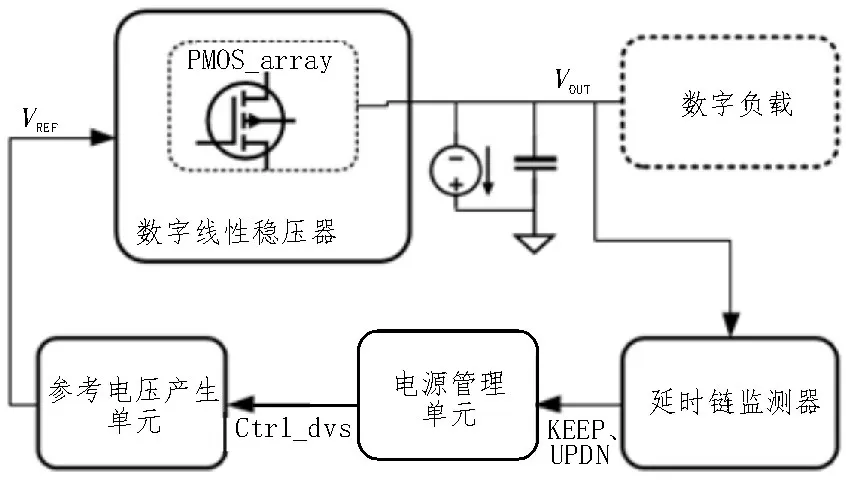

自適應動態電壓調節系統主要包括延時鏈監測器、電源管理單元、數字穩壓器、參考電壓產生單元4 個部分,如圖1 所示。數模轉換器采用文獻[14]中的分壓偏置電路。延時鏈監測器可以監測當前數字負載的時序余量,輸出2 bit的數字信號(KEEP、UPDN)指示當前電壓是否是當前運行環境(包括溫度、工藝、頻率)下的最合適電壓。使用DLDO 代替Buck 變換器或開關電容DC-DC 變換器,因為數字LDO 不需要芯片外電感而且可以提供對輸出電壓的精確控制,為了減小供電電壓的電壓波紋并提高響應速度,采用文獻[15]中提出的結合推挽輸出和電壓峰值監測的數字LDO 來為數字負載供電,數字LDO 會將供電電壓調節到參考電壓。電源管理單元為純數字控制邏輯,會根據延時鏈監測器的輸出狀態調整數控電壓信號,將其輸入到數模轉換器來提供參考電壓,參考電壓每次變化一個步長或者不變,采用的電壓調節步長為100 mV。這種全數字設計對數字電路友好,可以形成一整套基于EDA的低功耗設計流程。

圖1 自適應電壓調節系統結構圖

1.3 延時鏈監測器

延時鏈監測器結構如圖2 所示,其是該自適應電壓調節系統的核心模塊,用于監測測試脈沖在延時鏈傳遞時的時序余量。監測器全部由數字標準單元構成,主要由延時鏈、4 個D 觸發器、組合門邏輯以及控制邏輯電路構成。文獻[16]中闡述了電壓過沖時鐘樹的延時變化對時鐘周期的影響,所以監測器的采樣時鐘均采用經過時鐘延時鏈(與關鍵路徑采樣時鐘延遲一致)的時鐘clk_d,以此模擬時鐘樹對時序的影響。監測使能信號有效時,時鐘二分頻脈沖信號作為延時鏈的輸入信號,經過延時鏈和D 觸發器采樣后與直接D 觸發器采樣的信號異或得到S0、S1,S0、S1 信號分別指示電壓上升或下降,經控制單元輸出KEEP、UPDN 信號,控制電源管理單元。

圖2 延時鏈監測器結構圖

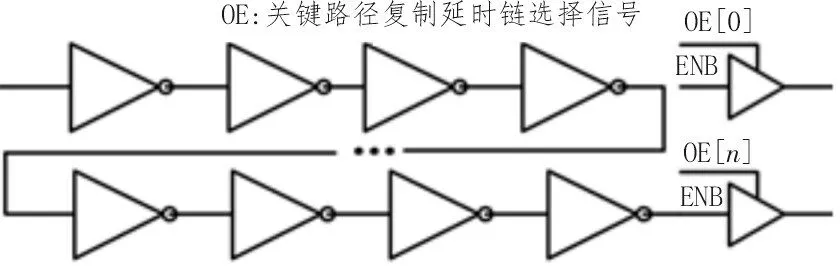

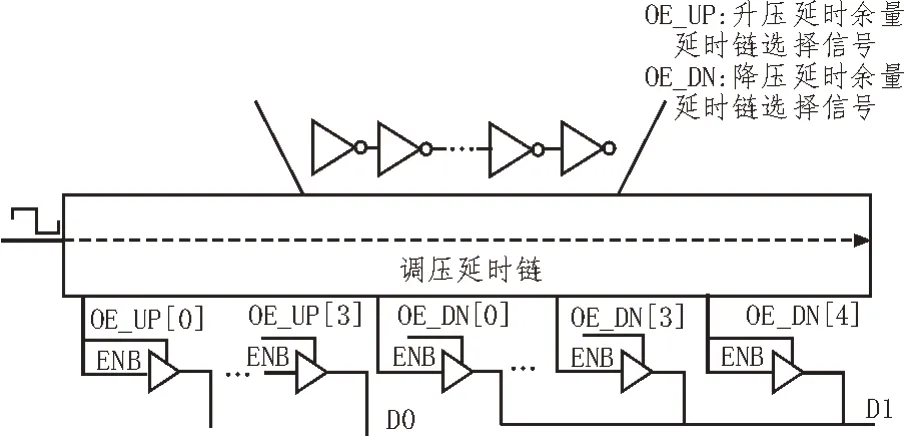

用于監測脈沖信號的延時鏈由可配置的關鍵路徑復制延時鏈(Critical Path Replica,CPR)和調壓余量延時鏈(Adjust Voltage Timing Margin,AVTM)構成。可調制關鍵路徑復制延時鏈,如圖3 所示,由反相器首尾相接構成,長度由數字負載的關鍵路徑長度決定。調壓余量延時鏈,如圖4 所示,其也是由反相器首尾連接構成,升壓余量監測信號D0和降壓余量監測信號D1 是電壓敏感的,基于不同電壓下延時變化一個電壓步長,關鍵路徑延時變化差別很大,根據電路當前的工作電壓選擇不同的延時鏈長度。

圖3 可調制關鍵路徑復制電路圖

圖4 調壓時序余量結構圖

1.4 線下校準程序

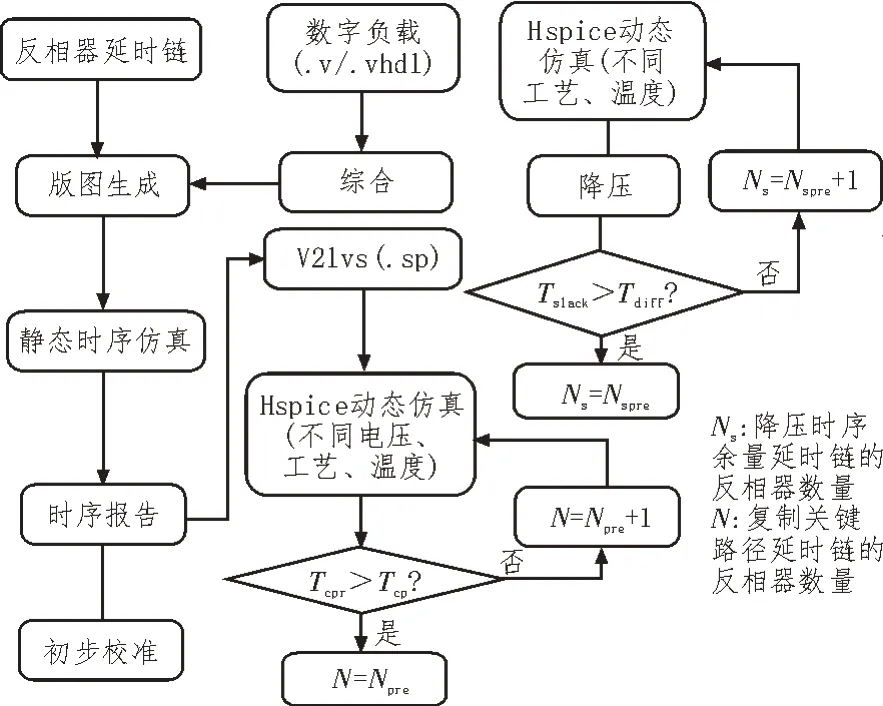

自適應電壓調節系統很重要的一個方面是如何精確關鍵路徑監測器跟蹤真實關鍵路徑在溫度、老化和電壓過沖下的延時行為;另一個方面,也要考慮降低一個電壓步長時需要在當前運行電壓下留出的時序余量,從而在保證功能正常的情況下最大限度節省功耗。圖5 顯示了延時鏈監測器的線下校準程序,該程序考慮了復制關鍵路徑對溫度、電壓以及工藝的靈敏度影響。

圖5 線下校準程序圖

采用靜態時序仿真和動態時序仿真相結合的方式校準CPR。延時鏈監測器是面向特定數字負載的,所以該方法首先對數字負載進行靜態時序分析,提取數字負載的關鍵路徑(包括標準單元和RC參數)。與此同時,對可配置的反相器延時鏈生成物理版圖,同樣進行靜態時序分析,預估匹配關鍵路徑延時的反相器延時鏈的長度N。然后,依照復制關鍵路徑延時鏈的延時比真實關鍵路徑延時鏈延時大的原則,動態仿真關鍵路徑在不同環境下的延時行為,最終確定關鍵路徑復制反相器延時鏈的長度N。

動態仿真確定圖4 中降壓時序余量延時鏈的長度Ns。降壓時序余量延時鏈長度的確定:基于不同的電壓下,延時變化一個電壓步長關鍵路徑延時變化不同,電壓從最低電壓到最高電壓,不同的工藝和溫度條件下對提取的關鍵路徑進行仿真掃描,特定電壓下,在不同工藝、溫度條件下,電壓下降一個電壓步長選取最大的延時增量?t,以此為標準選取該電壓下降低電壓的余量延時鏈長度Ns,使其延時與?t相近。相比于文獻[6]中的校準程序,該校準程序不需要因為運行頻率的不同重新校準監測器的bit 值,只面向數字負載的關鍵路徑,所以大大縮短了校準時間。

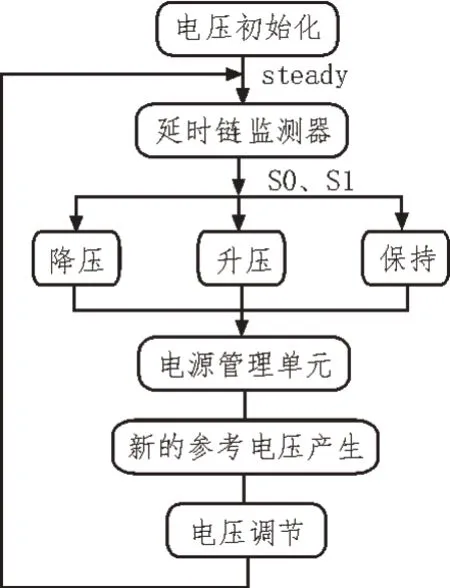

1.5 自適應電壓調節過程

圖6 是自適應電壓調節的流程圖,首先電壓初始化到初始電位,電壓穩定后,延時鏈監測器會根據當前電路運行頻率產生一個二分頻的脈沖,延時鏈監測器輸出KEEP、UPDN 信號,電源管理單元根據延時鏈監測器的結果升壓、降壓或者保持當前電壓,若產生新的參考電壓,數字LDO 重新對低電壓進行調節,此時為了節省功耗關閉延時鏈監測器,形成反饋回路。

圖6 自適應電壓調節流程圖

2 仿真與結果分析

2.1 仿 真

該設計采用SMIC 55 nm 工藝,通過Hspice 進行了后仿真。根據電路運行環境和頻率,自適應調節供電電壓到適當水平,當KEEP=0,UPDN=1 時,升高電壓;當KEEP=0,UPDN=0 時,降低電壓;當KEEP=1時,保持當前電壓不變。將電壓調節到適應當前頻率和運行環境的最小電壓,從而明顯節省功耗。

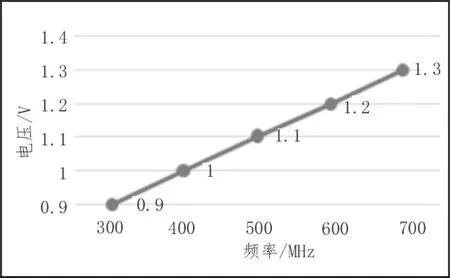

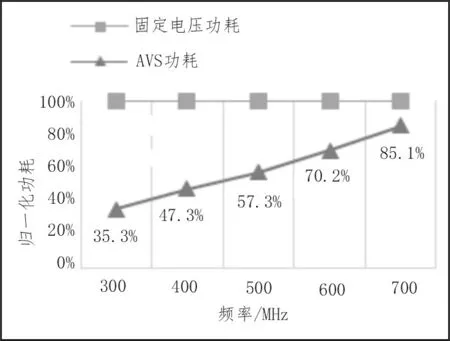

將自適應電壓調節系統應用到濾波器上來檢測其效果,之所以用濾波器,因為濾波器中的加法器、乘法器是數字電路中的常見單元,具有代表性。圖7中是特定工藝角、溫度條件下不同頻率調節到的最合適電壓,相比于固定電壓1.4 V,頻率從700 MHz下降到300 MHz,電壓下降了約7%~36%,相應功耗節省了約14.9%~64.7%,如圖8 所示。

圖7 AVS電壓和頻率的關系

圖8 AVS功耗與固定電壓1.4 V功耗對比

2.2 結果分析

文中提出的延時鏈監測器能夠實時監測電路頻率以及PVT的變化,且監測精度完全適應于電壓調節的需求,能夠準確監測到降低一個電壓步長所需的時序余量。表1 將文中延時鏈監測器與已發表文獻進行了對比。可以看到,監測器的監測信號一般是時鐘信號經過觸發器產生,輸出數字信號。文中關鍵路徑擬合采用通過校準后的可配置反相器延時鏈,相比于嵌入真實關鍵路徑的監測器,省去了選擇關鍵路徑這一復雜步驟,不會對負載電路產生影響,且結構簡單、可移植性好。監測器的面積評估,包括時序轉數字單元和數字控制模塊的面積,該文監測器的面積明顯小于其他文獻。監測器靈敏度的比較是非常困難的,沒有統一的標準,監測器的靈敏度與產生數字信號的延時鏈分辨率、不同的架構以及電路的運行環境(包括工藝、溫度、運行頻率)有很大的關系,這里列出的靈敏度根據每篇文獻的測量結果給出,該文可以監測降低一個電壓步長(100 mV,根據電壓調節方案可以更小)的時序余量。

表1 該文延時鏈監測器與已發表文獻對比

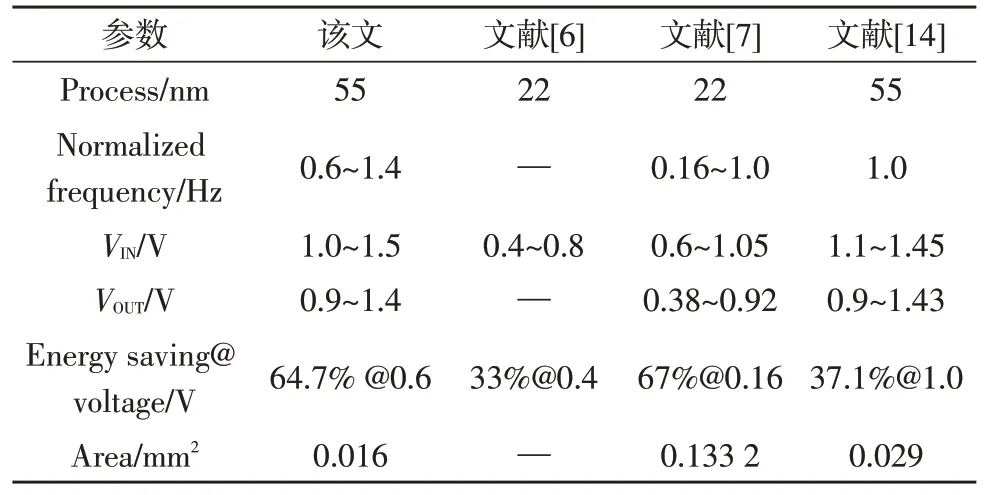

表2 將文中的AVS 系統和已發表文獻進行了對比,表中列舉文獻的運行頻率以及電壓調節的范圍,因為AVS 對功耗的節省跟電路頻率以及當前工作電壓有很大的關系,所以引入歸一化頻率,將功耗節省對應到當前運行頻率上。該文的功耗節省是在工藝SS、125 ℃情況下進行評估的,在歸一化頻率為0.6時,相比于固定電壓功耗節省64.71%。該文實現的AVS 系統能夠適用于較大頻率范圍內的電壓調整,實現功耗優化,且面積較小,能夠達到一個較有競爭力的水平。

表2 該文AVS系統與已發表文獻對比

3 結論

文中提出了一種基于線上實時監測和線下校準相結合的自適應動態電壓調節系統,能夠根據電路運行頻率和運行環境對供電電壓做出調整。該文提出的延時鏈監測器結構更加簡單,面積小,將其結合數字LDO 實現了自適應電壓調節,適用于寬頻率以及PVT 條件的監測,AVS 系統采用SMIC 55 nm CMOS 工藝,在125 ℃、SS 工藝角下,頻率從700 MHz下降到300 MHz時,相比于固定1.4 V 電壓,AVS 功耗節省14.9%~64.7%,能夠達到一個較有競爭力的水平。