塑閃陣列探測器讀出ASIC 閾值產生與調節電路的設計

敬雅冉,千 奕*,蒲天磊,趙紅赟,楊鳴宇,孫志坤,張家瑞,孔 潔,佘乾順,顏俊偉,孫志朋,王長鑫

(1. 中國科學院近代物理研究所 蘭州 730000;2. 中國科學院大學核學院 北京 石景山區 100049)

我國首顆暗物質粒子探測衛星“悟空號”,在電子能譜~0.9 TeV 處測量到了拐折,并在~1.4 TeV處發現了疑似的精細結構跡象,引起了國內外同行的高度關注[1]。然而,受限于探測器的尺寸和結構,“悟空號”的伽馬射線探測能力較弱。為了提升伽馬射線的探測能力,科學家提出要研制新一代高性能的甚大面積伽馬空間望遠鏡 (very large area gamma-ray space telescope, VLAST)[2]。VLAST 包括4 個子探測器,分別是徑跡探測器、量能器、中子探測器和塑料閃爍體陣列探測器(the plastic scintillator array detector, PSD)[3];其中大面積PSD對前端讀出電子學提出了多通道、大動態、高計數率的需求;同時由于衛星功耗資源及硬件的限制,還要求前端讀出電子學具有緊湊型、低功耗、低噪聲及抗輻照等特性。隨著半導體探測技術的日趨成熟,高集成度的專用集成電路(application specific integrated circuit, ASIC)芯片技術已被廣泛應用于粒子物理與核物理實驗的譜儀系統中;在空間探測領域中,這一技術也逐漸成為發展趨勢,ASIC 芯片的利用,極大簡化了前端電子學的設計,減少了星上功耗開銷和硬件支出[4]。因此,需要研制一款多通道ASIC 芯片,用于實現大面積PSD 對核素電荷的處理與測量。

1 ASIC 芯片設計

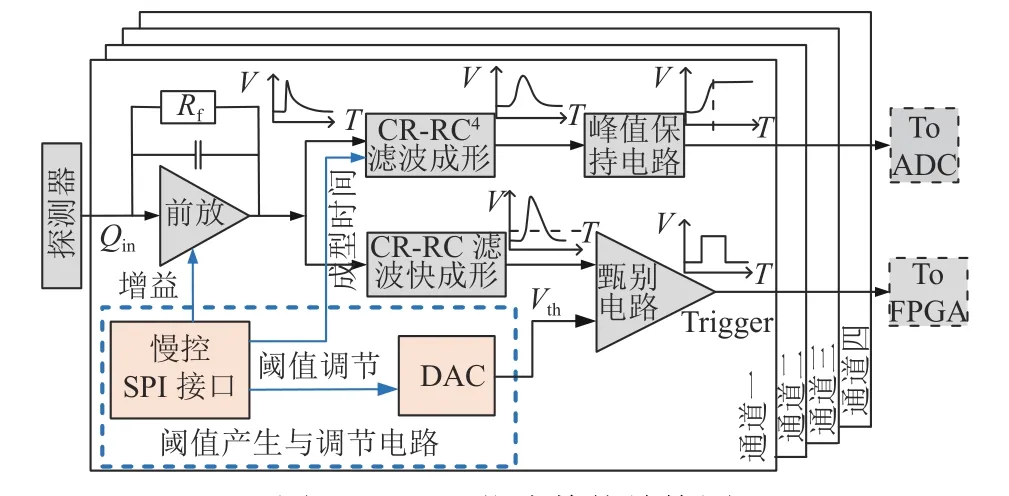

ASIC 芯片的整體結構圖如圖1 所示,其中每通道包括低噪聲前放、CR-RC 濾波成形、峰值保持電路、甄別電路、SPI 慢控接口[5-6],同時該芯片具有自觸發模式,每通道輸出獨立的觸發信號,觸發閾值由片內數模轉換(DAC)模塊產生[7]。本文主要設計了ASIC 芯片中閾值產生與調節電路(圖1虛框內所示),通過SPI 控制接口,可以為片內的甄別電路提供可調節的觸發閾值[6]。在物理實驗中,由于不同離子的能量不同,經前放和快成形電路處理后的輸出電壓也不同,該輸出電壓進入甄別電路和閾值電壓進行比較后輸出Trigger 信號。通常,對閾值電壓的設置是越低越好,在保證抑制噪聲的前提下,讓盡可能多的信號過閾。但是,有時為了降低Trigger 率,需要提供較高的閾值電壓。本設計中的閾值電壓具有較大的調節范圍,約15~960 mV,最小調節步進好于4 mV,INL 和DNL 均好于0.2 LSB。

圖1 ASIC 芯片整體結構圖

2 閾值產生與調節電路的設計

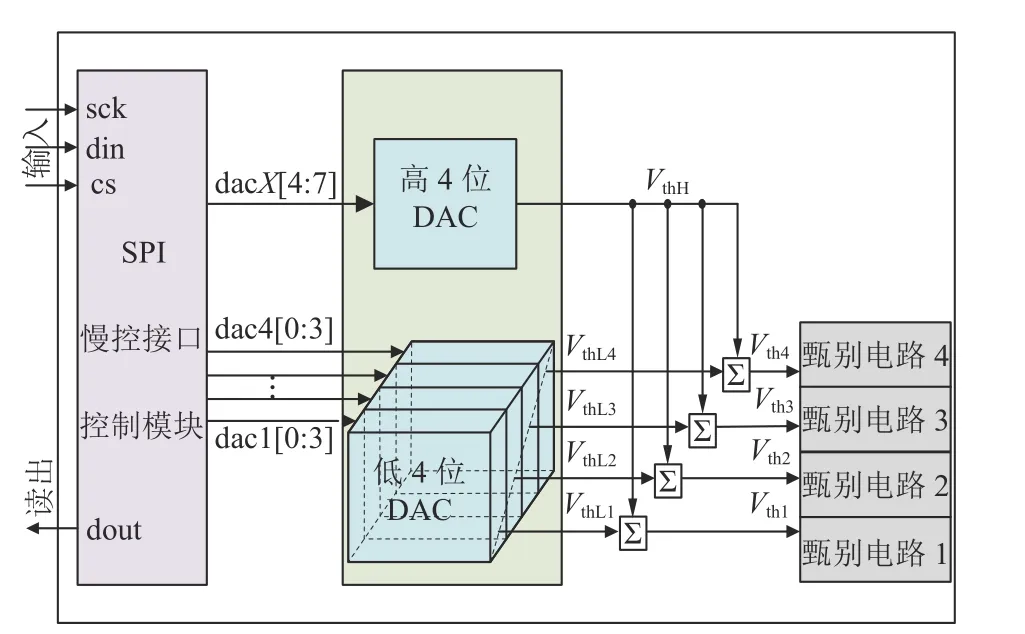

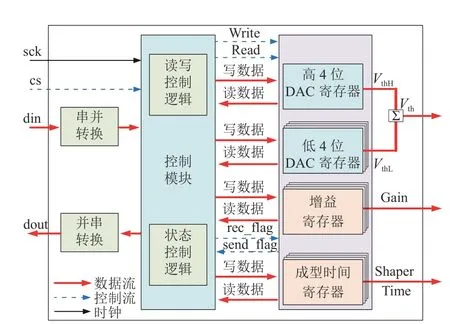

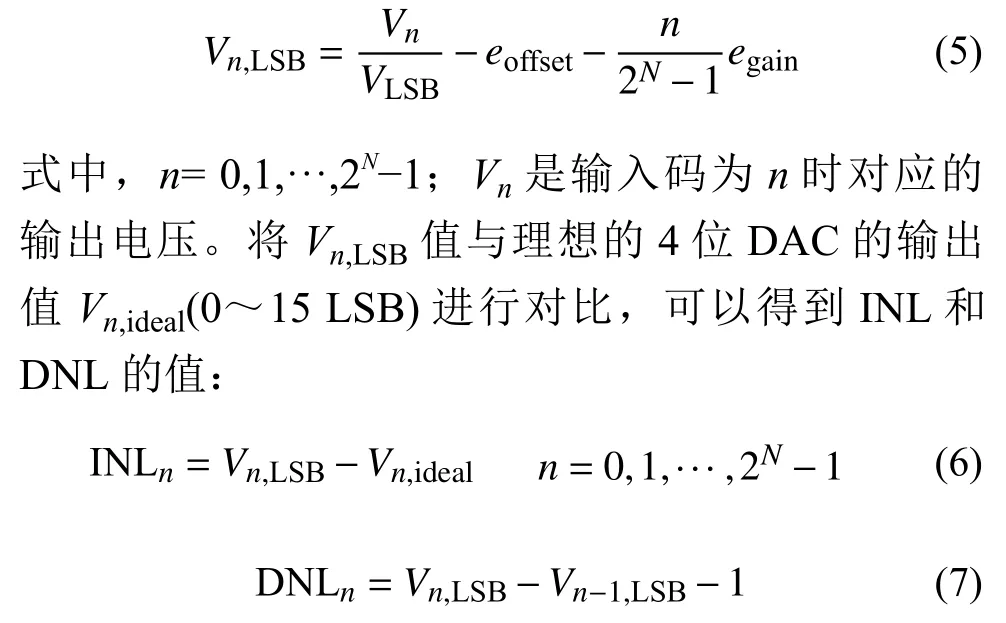

芯片中的觸發閾值產生與調節電路利用高4位DAC 與低4 位DAC 結合的方法,實現一個8 位DAC 的閾值調節,其結構如圖2 所示。包括DAC 模塊和基于SPI 慢控接口的控制模塊,外部輸入信號通過SPI 慢控接口的din 端口輸入,門控信號sck 在使能信號cs 為低時有效,并對相應DAC 寄存器進行讀寫。通過改變寫入寄存器的數據來控制DAC 的輸入信號,從而控制DAC 的輸出幅值,為甄別電路提供了可調閾值。

圖2 閾值產生電路的結構

為了簡化芯片內部電路結構,減小版圖面積,降低功耗,提出通過組合高、低兩個4 位DAC分別進行粗細閾值調節來實現一個8 位DAC 閾值調節的方法。在芯片內所有通道復用一個高4 位DAC,實現閾值的粗調,產生閾值電壓VthH,調節范圍約為900 mV;每個通道內部包含一個低4 位DAC,實現閾值的細調,產生閾值電壓VthL,調節范圍約為60 mV;每通道內甄別電路的輸入閾值電壓Vth=VthH+VthL。通過粗調和細調相結合的方法,實現了大動態范圍、高精度的閾值電壓調節。

2.1 DAC 模塊設計

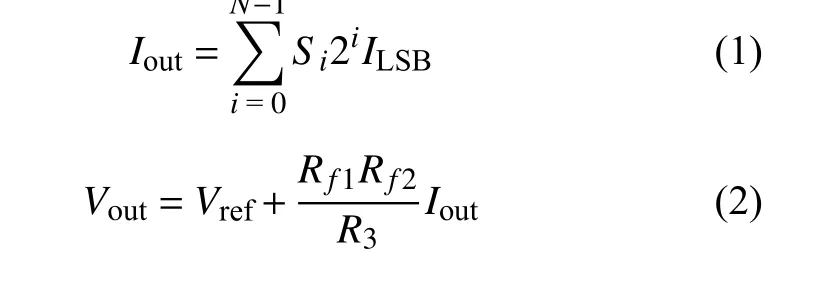

為了在芯片內設計并實現面積小、功耗低、轉換速度較快的DAC 模塊,對比不同類型DAC 的優缺點[8-10],并對設計要求進行衡量,本文最終選擇采用電流按比例縮放型中的二進制加權型電流舵DAC。電流舵DAC 首先利用有源器件MOS 管構成加權電流源,再通過數字輸入信號選通相關電流源支路輸出;數字輸入信號的不同,決定開關陣列電路中每個開關的通斷,從而決定每個電流源陣列是否接入電路。隨著數字輸入信號的變化,流入運算放大器的電流隨之變化,其輸出端的電壓也發生變化,實現數字信號向模擬信號的轉變。圖3 所示為電流舵DAC 的結構,包括N個二進制電流源:ILSB, 2ILSB, ···, 2(N-1)ILSB,其中,ILSB表示最小權值對應的電流大小。當第i位輸入數字信號Si=1 時,受信號Si控制的開關閉合,第i個電流源與運算放大器的輸入負端連接,相反,當Si=0時,開關Si斷開,對應電流源的輸出電流不再流入運算放大器中。所以,流入運算放大器I1 的電流Iout如式(1)所示,DAC 的輸出電壓Vout如式(2)所示:

圖3 二進制加權型電流舵DAC 結構

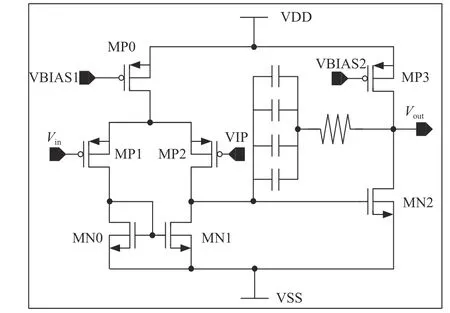

圖中,I1 和I2 均為低失調、高增益、低噪聲的運算放大器。I1 主要是把加權電流源網絡的權電流轉化為電壓輸出,并提高輸出的精度。其結構如圖4 所示,由兩級電路組成。

圖4 運算放大器電路結構

第一級為差分放大級,由MP0、MP1、MP2、MN0 和MN1 共5 個晶體管組成,由于PMOS 具有良好的抗輻射能力,MP1 與MP2 差分對使用PMOS 作為輸入級,差分對管通過調整柵長與寬長比,能夠顯著降低失調,由于L的增大,導致單極運算放大器無法滿足增益需求。因此,第二級采用了共源級來進一步提高增益,由MP3、MN2 共2 個晶體管組成。I2 為低失調的運算放大器,可對I1 的輸出信號進行反向并提高驅動能力。由于DAC 需要驅動較大的容性負載,所以采用大驅動能力的運算放大器能夠提高電路的穩定性。

2.2 SPI 慢控接口模塊設計

串 行 外 設 接 口 (serial peripheral interface, SPI)是一種高速、同步、全雙工的通信總線,連線簡單,可以有效節約芯片的輸入管腳[11-12]。本文設計的SPI 慢控接口模塊的功能包括:控制前放的增益、控制成型時間的檔位以及控制DAC 的輸入來調節甄別電路的觸發閾值。圖5 為SPI 慢控接口模塊的設計結構框圖,數據信號通過數據線din 輸入,通過串并轉換模塊后,進入控制模塊。控制模塊中的讀寫控制邏輯對并行數據進行判斷,并識別讀寫控制信號,當控制信號為寫信號時,在狀態控制邏輯的控制下,進入寫數據過程,向各個寄存器中寫入數據信號;當控制信號為讀信號時,在狀態控制邏輯的控制下,進入讀數據過程,從相應寄存器中讀出并行數據信號,再通過并串轉換模塊,由dout 數據線輸出。外部串行數據在使能信號有效時,通過SPI 慢控接口完成對寄存器的讀寫,寫入寄存器中的數據作為DAC 模塊中開關的控制信號。本文中,時鐘頻率設計為30 MHz,輸出可驅動負載電容為6 pF。

圖5 SPI 慢控接口結構

3 電路仿真

3.1 DAC 模塊仿真結果

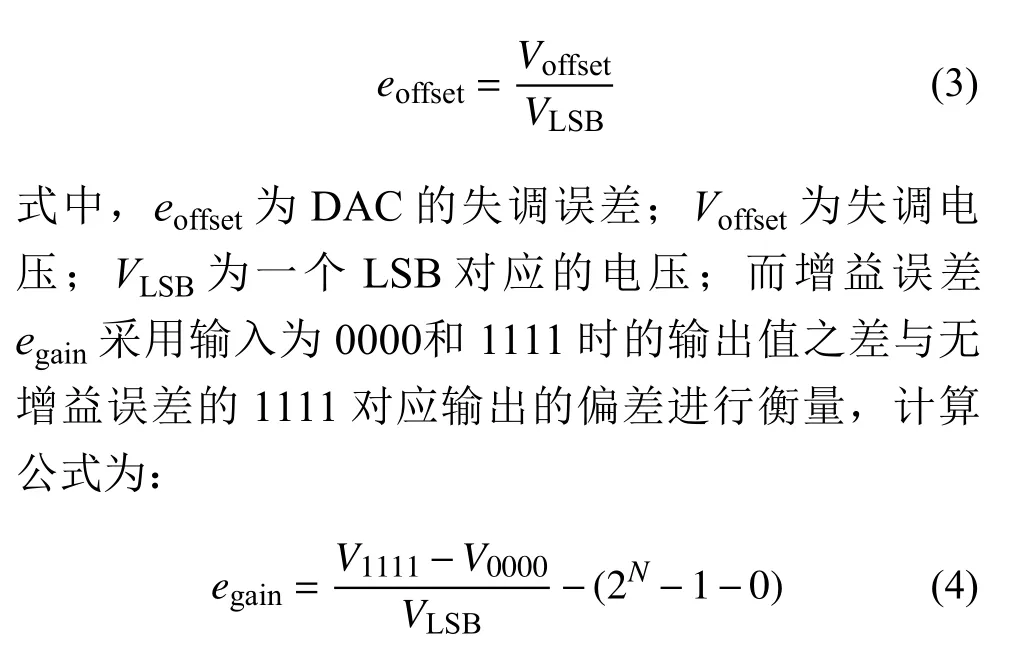

DAC 模塊的設計基于3.3 V 電源電壓,利用Spectre 軟件對閾值粗調的高4 位DAC 和閾值細調的低4 位DAC 進行原理仿真。相比于粗調的DAC,細調DAC 的精度要求更高。常溫條件下,對細調的低4 位DAC 進行前仿真和提參后的后仿真,并分別對數據進行處理,計算INL 和DNL 值:

式中,N為DAC 的位數。計算非線性INL 和DNL 時,首先應去除失調誤差eoffset和增益誤差egain,然后采用LSB 進行歸一后,各個輸出值Vn,LSB為:

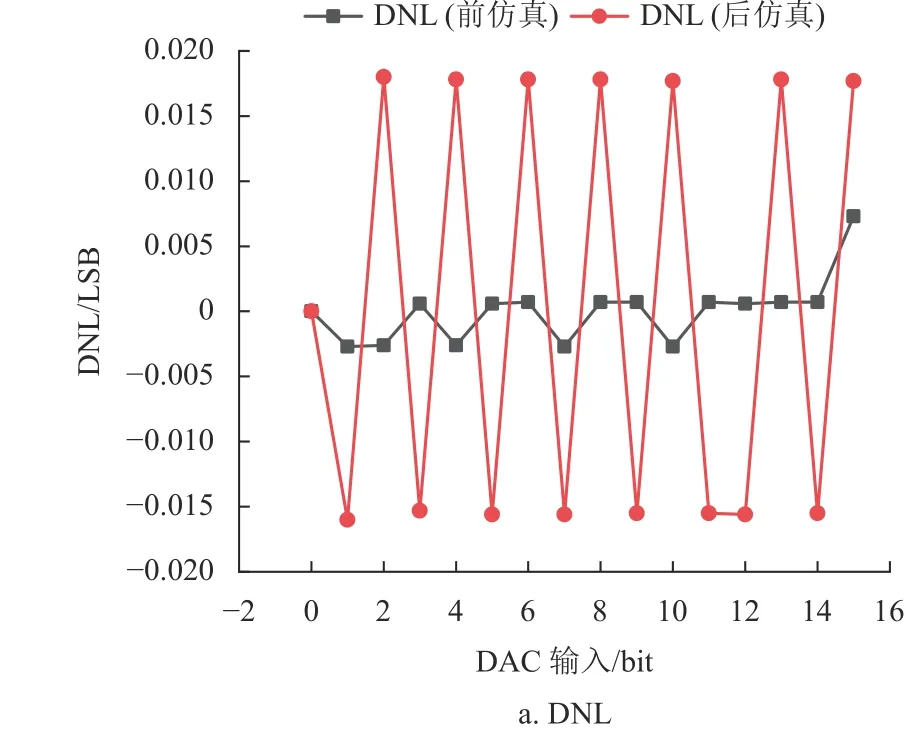

對計算出的數據進行擬合,從而得到DAC 前后仿真的DNL對比圖和INL 對比圖,如圖6 所示。

圖6 低4 位DAC 的DNL 和INL 仿真圖

從圖中可以看出DNL 為?0.016~0.018 LSB,INL 為?0.02~0.011 LSB,線性均小于0.02 LSB,表明設計具有較好的線性。

3.2 SPI 慢控接口模塊仿真結果

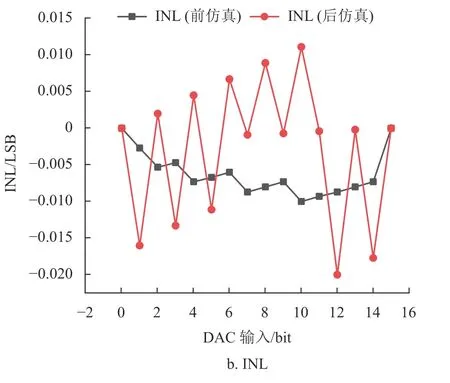

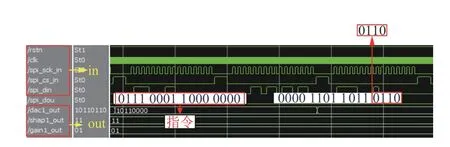

首先利用Modelsim 軟件對設計的SPI 接口模塊進行RTL 級功能仿真驗證。在testbench 文件中,設置基本時鐘周期clk 為100 ns,信號時鐘周期sck 為1000 ns,整個寫數據仿真流程如圖7 所示,按照寫入復位信號、寫入公共成型時間和公共增益信號、寫入公共高4 位DAC 值,以及寫入各通道低4 位DAC 值依次進行仿真和驗證。

圖7 寫數據仿真流程圖

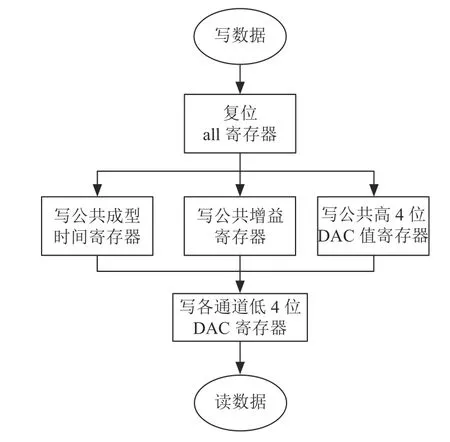

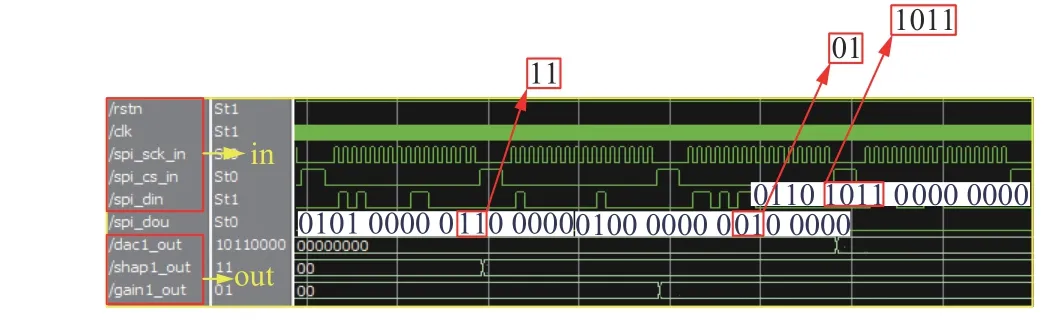

以寫數據操作驗證為例,寫公共部分數據時,高4 位為指令,規定寫的寄存器,后面指定位為實際寫進寄存器的數據,分別驗證了寫公共成型時間、寫公共增益和寫高4 位DAC 數據,仿真圖如圖8 所示,可以看出相應寄存器中被寫入與指令中數據位相同的數據。寫各通道低4 位DAC 數據的仿真圖如圖9 所示,先是16 位的指令,包括指定要寫的低4 位DAC 的通道號以及使能位,后是16 位數據位,圖中標出來的框圖為輸入寄存器的數據,同時可以看出低4 位DAC 寄存器中也被寫入與框圖中一致的數據。即寫數據過程滿足設計要求。讀數據操作驗證結果也一致。表明所設計的SPI 慢控接口能夠對寄存器進行正確的讀寫操作。

圖8 寫公共成型時間、增益及高4 位DAC 數據波形圖

圖9 寫低4 位DAC 數據波形圖

功能仿真驗證后,利用Synopsys 公司的DC(design compiler)軟件,對代碼進行綜合過程,將RTL 代碼映射為與工藝庫相關的網表文件;然后利用Cadence 公司的SOC Encounter 軟件進行后端的布局布線,對綜合產生的門級網表進行布局規劃(floor planning)、布局布線(placement& routing),并生成生產用的版圖;再對版圖進行提參(starrc)、靜態時序分析(STA)和形式驗證(formality),以便進行后仿真。完成后仿真后,對得到的后仿真結果和前仿真結果進行對比,每個輸出信號的延時時間在6 ns 以內,完全符合輸出設計要求,也保證了流片結果的可靠性。

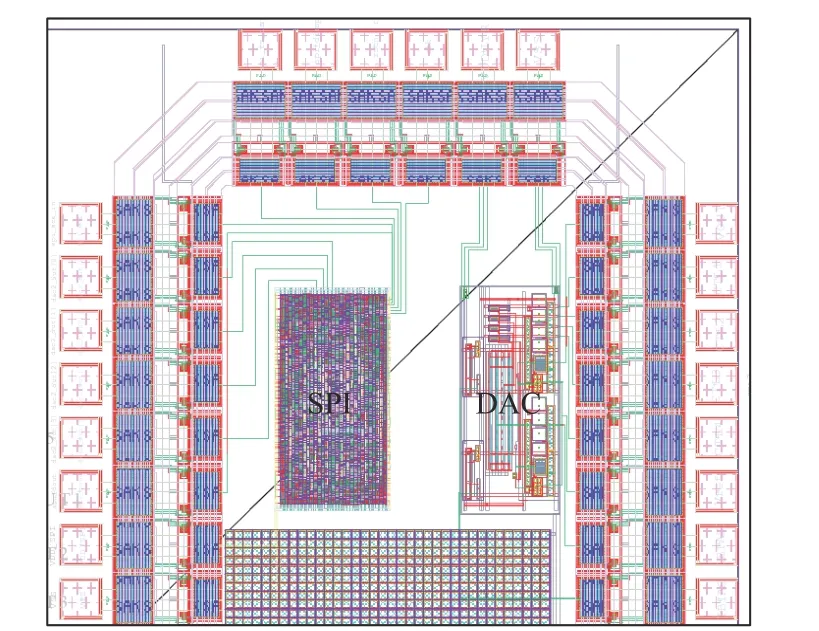

4 版圖設計

該芯片采用 global foundries (GF) CMOS 0.18 um工藝,3.3 V 單電源供電。芯片整體版圖如圖10 所示,尺寸為800 um×1000 um。芯片在foundry 流片后,使用QFN68 進行封裝。

圖10 整體模塊版圖

在版圖設計過程中,考慮到設計的用途,對版圖進行了優化,包括電路中的信號線采用適當的寬度并且走線要盡量短,減小寄生參數;偏置電路的位置要避開電路的敏感器件;在電流源陣列布局時,考慮不同電流源的權重不同,將電流源陣列采用共質心布局來減小失配。

同時,為了防止發生單粒子閂鎖,DAC 模塊的版圖設計時加入了抗輻照考慮,采取以下措施:1)在晶體管周圍增加保護環;2)盡量讓NMOS 靠近VSS,PMOS 靠近VDD,使NMOS和PMOS 晶體管之間保持足夠大的距離;3)在晶體管四周密集排布阱接觸孔,減小接觸孔與晶體管有源區的距離。

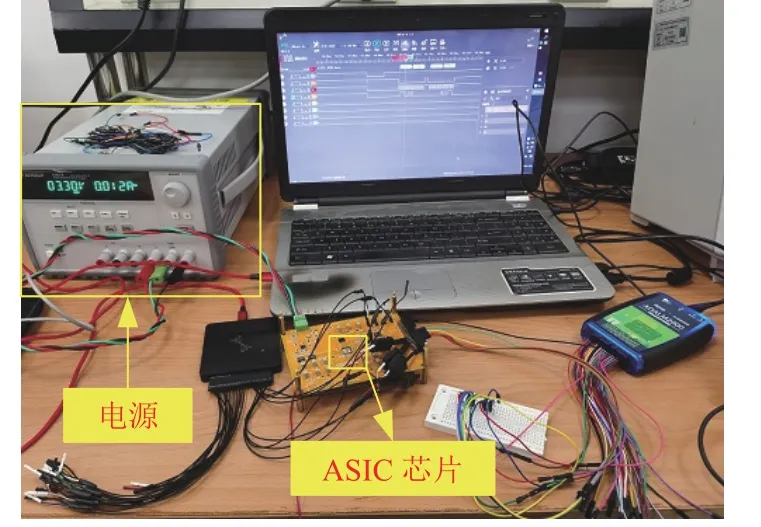

5 電路測試

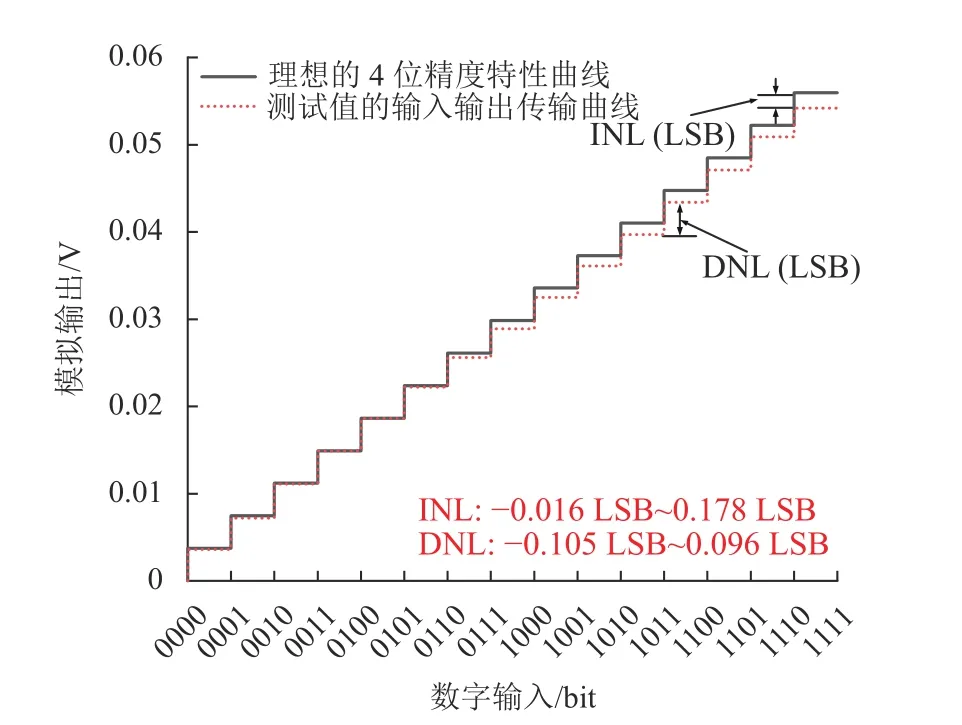

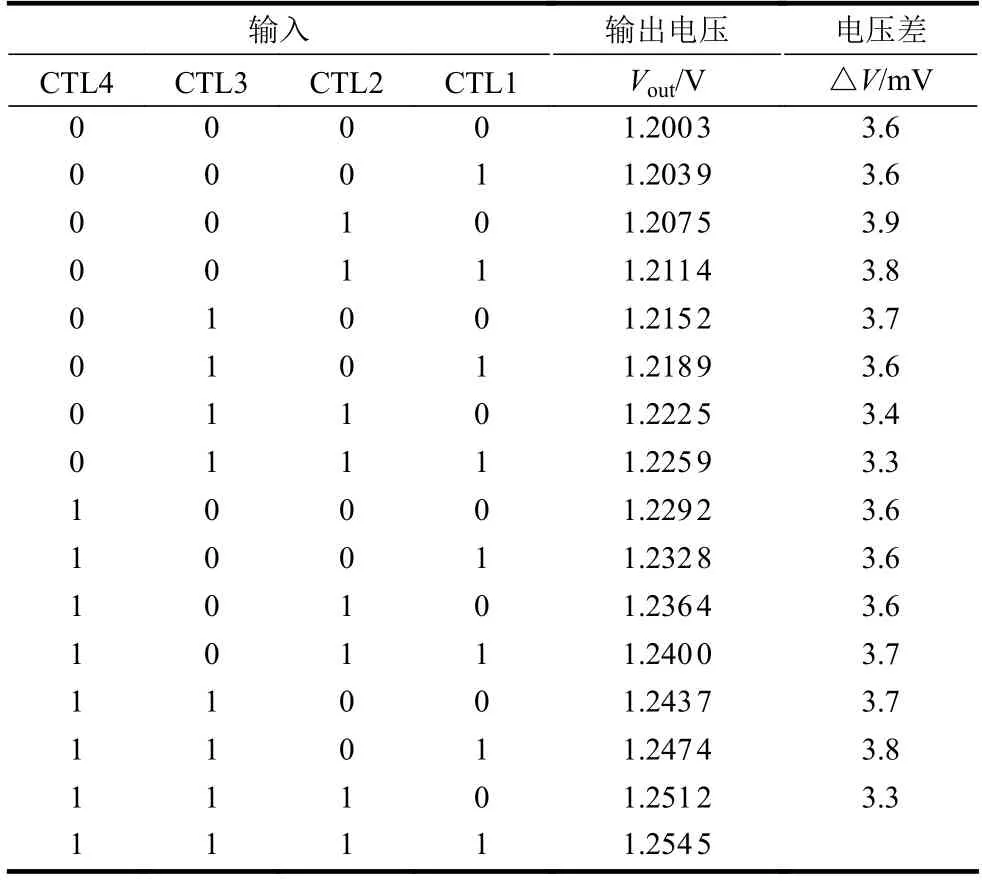

在實驗室進行DAC 的測試,測試現場如圖11所示。通過改變DAC 的輸入,來改變接入DAC電流源電路輸出電流的大小,使DAC 輸出電壓相對應的改變。表1 為低4 位DAC 的測試數據表,由測試結果可以看出,低4 位DAC 在輸入偏置電流為3.73 uA 時,仍可得到合適的輸出,且精度誤差均小于7%,可見其精度好于4 mV。對用于細調的低4 位DAC 輸出數據進行線性處理,得到其DNL為?0.10~0.09 LSB,INL 為?0.01~0.18 LSB,均小于0.2 LSB,符合設計要求。將測試數據的輸入輸出傳輸曲線與理想的輸入輸出傳輸曲線進行對比,對比圖如圖12 所示。由測試數據可得此設計噪聲低,精度高,動態范圍大,各參數均符合設計的要求。因此,本文通過組合兩個4 位DAC,分別進行粗細閾值調節,來實現一個8 位DAC 閾值調節的方法是具有可行性的。

圖11 測試現場圖

圖12 低4 位DAC 理想和測試的輸入輸出傳輸曲線對比圖

表1 低4 位DAC 測試數據表

測試結果表明,本文的設計具有良好的線性,但也仍然存在誤差。經過分析,誤差產生的原因主要在偏置電路的結構設計上,形成電流源陣列的晶體管需要的偏置電流過小,測試時實現起來較難,會造成一定的誤差,可以通過優化和改進偏置電路的結構來設置合適的偏置電流,減小由這一原因帶來的誤差。

6 結 束 語

本文介紹了可適用于PSD 陣列探測器讀出ASIC芯片中的閾值產生單元模塊的設計與實現。利用0.18 um CMOS 工藝實現了該單元電路的原理設計、版圖設計、前后仿真和最終的芯片流片。并對流片成功的芯片進行了實驗室測試,結果表明其DAC 的積分非線性、微分非線性、輸出誤差、閾值范圍、噪聲等性能良好。該單元電路能夠為讀出ASIC 芯片內的甄別電路提供可調節的閾值電壓;通過高4 位DAC 結合低4 位DAC,實現粗細閾值的調節,達到較好的調節精度;并且版圖面積小,功耗低,易于集成。本文研究為后續VLAST中PSD 前端讀出ASIC 芯片的整體設計提供了重要技術保障,也為讀出ASIC 芯片中慢控模塊的設計積累了相關經驗。