某模塊SOC芯片失效分析及改進

向以鑫,張學新,張云

某模塊SOC芯片失效分析及改進

向以鑫,張學新,張云

(中國電子科技集團公司 第三十研究所,四川 成都 610041)

對某模塊在可靠性試驗中,出現核心功能失效的故障現象進行了研究。通過有限元仿真分析、金相切片分析結果,定位模塊故障原因為SOC芯片存在較大比例焊點開裂現象。針對焊點開裂的原因,采用SOC芯片底部填充膠加固的改進措施,建立對應的有限元仿真模型,進行模態計算、諧響應分析,校核了改進方案的可行性。并對加固后的模塊進行可靠性試驗、焊點切片分析,進一步驗證了模塊改進措施的有效性。這種對芯片底部填充膠加固、有限元仿真分析校核、試驗及切片驗證的設計方法,對同類型芯片焊點加固設計具有參考意義。

SOC芯片;底部填充膠;焊點開裂;諧響應分析

隨著電子技術的快速發展,電子產品不斷向小型化、輕量化方面發展,印制電路板集成度越來越高,促進印制板上的器件向著微型化方向發展。球珊陣列封裝(Ball Grid Array,BGA)是一種常見的IC(Integrated Circuit,集成電路)封裝形式,具有體積小、電性能強和散熱性能好的優勢。

在實際使用過程中發現,BGA封裝SOC(System on Chip,系統級芯片)等芯片會因焊點小、焊球匹配性等原因造成焊點出現應力集中情況,使其焊后芯片在長期使用過程中出現焊點連接失效問題[1]。夏卓杰等[2]探究有限元方法在無鉛焊點可靠性研究方面的不足及解決辦法,為IC封裝領域無鉛焊點可靠性的研究提供理論支撐。楊雪霞等[3]根據不同焊點形狀建立三種3D有限元模型,采用Input-G方法將加速度曲線作為數值模型的載荷輸入,對BGA封裝件在板級跌落沖擊載荷下的可靠性進行了分析。馮春苗等[4]為改善芯片焊點失效問題,采用底部填充技術,對芯片和線路板之間的空隙進行底部填充補強。秦蘇瓊等[5]根據芯片組裝的要求,討論了底部填充膠在使用中的工藝要求以及缺陷分析方法。姜健等[6]研究了芯片在長膠、短膠(中間)、短膠(四角)和無膠四種不同點膠方式下,芯片管腿上應力的大小。

本文針對模塊核心功能失效,建立失效分析和芯片底部填充膠有限元仿真模型,定位和解決模塊SOC芯片失效問題。

1 故障描述

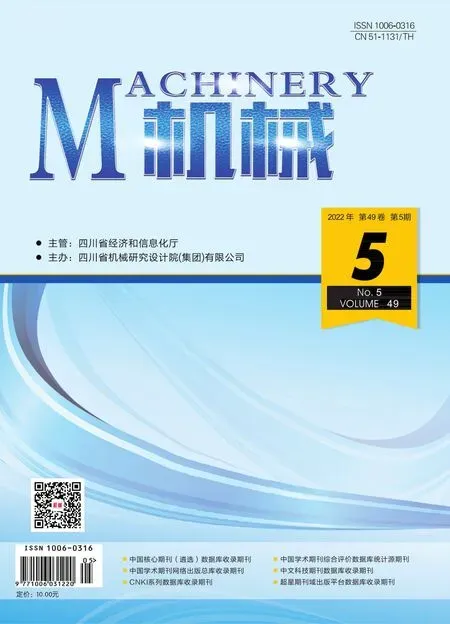

某型模塊完成生產后,抽取24個模塊開展可靠性試驗。在第8個周期高溫工作檢測點檢查時,出現5個模塊核心功能失效。現場查看模塊故障現象,均直觀顯示為測試項“模塊編號”或“自檢”失敗,發送測試指令,無法送達SOC芯片處理,重啟電源及恢復常溫后再次檢查,故障現象未消失。在故障模塊檢查過程中,按壓其SOC芯片等位置,故障現象消失。對部分故障模塊重新焊接SOC芯片后,問題消失。失效原因初步定位為SOC芯片焊點有開路。模塊外觀如圖1所示。

圖1 模塊外觀圖

2 模塊失效分析

2.1 有限元模型的建立

本文采用ANSYS Workbench軟件對模塊模態、諧響應進行仿真分析。

模型簡化:由于模塊印制板及元器件成分復雜,分析中對模型進行適當簡化處理,僅考慮關鍵部位質量較大器件及重要器件[7]。為快速定位故障原因,忽略芯片封裝引腳和接插件的插針的影響,芯片、器件均簡化為固體塊。

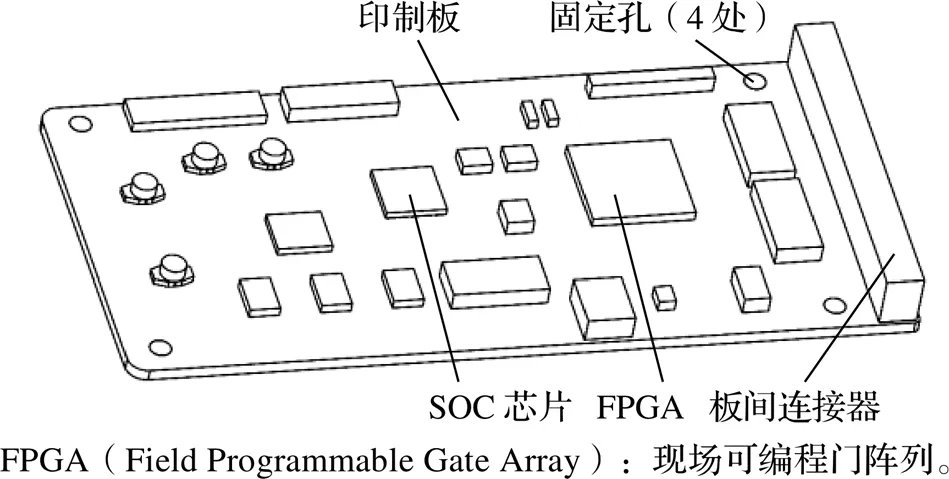

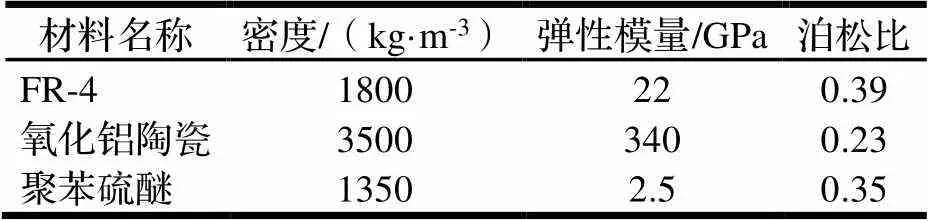

材料賦值:仿真模型中印制板材料為FR-4,固定安裝螺釘材料為不銹鋼,SOC芯片為陶瓷封裝材質,FPGA等芯片材料為塑料封裝外殼材質,板間連接器和部分接插件材料為聚苯硫醚,其余質量較大器件材料為工程塑料,主要材料的力學參數如表1所示。

表1 主要材料參數表

施加約束:對印制板上器件與印制板施加綁定接觸,安裝螺釘與印制板之間施加綁定接觸,4處安裝螺釘施加固定約束。

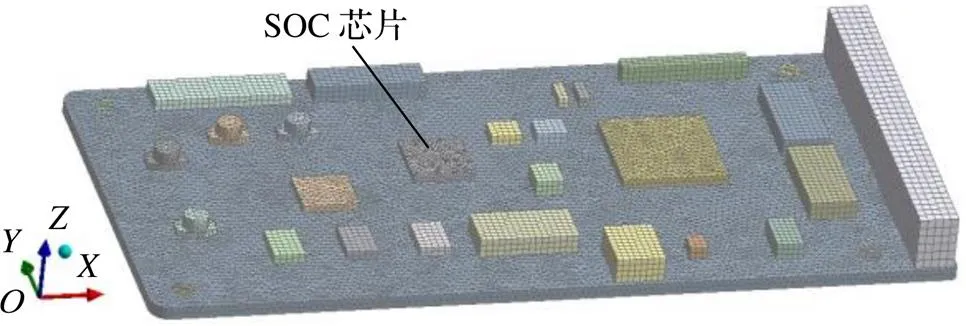

劃分網格:模塊有限元網格劃分節點數304781個,單元數178627個,網格模型及計算坐標系如圖2所示。

圖2 模塊有限元網格模型及坐標系

施加載荷:模塊可靠性試驗每個周期中的第12~18 h中環境溫度為50℃,需承受三個相互垂直軸向各30 min的振動應力,加速度載荷4.2,頻率范圍5~500 Hz。結合可靠性試驗中失效模塊出現的位置,分析發現所有失效模塊均為承受方向振動時出現故障,其余兩個方向模塊均未出現故障,因此,有限元模型只分析方向激勵載荷的影響。

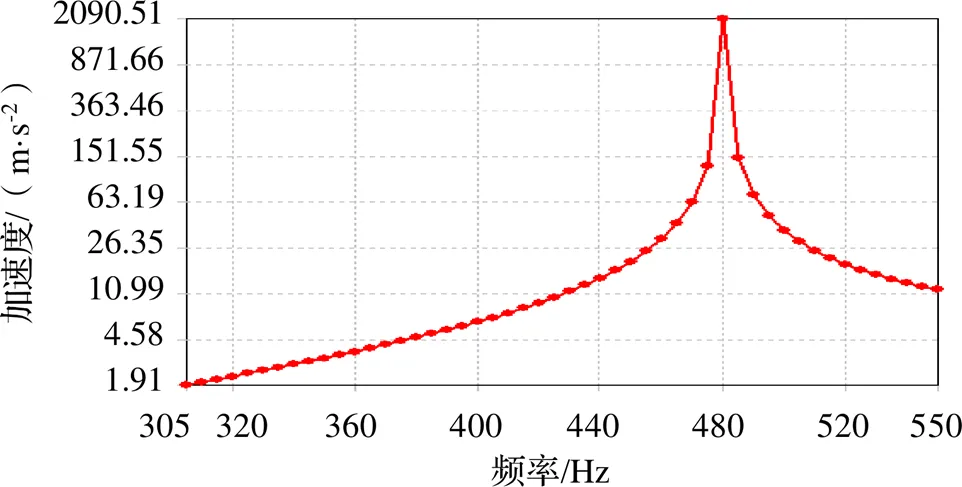

2.2 模態分析

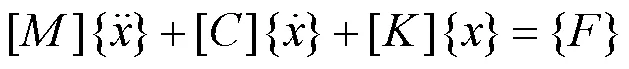

模態分析是一種確定結構振動特性的技術,是結構動力學分析的基礎,用于分析結構的自振頻率特性,包括固有頻率和振型及模態參與系數[8]。本文研究的模塊可以等效為一個多自由度線性系統,工作過程中承受裝甲環境的作用,模塊的動力學方程為:

進行無阻尼模態分析是經典的特征值問題,模塊此時的阻尼矩陣和激勵載荷均為零,位移為正弦函數,無阻尼簡諧振動的運動學方程可簡化為:

由式(2)可得特征方程為:

本文采用振型疊加法,使用Block Lanczos法提取特征值,計算模塊的固有頻率及相應的振型。考慮模塊工作頻率最高為500 Hz,計算時重點關注該模塊低于500 Hz的固有頻率值。

由計算結果可知,模塊低于500 Hz的固有頻率僅有1階固有頻率480.32 Hz,其模態振型如圖3所示。由圖3可知,當外部激勵的頻率與模塊固有頻率接近時,將引起模塊出現共振現象,模塊呈現中間彎曲變形,SOC芯片沿方向兩端焊點承受較大的拉伸形變,容易引起焊點出現結構破壞。

圖3 模塊1階模態振型

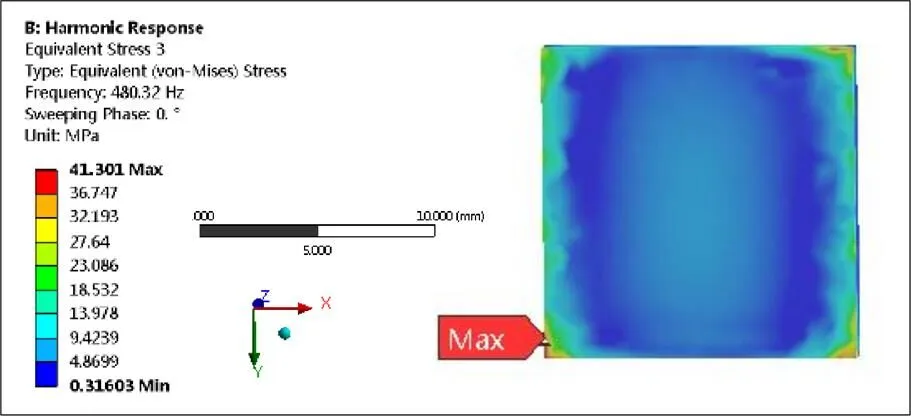

2.3 諧響應分析

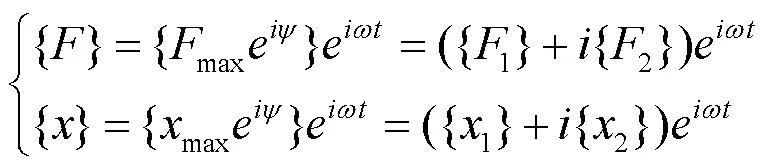

諧響應分析是一種確定結構在正弦(簡諧)激勵載荷作用下系統穩態響應的技術,用于分析結構在激勵載荷作用下的結構響應和不同頻率激勵載荷下的動態特性[8-9]。模塊諧響應分析的基本動力學方程見式(1),此時式中的{}矩陣和{}矩陣是簡諧的,有:

將式(4)求導代入式(1),整理得諧響應分析的運動方程為:

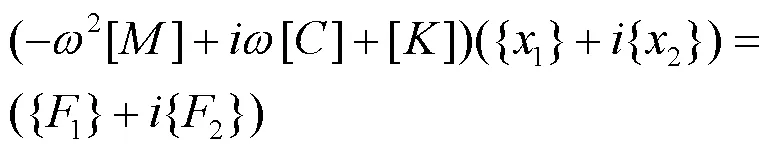

本文采用模態疊加法對模塊進行諧響應分析,響應頻率范圍結合模態分析結果取300~550 Hz,在固定約束上施加沿方向的加速度載荷,相位角0°,子步數50步。由仿真結果可得,SOC芯片中點位置的加速度-頻率曲線如圖4所示。模塊在1階固有頻率附近應力值最大,出現在SOC芯片焊點位置,如圖5所示。

由圖4、圖5可知,SOC芯片在模塊1階固有頻率480 Hz附近出現共振現象,此時SOC芯片加速度最大放大49.8倍,SOC芯片最大應力值出現在4個角上,為41.30 MPa,超出SOC芯片焊接材料Sn63Pb37在環境溫度50℃條件

下的許用應力值22.96 MPa[10],在此外部激勵下,焊點容易出現開裂。

圖4 SOC芯片在Z方向加速度-頻率響應曲線

圖5 SOC芯片焊點沿Z方向最大應力云圖

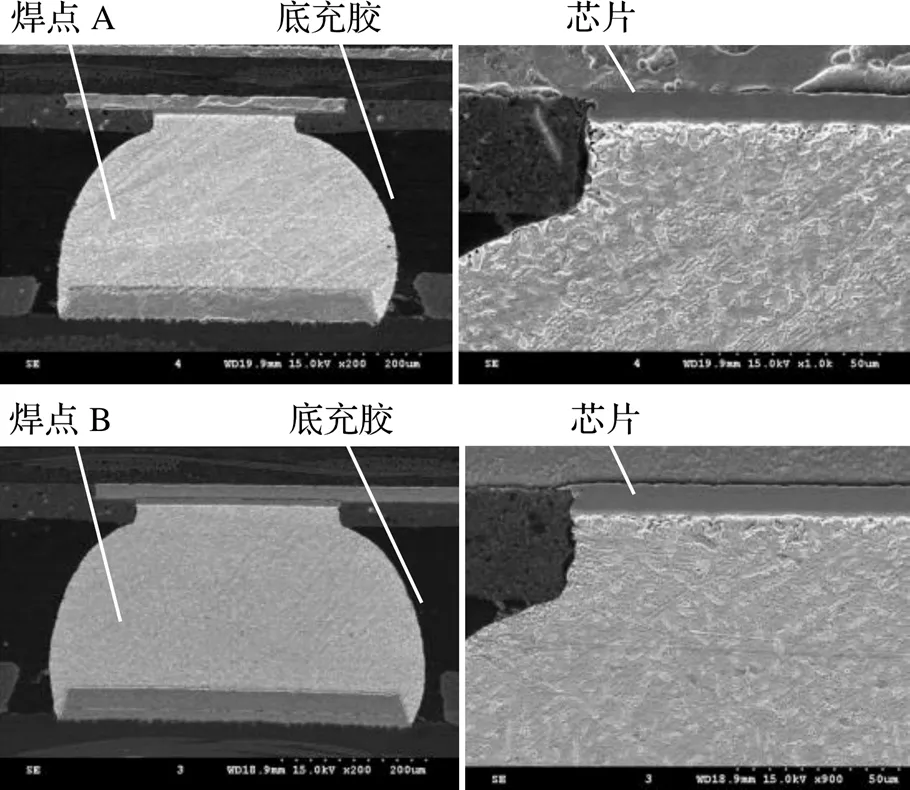

2.4 SOC芯片切片分析

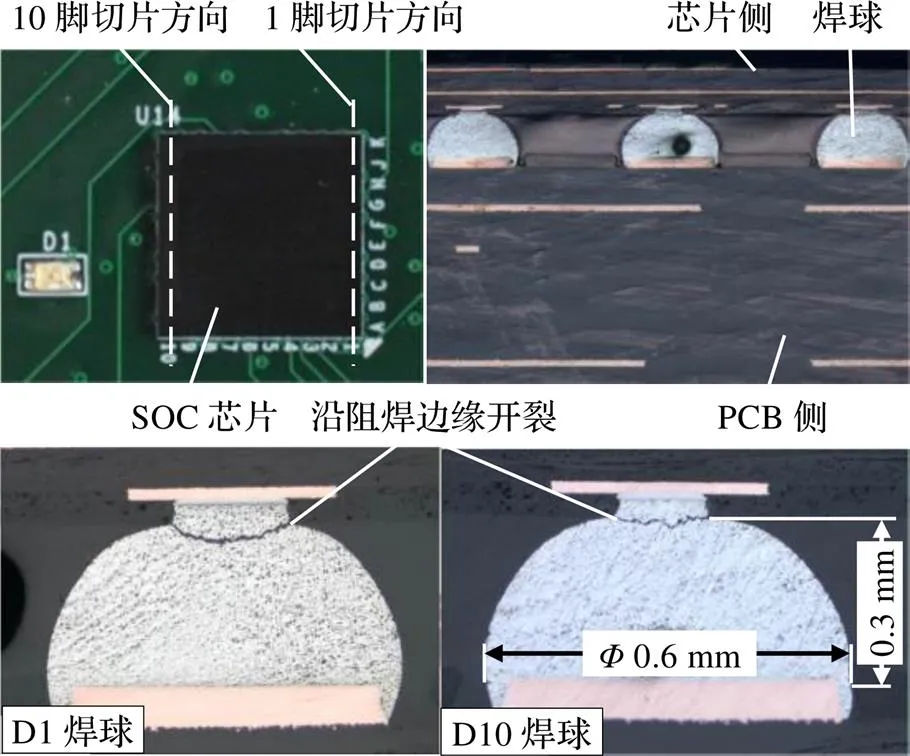

為判斷焊點是否開裂,將失效模塊送中國賽寶實驗室對SOC芯片焊球引腳沿軸方向進行剖片分析,如圖6所示,可知,SOC芯片焊球與芯片基板位置存在開裂情況。

圖6 失效SOC芯片切片分析結果

3 改進方案及驗證

3.1 改進方案

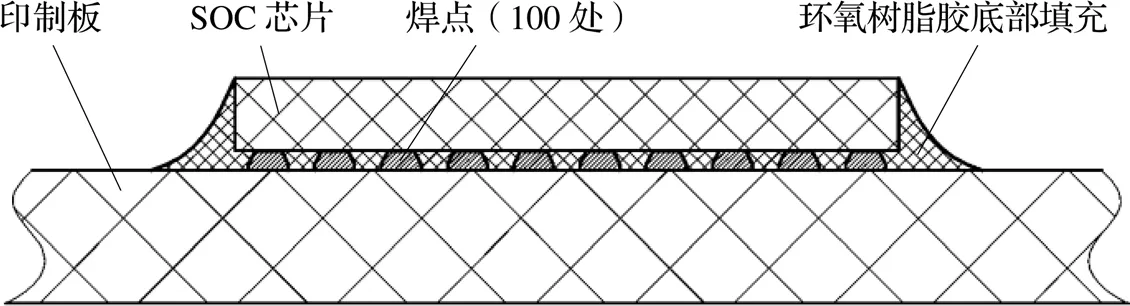

針對SOC芯片焊點在方向振動應力值超出焊料許用應力值、導致焊點開裂的現象,同時改善芯片焊點存在變截面的設計弱點,在SOC芯片底部填充某型環氧樹脂膠進行加固,施膠工藝為L形填充,如圖7所示。

圖7 SOC芯片填充加固示意圖

3.2 改進方案仿真分析

模型簡化:根據模塊失效原因為SOC芯片焊點有開路,對SOC芯片有限元模型進行合理細化,結合切片分析焊點形狀,在SOC芯片和印制板之間建立100個碗型焊點,按照改進方案建立模塊SOC芯片底部填充加固后的模型。

新增材料賦值:環氧樹脂膠密度1.2 g/cm3,彈性模量2.6 GPa,泊松比0.38。

施加約束:對印制板上器件與印制板施加綁定接觸,SOC芯片焊點與印制板及SOC芯片施加綁定接觸,環氧樹脂膠與焊點、芯片及印制板施加綁定接觸,安裝螺釘與印制板之間施加綁定接觸,4處安裝螺釘施加固定約束。

劃分網格:對焊點和底部填充環氧樹脂膠處的網格進行合理控制,網格單元尺寸0.1 mm,模塊有限元網格劃分節點數834487個,單元數512279個,網格模型如圖8所示。

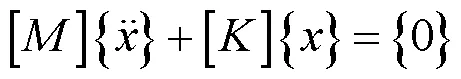

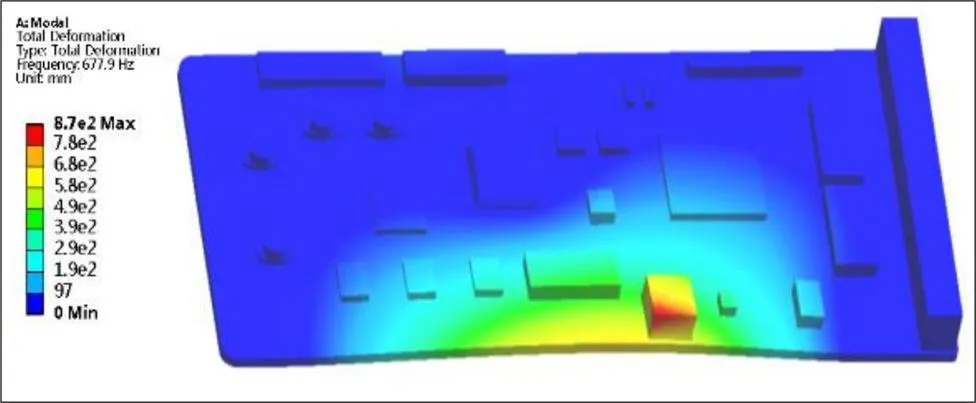

模態分析:對模塊前6階固有頻率進行仿真分析,模塊1階固有頻率為677.9 Hz、模態振型如圖9所示,超出工作頻率500 Hz的范圍,模塊不易發生共振。

圖8 SOC芯片填充加固有限元網格模型

圖9 模塊1階模態振型

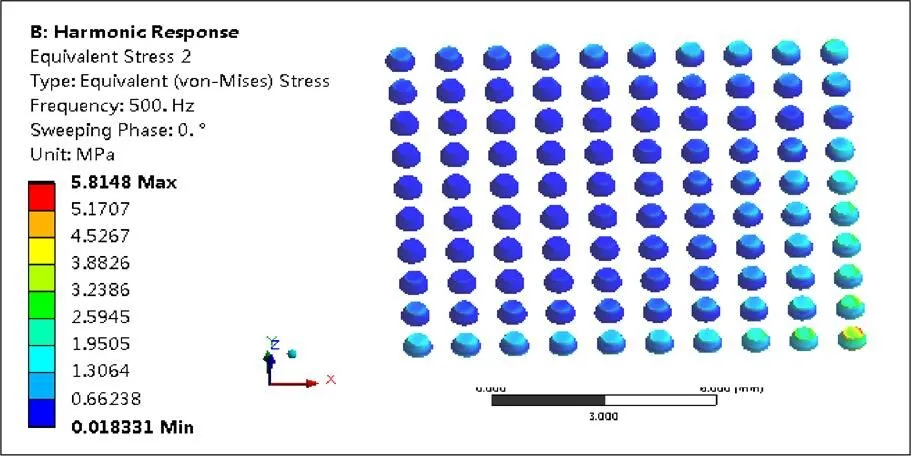

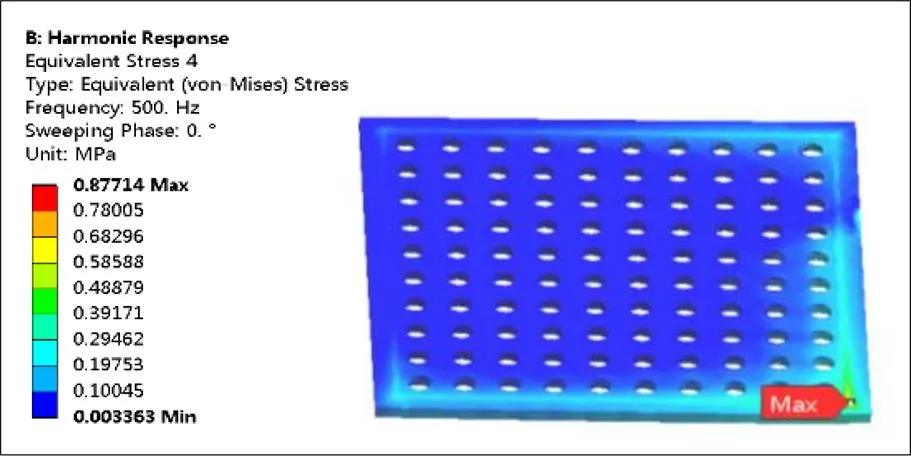

諧響應分析:響應頻率取300~550 Hz,子步數為50步。由仿真結果可知,模塊在500 Hz內沒有共振點,SOC芯片中點位置的加速度曲線如圖10所示。模塊SOC芯片焊點在工作頻率500 Hz出現最大應力值,如圖11所示。底部填充環氧樹脂膠在工作頻率500 Hz出現最大應力值,如圖12所示。

圖10 SOC芯片在Z方向加速度-頻率響應曲線

由圖10~12可知,SOC芯片在模塊工作頻率范圍內未出現共振頻率,焊點最大應力值為5.81 MPa,遠低于焊接材料Sn63Pb37的許用應力值,環氧樹脂膠最大應力值為0.88 MPa,遠低于材料的許用應力值,SOC芯片底部填充環氧樹脂膠后焊點不會開裂。

圖11 SOC芯片焊點沿Z方向最大應力云圖

圖12 環氧樹脂膠沿Z方向最大應力云圖

3.3 改進方案試驗驗證

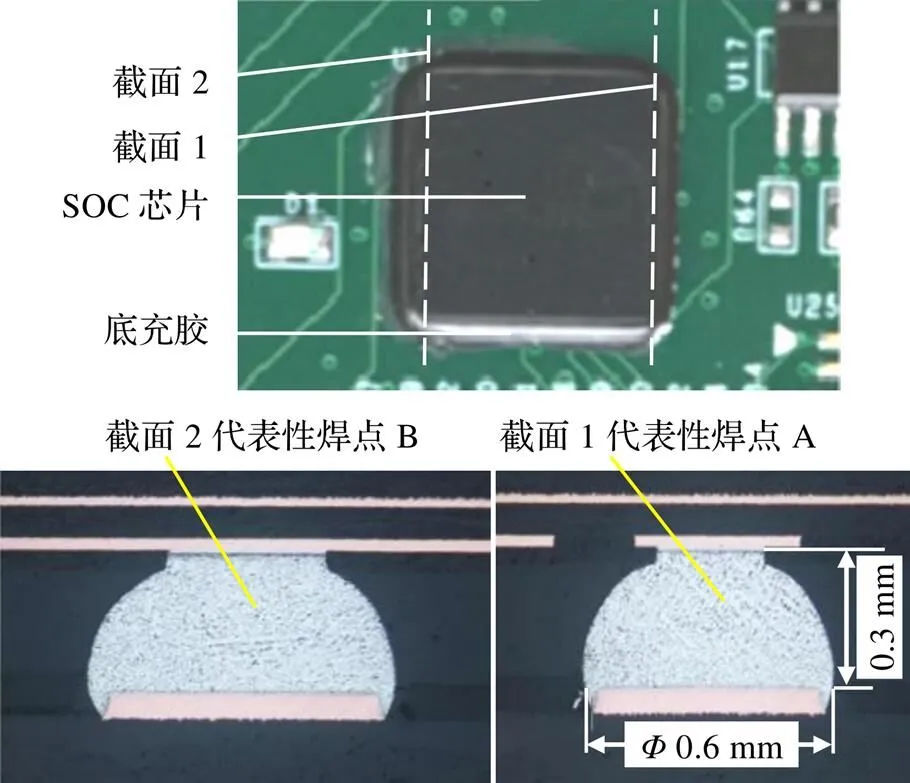

重新抽取24個模塊,根據改進方案對模塊SOC芯片進行填膠加固后,保持原有裝夾方式和試驗方法對模塊進行12個周期的可靠性試驗測試。模塊均通過了可靠性試驗的驗證。為排查焊點是存在潛在裂紋,抽取可靠性試驗后的模塊送至中國賽寶實驗室對SOC芯片截面1和截面2進行剖片分析,由圖13、圖14切片結果及切片分析報告可知,SOC芯片焊點截面未出現開裂現象,驗證了改進方案合理、可行。

圖13 SOC芯片切片截面位置示意圖

圖14 SOC芯片代表性焊點切片分析結果

4 結束語

以某裝甲模塊SOC芯片失效為對象,利用有限元分析得出,SOC芯片失效原因為在工作頻率范圍內芯片出現共振現象,導致焊點處應力值超出焊點材料許用應力值,出現焊點開裂現象。采用SOC芯片底部填充環氧樹脂膠的加固方式,降低芯片焊點受到機械應力的影響。

經過仿真校核和試驗驗證了結構改進措施可行有效,為芯片的加固設計提供有效的參考依據。

[1]何燕春,袁莓婷,米曦宇. BGA類元件點膠工藝技術研究[J]. 學術研究,2020(3):156,159.

[2]夏卓杰,張亮,熊明月,等. 有限元數值模擬在BGA/QFP/ CCGA器件焊點可靠性研究中的應用[J]. 電子與封裝,2020,20(2):1-7.

[3]楊雪霞,肖革勝,樹學峰. 板級跌落沖擊載荷下無鉛焊點形狀對BGA封裝可靠性的影響[J]. 振動與沖擊,2013,32(1):104-107.

[4]馮春苗,張欲欣,付博彬. 軍用倒裝焊器件底部填充膠選型及驗證方法討論[J]. 電子與封裝,2020,20(5):1-4.

[5]秦蘇瓊,王志,吳淑杰,等. 芯片底部填充膠的應用探討[J]. 電子工業專用設備,2017(265):8-11.

[6]姜健,醋強一,張豐華,等. 元器件點膠方式對芯片可靠性的影響[J]. 機械研究與應用,2018,31(2):12-13,17.

[7]張云,吳圣陶,曾柯杰,等. 某電子設備隨機振動疲勞壽命仿真分析[J]. 電子機械工程,2016,32(6):25-28.

[8]鄭彬,鄂靖元. 發動機連桿有限元模態分析及諧響應分析[J]. 機械設計,2020,37(1):98-101.

[9]龍慎文,王優強,周亞博,等. 基于諧響應分析的艉軸承動態特性研究及靈敏度分析[J]. 機械傳動,2019,43(5):101-105.

[10]黃春躍,周德儉,李春泉. CCGA焊點熱循環加載條件下應力應變有限元分析[J]. 桂林電子工業學院學報,2001,21(3):22-28.

Failure Analysis and Improvement of a Module SOC Chip

XIANG Yixin,ZHANG Xuexin,ZHANG Yun

(The 30th Research Institute, CETC, Chengdu 610041, China)

This paper analyzed the reason why the core function of a module failed in a reliability test. Finite element simulation and cross section analysis were adopted to determine reason of the failure which was proven to be a large proportion of solder joint cracking on soc chip. Based on causes of the solder joint cracking, we adopted underfill reinforcement for soc chip, set up corresponding finite element simulation model and made modal calculation and harmonic response analysis to verify feasibility of the improvement plan. In addition, effectiveness of the structural improvement measures was further approved by reliability tests for the reinforced module and solder joint section analysis. This design method with underfill reinforcement, finite element simulation analysis verification and test as well as section verification has reference significance for solder joint reinforcement design of the same type of chips.

SOC chip;underfill reinforcement;solder joint cracking;harmonic response analysis

TN607

A

10.3969/j.issn.1006-0316.2022.05.004

1006-0316 (2022) 05-0022-06

2022-01-19

向以鑫(1989-),男,重慶人,碩士研究生,工程師,主要從事電子設備結構設計工作,E-mail:740799051@qq.com。