基于FPGA的機載光電觀瞄成像裝置系統設計

康亞林,郭 杰,吳 迪,肖明艷,傅 霖

(云南師范大學物理與電子信息學院,昆明 650500)

0 引言

機載光電觀瞄成像裝置是一種安裝在航空器上,并具有導航、目標搜索、瞄準以及穩定跟蹤等功能的光電系統,相較于普通成像裝置,工業航空觀瞄成像裝置往往面臨著更加復雜和更加嚴酷的工作環境,圖像采集系統的性能要求越來越高[1]。早期的工業航空觀瞄成像裝置很多都是采用CCD 圖像傳感器,由于受到半導體制造工藝水平的限制,CMOS圖像傳感器的性能指標均低于CCD 圖像傳感器的性能指標。但是近年來,CMOS 圖像傳感器以其開發周期短、功耗小,尤其是高幀頻高分辨率的特點成功進軍工業、監控、航天等領域[2]。電子元器件國產化替代對國防和信息安全建設具有重要意義,特別是依賴進口的航空航天裝備領域。

本文采用國產CMOS 圖像傳感器HT50A、國產可編程邏輯器件T120,設計了機載光電觀瞄成像裝置系統的硬件電路,并編寫了控制軟件。

1 系統總體設計

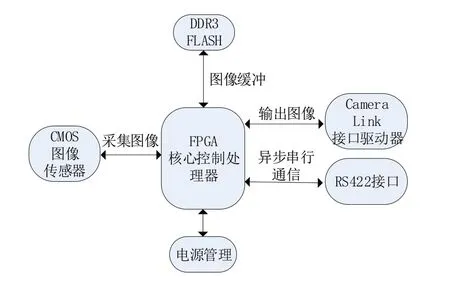

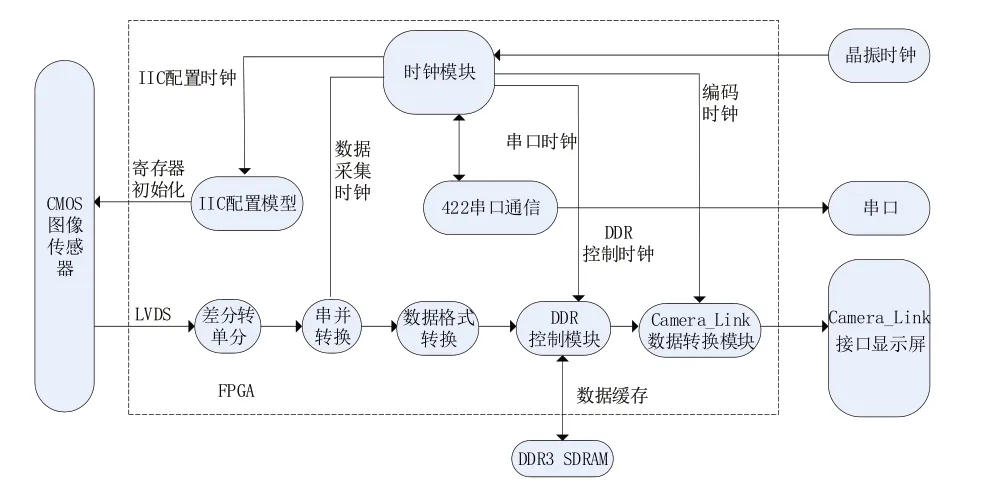

機載光電觀瞄成像裝置系統主要包括三部分:圖像傳感器模塊、信息處理模塊和Camera-Link接口模塊。系統結構如圖1所示。

圖1 系統結構框圖

2 硬件電路設計

2.1 圖像傳感器模塊

采用海圖微電子有限公司的HT50A 圖像傳感器。HT50A 是一款2/3 型5 兆像素高分辨率CMOS圖像傳感器,在2464(H)*2048(V)的全分辨率下,幀速率高達61.9 fps。HT50A 圖像傳感器分別需要用到數字電源1.2 V、模擬電源3.3 V、I/O 數字電源1.8 V。注意供電的電源要進行充分的解耦,防止噪聲干擾[3]。設計的時候數字部分電源和模擬部分電源要分開。電源芯片選用線性穩壓器LDO,靜態電流小、電壓穩定、輸出紋波小、負載響應快,最重要的是外圍電路簡單。

CMOS圖像傳感器的快門模式由系統所使用的傳感器特性決定,主要分為全局快門和卷簾快門兩種模式[4]。全局快門同時曝光傳感器網格中的所有像素,因此最終數字圖像的每個像素都是在同一時刻捕獲的。卷簾式快門在第一行曝光結束后,立即開始讀出數據,數據完全讀出后,下一行開始讀出數據。因此卷簾快門的第一行和最后一行像素的捕獲之間存在時間差,這意味會發生由于使用卷簾快門而導致的移動物體或場景的圖像失真或模糊。全局快門傳感器通常比卷簾快門傳感器尺寸更大、更感光。

本文選用的這款傳感器具有全局快門像素,高分辨率ADC和高速讀數。滿足智能交通系統、機器視覺和工業檢測等應用中的高性能和高分辨率要求。

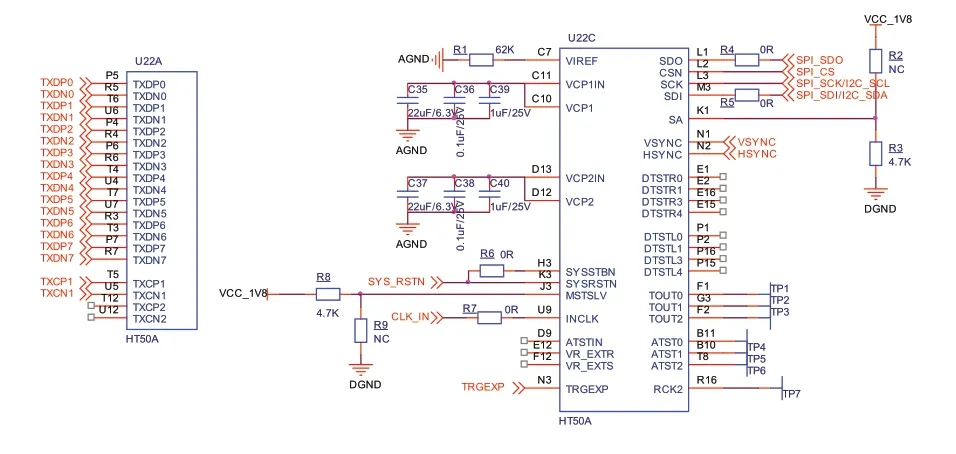

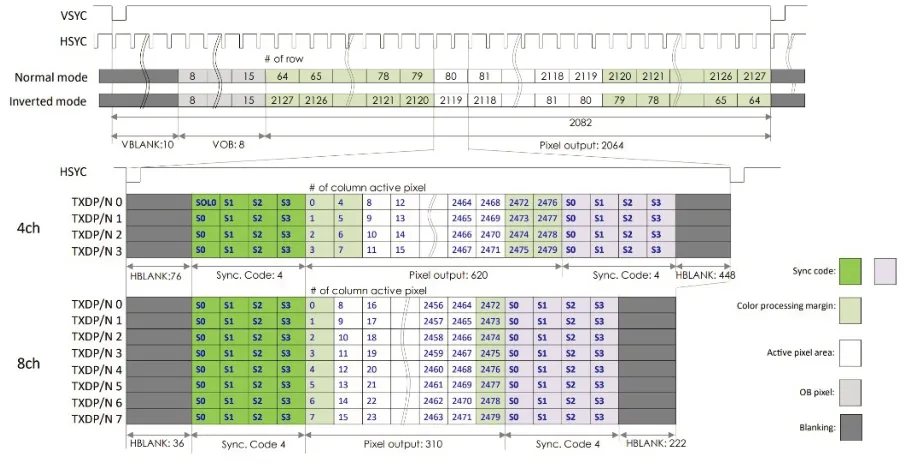

如圖2所示,TXDN0/TXDP0-TXDN7/TXDP7是HT50A的8對LVDS信號通道;TXCP1/TXCN1是隨同8 對信號數據的時鐘,即CMOS 輸出的圖像數據和時鐘信號;HSYNC 和VSYNC 是CMOS輸出的行場信號;I2C_SCL、I2C_SDA 是I2C 配置圖像傳感器所需要的信號。

圖2 圖像傳感器硬件電路圖

2.2 Camera-Link接口模塊

Camera-Link 接口模塊主要包括一個驅動器和一個接收器。接收器一共需要接收包括1 路LVDS 時鐘信號和4 路LVDS 數據信號,然后將傳輸的圖像數據流轉換成28 位的CMOS/TTL 并行數據和1 位時鐘信號[5]。驅動器總共需要驅動5路LVDS數據流,其中這5路LVDS數據流包括1路專用的LVDS時鐘信號傳輸通道和以7∶1方式串行化的4路LVDS 數據流。因此,驅動器接收端只需要接受28 位單端的數據信號和1 位單端的時鐘信號。但是這樣就會占用FPGA的大量IO 管腳和布線資源,不利于機載光電觀瞄成像裝置的低成本和集成化。基于此,本文以FPGA 作為主控芯片,利用FPGA 內部資源OSERDES 實現Camera-Link 并串轉換模塊。值得注意的是在差分信號之間需要100 Ω 的差分阻抗匹配設置。

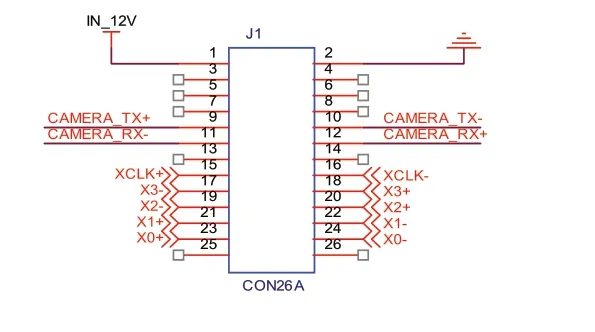

根據實際應用場景使用要求的不同,視頻傳輸模式包括以下三種配置模式:Full 模式、Medium 模式和Base 模式。在Base 傳輸模式下,發送器可以達到在每一個像素時鐘里發送24 bits的圖像數據和4 bits 的圖像使能信號。Base 模式的最大傳輸速度為2.0 Gb/S @ 85 MHz 。在Medium 傳輸模式下,發送器能夠發送36 bits 的圖像數據和4 bits 的圖像使能信號在每一個像素時鐘里。Medium 模式的最大傳輸速度為4.8 Gb/S @ 85 MHz 。在Full 傳輸模式下,發送器可以發送64 bits 的圖像數據和4 bits 的圖像使能信號在每一個像素時鐘。Full模式的最大傳輸速度為5.4 Gb/S@85 MHz。需要根據觀瞄成像裝置系統輸出的數據量的大小來決定使用哪一種配置的傳輸模式,本文所選用的CMOS 圖像傳感器的型號為HT50A,在Normal 工作模式下,本次設計寄存器配置的輸出數據位寬12 bit,輸出數據格式為RAW 格式,圖像總像素點為2464*2048,輸出圖像大小為1024*768,幀頻可選擇為30幀每秒或60幀每秒,選擇8通道輸出,像素時鐘頻率為78.5 MHz,輸出圖像數據量為225 Mbps,故對于圖像視頻數據流的接收,選擇Base模式即可滿足。硬件接口如圖3所示。

圖3 Camera-Link接口連接硬件電路圖

2.3 信息處理模塊

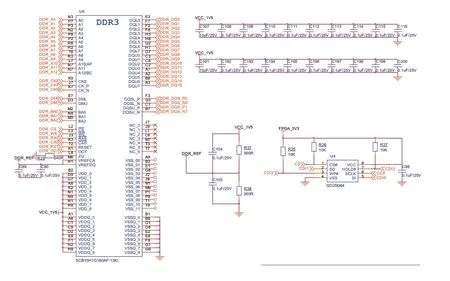

信息處理模塊架構為FPGA+DDR3+FLASH。現場可編程門陣列FPGA為易靈思科技有限公司的T120。DDR3 存儲器為西安紫光國芯半導體有限公司的SCB5H1G160AF-13KI。FLASH 為北京兆易創新科技股份有限公司的GD25Q64。

相對于DSP 來說,FPGA 片內有大量的邏輯門和觸發器,硬件集成度高、規模大、運算效率高;軟件數據處理速度快,可以實現更復雜的時序邏輯設計,并進行多次重復程序編程。

信息處理模塊主要需要1.2 V、1.8 V、1.5 V和3.3 V 供電。選用DC-DC 開關穩壓器,經濾波后得到的電壓干凈、效率高、帶負載能力強、瞬態反應比較快。

硬件電路圖如圖4和圖5所示。

圖4 FPGA模塊硬件原理圖

圖5 DDR+FLASH模塊硬件電路圖

圖6 頂層設計結構圖

3 軟件設計

3.1 I2C配置模塊

在本次系統設計中,通過FPGA 內部分頻器產生時鐘(SCLK),輸入到圖像傳感器CMOS以便可以進行數據同步傳輸,圖像數據(SDATA)在FPGA 與CMOS 圖像傳感器之間進行雙向傳輸,同時調試各種參數。配置模式選擇主從模式,即配置CMOS 圖像傳感器為從設備,FPGA 為主設備。I2C 控制模塊主要是應用處理器向圖像傳感器中的指定寄存器寫入指定數據,同時應用處理器從圖像傳感器中讀取某些控制和狀態數據。HT50A 通過I2C 通信協議接口配置內部寄存器,對其進行初始化操作[6]。表1為部分寄存器地址和設置值。

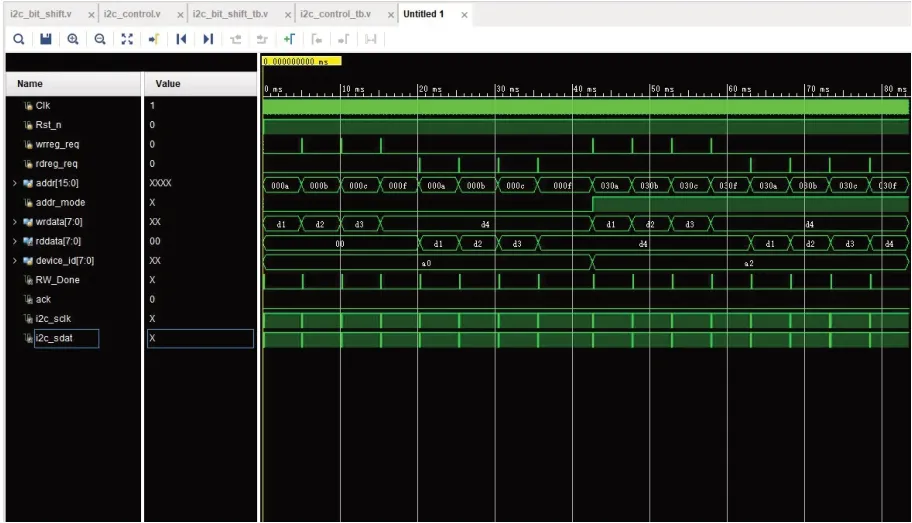

配置的時序圖如圖7 所示,圖8 是I2C 總線的時序仿真圖,仿真結果完全符合HT50A 手冊上的I2C通信接口寫時序圖。

圖8 I2 C總線仿真時序圖

3.2 DDR控制模塊

經過串并轉換模塊輸出的圖像數據需要存儲在DDR3 SDRAM 芯片中,因此就需要設計DDR 控制模塊用來實現對DDR3 的讀寫操作,如圖9所示。在本設計系統中,為了進一步降低軟件開發難度,增加設計系統的穩定性,FPGA與DDR3進行圖像數據信息交互所需接口信號是通過調用IP 核產生的。DDR 控制單元模塊設計通過直接例化MIG 生成新的時鐘單元模塊和DDR 核,wr_ddr3_fifo 模塊設計用來對DDR 進行寫操作,rd_ddr3_fifo 模塊設計用來對DDR 進行讀操作。用戶邏輯首先將圖像數據寫入到數據FIFO 中,接著再將命令信息寫入到命令FIF0中,這種寫入圖像信息的方式被稱為DDR 寫操作[7]。用戶邏輯要先將命令信息寫入到命令FIF0 中,然后才能將圖像數據讀出來,這種讀出圖像數據的方式被稱為DDR 讀操作。因此DDR 在進行讀操作時,它的地址必須要和寫操作的地址保持一致。

圖9 DDR讀寫控制流程

3.3 串口通信模塊

串口通信模塊主要用于設置機載光電觀瞄成像裝置的控制參數,主要包括自動曝光、對比度和增益等[8]。

波特率產生器:即需要產生一個時鐘頻率與對應波特率時鐘頻率相同的時鐘信號。例如:當選擇系統時鐘為50 MHz、波特率為115200 bp時,此時波特率產生器需要產生一個模為434的計數器。

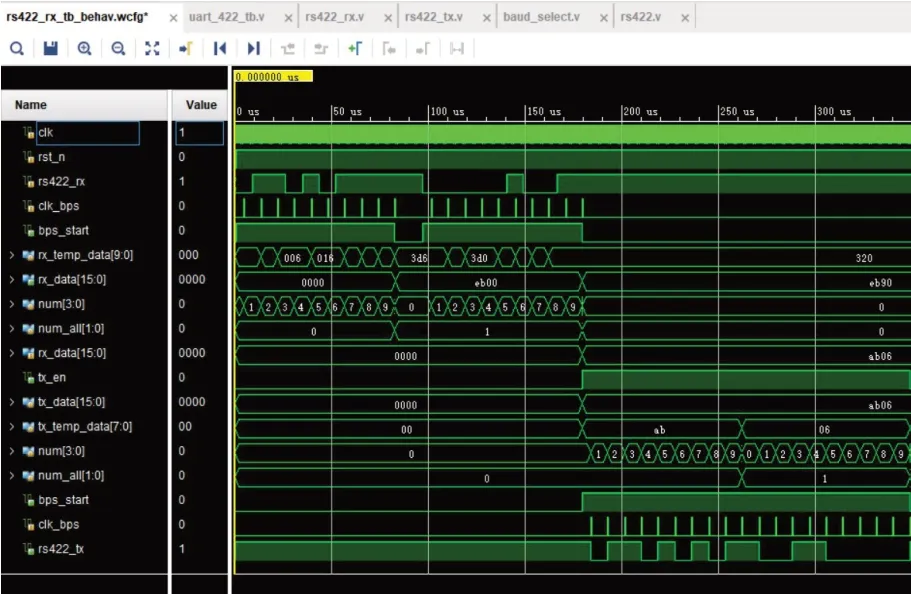

422通訊:以一位低電平標志開始,傳輸八位數據位,然后以一位高電平標志結束。它的發送模塊和接收模塊可以選擇共用一個波特率產生器。

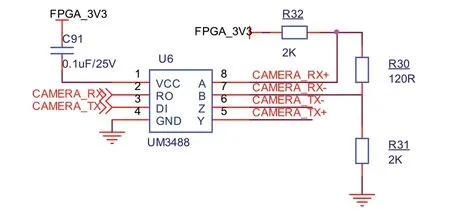

串口通信的硬件原理圖如圖10 所示,仿真時序圖如圖11所示。

圖10 通訊模塊硬件電路圖

圖11 422通信仿真時序圖

3.4 圖像接收與輸出模塊

FPGA 采集到所需要的圖像數據后,首先要在其內部的RAM 中緩沖一下再進行輸出,由于數據量很大,為了防止出現數據錯亂,影響數據傳輸的準確性,故需要進入DDR3進行數據緩沖,最后通過Camera-Link 端口傳遞圖像數據到顯示屏成像。

CMOS圖像傳感器的圖像數據輸出時序如圖12所示,當幀同步信號(VSYC)電平位低時,正常輸出數據,即VSYC默認高電平有效。

圖12 圖像傳感器數據(LVDS)輸出時序圖

4 圖像測試

利用DALSA 圖像采集卡來采集輸出的圖像,通過圖像采集軟件可以明顯觀察到此觀瞄成像裝置系統的幀頻為30 fps 和60 fps,輸出圖像的分辨率大小為1024*768,可實時觀察到圖像并且無任何卡頓。如圖13和圖14所示。

圖13 分辨率1024*768(30 fps)

圖14 分辨率1024*768(60 fps)

通過以上的圖片測試,我們可以看出:本次基于FPGA的機載光學觀瞄成像裝置系統設計是可行的,通過驗證在圖像傳感器支持的像素大小和幀率范圍,此次設計輸出圖像大小和幀率可通過寄存器的配置進行調整,同時也可以進一步加入圖像處理算法來增強圖像質量,具有較高的實用性,滿足現實的需求。

5 結語

本文設計的基于FPGA的機載光電觀瞄成像裝置系統,以可編程邏輯器件FPGA作為核心控制器,通過I2C 總線協議配置圖像傳感器HT50A的寄存器,FPGA 通過同步時鐘信號(包括幀同步信號、行同步信號,以及像素時鐘信號)能夠準確地采集到sensor_data 口輸出的數據,然后將采集到的圖像數據先在DDR3內進行數據緩存后再通過Camera-Link 端口傳遞到顯示屏成像。通過測試驗證了所設計系統的硬件可行性,系統穩定可靠,設計符合預期目標。機載光電觀瞄成像裝置系統的軟件配置都是通過FPGA進行的,后期也可以將圖像處理算法移植到該機載光電觀瞄成像裝置系統軟件中,如邊緣檢測算法、圖像濾波算法、自動白平衡算法等,具有比較高的實用性。