一種基于流水線的SpaceWire路由器研究

李 瀟 龔龍慶 田 衛 南 希

摘 要:SpaceWire路由器是面向Spacewire總線網路互聯的設計,它解決了SpaceWire總線只能點對點連接的問題,并提供了通用標準接口和規范進行SpaceWire網絡的建立。提出了一種基于流水線技術的SpaceWire路由器,它是利用FPGA設計來實現無阻塞的交換矩陣,并且利用流水線原理提高系統的并行工作速度,以提高SpaceWire路由器的交換速度。目前經過驗證的速度已達200 Mb/s,且正在不斷改進中。

關鍵詞:SpaceWire路由器;流水線;FPGA;無阻塞交換網絡;傳輸速度

中圖分類號:TN915文獻標識碼:A

文章編號:1004-373X(2009)03-090-03

Study of SpaceWire Router Based on Pipeline

LI Xiao,GONG Longqing,TIAN Wei,NAN Xi

(Xi′an Micro-electronic Technology Institute,Xi′an,710054,China)

Abstract:SpaceWire router is a design for SpaceWire bus network,it has solved the problem that SpaceWire bus only can connect by point to point,and has provided an universal standard interface and criterion to establish the SpaceWire network.This article introduces a SpaceWire router based on pipelining technique,it achieves a non-blocking switch based on FPGA,and uses pipelining technique to improve the speed of parallel work,which advances the transmission rate of SpaceWire router.The rate has been proved is reach 200 Mb/s,and it is improving now.

Keywords:SpaceWire router;pipeline;FPGA;non-blocking switch;transmission rate

近年來,隨著SpaceWire總線技術在航天航空領域的不斷應用,SpaceWire路由器在理論和技術應用方面也得到了飛速發展。國外,歐洲航天局(ESA)已經將速度為200 Mb/s抗輻射的SpaceWire路由器應用到ESA的航天任務中。國內,目前對SpaceWire路由器的研究還處于初級階段,設計的SpaceWire路由器最高速度也只能達到100 Mb/s。為了提高路由器的傳輸速度,這里提出了一種基于流水線技術的SpaceWire路由器。

1 SpaceWire路由器概述

SpaceWire路由器由一定數量鏈接接口單元和路由單元構成。接口單元主要負責連接各SpaceWire接點,路由單元負責數據的路由交換。

1.1 SpaceWire數據鏈路層接口單元

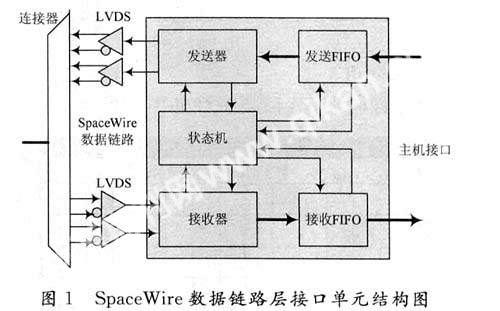

SpaceWire數據鏈路接口主要由連接器、LVDS驅動器、編碼器、譯碼器、狀態機、收發FIFO以及主機接口組成,其結構如圖1所示。

發送器接收來自發送FIFO的數據,使用DS編碼技術編碼這些數據并且進行發送。

接收器負責解碼DS(Din和Sin)信號產生N-Chars字符序列(data,EOP,EEP),這些字符序列通過接收FIFO傳送給主機系統。

FIFO的使用簡化了數據鏈路與主機系統之間的接口。在系統復位以后,發送和接收FIFO都是空的。在鏈路連接建立以后,如果接收到FCT表明鏈路另一端允許向它發送數據,那么被寫入發送FIFO的數據將被發送。當接收FIFO內仍然有可用空間時,接收FIFO能夠接收數據。主機系統從接收FIFO中讀取數據。在FIFO全空或全滿以前,FIFO的半空或半滿標志會觸發處理器干預對FIFO的讀寫操作。這種機制能夠控制通過鏈路的數據流,使數據鏈路接口保持高速數據吞吐。

狀態機用來負責控制接口單元的整體操作,它會提供鏈路初始化,普通操作和錯誤服務。

1.2 SpaceWire路由器單元

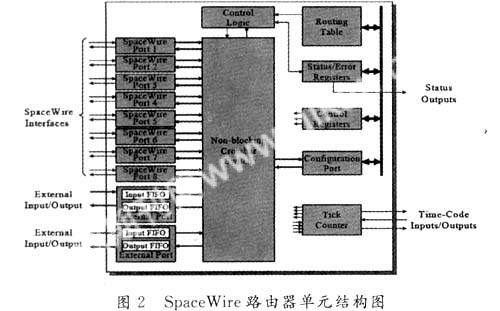

為了簡化基于SpaceWire的通訊系統的復雜度,很重要的就是對SpaceWire路由單元的設計。如圖2所示,在圖中所設計的SpaceWire路由器中包括8個SpaceWire端口,即2個外部端口、1個內部配置端口、路由表、控制寄存器、狀態/錯誤寄存器、控制邏輯、無阻塞交互開關等。

低延遲、蟲洞路由和無阻塞交換開關使數據包能夠到達任意一個SpaceWire端口和外部端口,或者也可以由配置端口直接訪問任意一個SpaceWire端口和外部端口。所設計SpaceWire端口完全支持SpaceWire標準,提供高速的、雙向的通訊。每個外部端口包括一個發送FIFO和一個接收FIFO,可以發送接收字符和包結束標志。

Time-code端口會和計數器一起被提供用來方便Time-code的傳播。當一個有效的Time-code到達一個路由端口時,它也會被發送到其他SpaceWire端口,一個TICK_OUT信號會在Time-code端口被產生。路由器可以用Time-code端口提供的TICK_IN信號做為Time-code的操作管理。

配置端口可以配置任何SpaceWire端口和外部端口。它包括可以控制SpaceWire端口、外部端口和交換開關的寄存器。配置端口為各種端口和交換開關都設置了狀態寄存器。用配置端口的讀命令可以讀這些寄存器,從而來讀出路由器的狀態和錯誤信息,而且一些狀態引腳上的狀態和錯誤信息可以被選擇輸出。

路由表可以通過配置端口來訪問。邏輯地址端口映射和優先位都可以在路由表中進行設置,路由表常常用來控制組適應路由和交互開關中的優先仲裁。

1.3 蟲洞路由

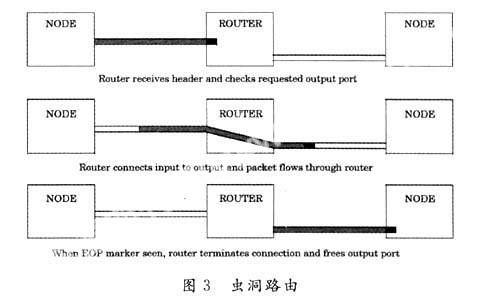

SpaceWire路由器是基于蟲洞路由上進行設計的。蟲洞路由是包路由的一種形式。每一個包的包頭包含著目的地的地址信息。每當有一個包到達路由器時,它就立即檢測這個包的目的地址,然后按照該地址轉發這個包到相應的輸出端口。如果要求的輸出端口是“空閑”(free)狀態,則這個包會被立即轉發到這個輸出端口。這時,該端口就會被打上“忙”(busy)狀態標記,直到這個包的最后一個字符即“包尾”(EOP)通過路由器轉發出去。

蟲洞路由如圖3所示,圖中一個包從一個節點發出,通過路由器到達另外一個節點。包頭標記為黑色,其余部分為灰色。路由器負責在輸入端口和空閑的輸出端口之間建立連接,當檢測到EOP或EEP時,斷開連接,釋放輸出端口為空閑狀態,準備接收其他端口來的包。輸出端口忙時,輸入端口阻塞輸入包,直到其空閑。通過輸入端口相遠節點發送FCT來實現,直到輸出端口空閑時,路由器才取消阻塞。以上是蟲洞路由和流量控制之間的關系。

2 基于流水線的SpaceWire路由器

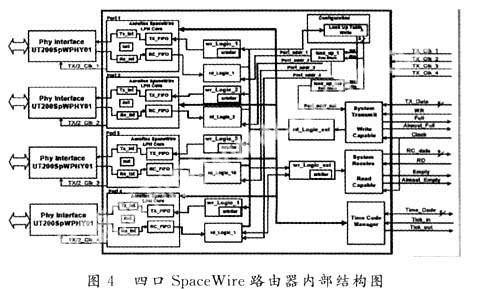

SpaceWire路由器將數據從輸入端傳遞到輸出端的過程一般需要進過三個階段:首先,從輸入端讀數據,將數據包中包頭所包含的目標地址發送給路由查找表;再次,由路由查找表對目標地址進行查找,確定該數據包所要發送的輸出端;最后,將數據包發送到目標地址所指的輸出端。具體結構如圖4所示。

如果路由器中有兩個以上輸入端向同一個輸出端發送數據時,就會對路由器內部的讀寫操作產生爭奪。這時,路由器應提供仲裁機制進行發送優先級的確定。仲裁后,得到發送權的輸入端向輸出端口發送一個包。也就是說,在同一時間內,路由器中只能有一個輸入端進行數據的發送。當這個輸入端發送完畢后,其他輸入端再進行數據的發送。這樣極大地降低了路由器的工作效率。

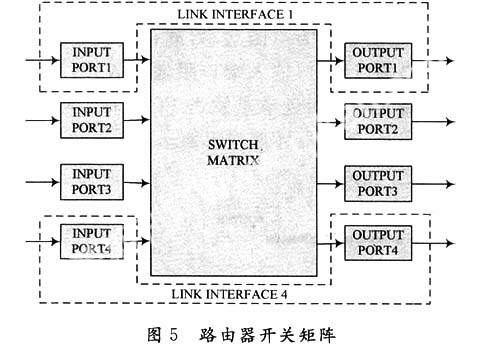

為了改善路由器的傳輸速度,研究設計了一種基于流水線技術的SpaceWire路由器。關鍵技術是設計一個基于流水線技術的無阻塞的并行交換開關(如圖5)。

對于SpaceWire路由器內部數據流包頭的檢測和數據重排電路的設計復雜、規模較大。為了簡化電路設計的復雜度、降低電路功耗、提高系統工作可靠性,針對輸入數據流的包頭檢測及數據重排電路,采用事務處理流水線技術實現電路方案設計。圖6為采用事務處理流水線技術實現包頭檢測及數據重排電路方案框圖。采用此設計方案進行電路設計的實驗結果表明,采用流水線設計技術實現的電路其規模比原來電路減少了50%。

圖6所示的為并行交換體系結構,設計用FPGA實現K個M×M的無緩存的交叉開關作為交換模塊。這個體系結構是由M個輸入共享存儲器模塊、K個交叉開關和M個輸出共享存儲模塊組成。每個輸入/輸出共享存儲器模塊有V個外部線路接口,同時與所有交叉開關相連接。

輸入共享存儲器模塊包含(M*V)個VOQ(虛擬輸出隊列),保存輸出到不同目的端口的信元。輸出共享存儲器模塊包含V個輸出隊列,保存等待輸出的信元。在每個仲裁周期,輸入端口從(M*V)個VOQ隊列中隨機選擇M個隊列,向交換開關提交調度請求。交換開關以輪詢方式為各隊列提供服務,根據調度結果將授權信息反饋給輸入端口。授權信息指定的VOQ隊列頭信元通過交換開關直接到達輸出隊列,完成報文重組等處理后,發送到外部鏈路。為了避免輸出端發生緩沖區溢出,可采用反壓機制及時阻止輸入端發送過量信元。

在多個輸入端向一個輸出端發送數據時,在交換開關中利用流水線技術讓多個輸入端分時向輸出端發送數據。也可以在每個輸入端都復制一個路由查找表,這樣在就不需要仲裁機制了。當數據流進入輸入端后,根據包頭地址查找路由表,確定要發送的輸出端,然后進行發送,當多個輸入端進行傳送時,就會給每個輸入端分配一個時間令牌,當自己的時間令牌有效時,就進行傳輸,當時間令牌失效時,停止傳輸,直到將所有數據傳輸完畢。而時間令牌的分配,由路由算法來控制。基本思想是利用流水線將時間令牌輪流分給每個輸入節點,還可根據具體的一些情況對路由算法進行優化。此項工作目前正在進行中。基于這種流水線技術設計的SpaceWire路由器,速度將會達到200 Mb/s。從而使SpaceWire網絡的數據傳輸更加快速,也會實現各輸入端到輸出端的同時訪問。

3 結 語

介紹了SpaceWire路由器的基本原理,重點闡述了一種基于流水線技術的SpaceWire路由器的研究,關鍵技術是用FPGA設計一種基于流水線技術的交換開關。SpaceWire路由器符合未來航天航空領域的發展需求,所以SpaceWire路由器速度是非常關鍵的指標。本文就是介紹了一種改善SpaceWire路由器的速度的方法,具有很高的研究價值。目前此項研究正在實現過程中。

參考文獻

[1]胡曉峰.并行路由器體系結構若干關鍵技術研究[D].長沙:國防科學技術大學,2004.

[2]孟李林.一種無阻塞的高階電路交換方案設計[J].西安郵電學院學報,2007,12(5):1-3.

[3]白海斌,邵淼青.基于FPGA的數據無阻塞交換設計[J].無線電通信技術,2007,33(6):63-65.

[4]Steve Parkes,Chris McClements.SpaceWire Router.http://Netherlands: International SpaceWire Seminar, 2003.

[5]UT200SpW4RTR 4-Port SpaceWire Router[EB/OL].http://www.aeroflex.com,2007.

[6]侯伯亨,顧新.VHDL硬件描述語言與數字邏輯電路設計[M].西安:西安電子科技大學出版社,2004.

[7]田華.SpaceWire總線在遙測衛星數傳系統中的設計應用[M].上海:上海交通大學出版社,2005.

[8]徐明偉,徐恪.路由查找算法研究綜述[J].軟件學報,2002,13(1):42-50.

[9]孫志剛,蘇金樹.高效的Crossbar仲裁算法——ISP[J].計算機學報,2000,23(10):1 078-1 082.

[10]胡曉鋒,孫志剛,盧錫城.并行交換系統PSIQC的容錯機制[J].計算機工程與科學,2004,26(10):1-4,10.

作者簡介 李 瀟 男,1984年出生,陜西人,在讀碩士研究生。研究方向為計算機應用技術。

龔龍慶 男,1963年出生,吉林長春人,總工程師,研究生導師。研究方向為計算機應用。

田 衛 男,1969年出生,陜西人,研究員。研究方向為嵌入式計算機。

南 希 女,1983年出生,在讀碩士研究生。研究方向為計算機應用技術。