LEON2應用于數字機頂盒CPU的FPGA仿真

朱 旭 徐良波

摘 要:采用免費軟核LEON2作為數字機頂盒的CPU可以降低產品成本。為了使LEON2軟核能更快更好地應用于數字機頂盒,選擇先在FPGA開發板上建立基于LEON2處理器的一個原型,通過這個原型對硬件性能進行仿真,并且還可以在線修改程序,這樣就很容易驗證系統的性能,加速軟件開發調試流程。經過在FPGA開發板上的仿真,對基于LEON2的系統測試取得了預期的效果。

關鍵詞:LEON2;片上系統;嵌入式系統;知識產權核;現場可編程門陣列

中圖分類號:TP368.1文獻標識碼:B

文章編號:1004 373X(2009)02 030 03

FPGA Simulation of LEON2 Applied to Digital Set-top Box CPU

ZHU Xu,XU Liangbo

(710 Research & Development Institute of CSIC,Yichang,443003,China)

Abstract:Selecting free IP core LEON2 for CPU of Digital Set-top Box (STB) can reduce the cost.For LEON2 applied to STB faster and better,firstly prefer to set up a prototype based on LEON2 processor on FPGA,through the prototype to emulate the hardware capability,and to modify program online,afterward validate the system capability easily,and the flow of program exploitation can be accelerated.A prospective effect of test to the system based on LEON2 through the FPGA simulation is gained.

Keywords:LEON2;system on chip;embedded system;IP core;FPGA

0 引 言

近年來,隨著數字多媒體業務和Internet網絡的迅速發展,新型數字機頂盒可以有效利用我國巨大的有線電視網絡資源,完成視頻點播、數字電視的接收及接入Internet等綜合業務功能。

1 數字機頂盒總體設計方案

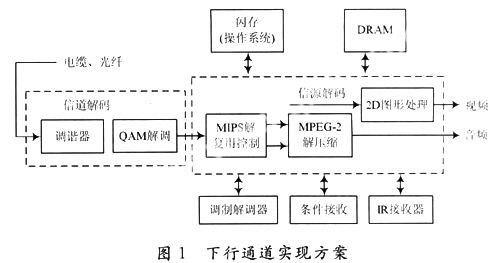

數字機頂盒分為兩個通道,下行通道接收來自電纜或光纖的有線電視信號,上行通道傳輸從客戶端到服務器端的指令。

下行通道方案如圖1所示,調諧器接收來自有線網的高頻信號,通過QAM解調器完成信道解碼,從載波中分離出包含音、視頻和其他數據信息的傳送流(TS)。傳送流中一般包含多個音、視頻流及一些數據信息。解復用器則用來區分不同的節目,提取相應的音、視頻流和數據流,送入MPEG-2解碼器和相應的解析軟件,完成數字信息的還原。對于付費電視,條件接收模塊對音、視頻流實施解擾,并采用含有識別用戶和進行記賬功能的智能卡,保證合法用戶正常收看。MPEG-2解碼器完成音、視頻信號的解壓縮,經視頻編碼器和音頻D/A變換,還原出模擬音、視頻信號,在常規彩色電視機上顯示高質量圖像,并提供多聲道立體聲節目。

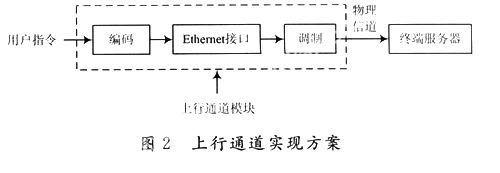

上行通道方案如圖2所示,用戶發送指令,然后經過編碼符合網絡通信協議,從以太網接口傳輸到調制器,再經物理信道傳給終端服務器。

2 LEON2處理器

嵌入式CPU是數字電視機頂盒的心臟,當數據完成信道解碼以后,首先要解復用,把傳輸流分成視頻、音頻,使視頻、音頻和數據分離開。CPU是嵌入式操作系統的運行平臺,它要與操作系統一起完成網絡管理,顯示管理、有條件接收管理、圖文電視解碼、數據解碼、視頻信號的上下變換等功能。

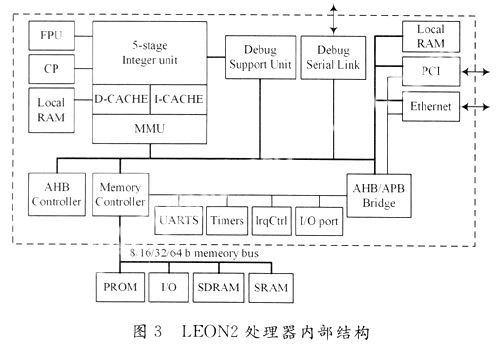

LEON系列32位RISC處理器核的第一個版本是LEON1,它是由歐洲航天局主持設計開發的。LEON1的設計初衷是為了使歐洲能夠擺脫在航空航天高性能嵌入式處理器上對美國的嚴重依賴。以Jiri Gaisler為首的設計團隊在完成LEON1后從歐洲航天局獨立出來,成立了Gaisler Research 公司,后來就推出了LEON2處理器。LEON2是一個可配置的微處理器核,使用SPARC V8指令集,它的源代碼由可綜合的VHDL代碼構成。LEON2內部結構如圖3所示。

LEON2的整數處理單元是5級流水線設計,采用SPARC V8(IEEE-1754)指令和體系結構,具有分離的數據Cache和指令Cache。LEON2的整數單元包括一個可選的16×16 的MAC單元,能夠完成基本的DSP運算,同時還提供了浮點運算單元(FPU)的接口和協處理器(CP)的接口,可以擴展浮點運算和DSP處理。LEON2選用了ARM公司的AMBA 2.0片上總線標準,用于連接內存控制器、定時器、中斷控制器、UART接口、PCI接口、10/100 Mb/s以太網接口等模塊。LEON2同時還提供1個調試支持單元和1個調試串口,用于支持片內調試。LEON2的一個非常重要的特點就是具有很好的可配置性。使用者根據自己的需要,通過一個用tcl/tk腳本編寫的圖形化界面,對LEON2內核的絕大多數模塊進行配置,比如可以配置Cache的大小和訪問方式,是否支持硬件乘/除法,是否需要內存。

Gaisler Research 公司還提供了比較完善的基于LEON2的GNU軟件開發環境。使用者可以使用TSIM或GRMON進行LEON內核的調試仿真。LECCS是專門針對LEON的交叉編譯系統,可以進行C/C++的編譯和調試。SnapGear Linux是基于LClinux的實時Linux內核,它的LEON版提供了對LEON處理器的全面支持,可以支持MMU和NOMMU等不同配置方案。

由以上描述可以看出,LEON2具有強大的硬件配置和完備的軟件開發環境支持,可以承擔數字機頂盒CPU要求的各種信號處理任務。

3 在FPGA開發板上建立LEON2的SoC平臺

3.1 硬件平臺的建立

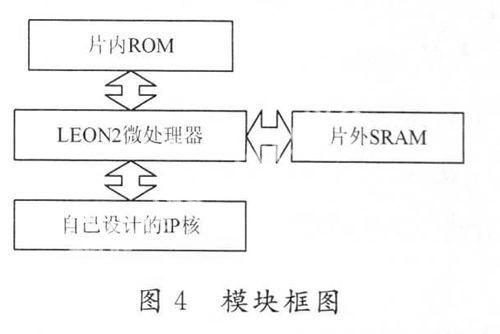

圖4就是基于LEON2的平臺的模塊框圖。LEON2處理器作為核心部分,片內ROM存放Monitor負責系統初始化和將程序拷貝到片外SRAM內的任務,片外RAM是FPGA開發板上Memory,用來存放程序和數據。設計的IP核通過AHB總線和LEON2相互交互。

FPGA開發板主要有以下資源:50 MHz有源時鐘;1塊Altera公司的核心FPGA芯片EP2C20F484C8,邏輯單元18 752個;2片512 KB的IS61LV25616AL SRAM芯片組成32 b寬共1 MB容量,其中每片設計為可兼容1 MB,總共最大可擴充到2 MB;JTAG接口(通過JTAG接口可以從PC機上對EP2C20F484C8進行編程);串口與計算機COM1相連,可以用于程序下載。

將配置好的LEON2的VHDL代碼,加入設計的HDL代碼,一起使用Synplify綜合工具生成FPGA的網表文件;然后使用Quartus進行布局布線,將LEON2核同片內ROM和片外SRAM連接,布局布線完成后生成相應的SOF文件;通過JTAG端口將SOF文件下載到片子上去,對FPGA硬件進行配置,最后占用 FPGA資源是5 800個邏輯單元,可以達到的時鐘頻率最大為46 MHz。

3.2 軟件設計

由于Quartus軟件可以預先配置EP2C20F484C8片上ROM,所以可以在LEON2的片上ROM預先配置好的1 KB大小的Monitor軟件。Monitor的主要作用是在LEON2系統reset初始化時首先對處理器初始化,對LEON2的存儲配置寄存器進行配置;然后向UART口發送啟動信息;等待UART信息。當軟件部分使用交叉編譯器LECCS在PC上編譯完畢后, PC機通過UART口和FPGA開發板相互通信,就可以將編譯好的srec文件下載到FPGA開發板上,放置在片內ROM里面的Monitor程序就讀入程序的內容以及程序的起始地址。開始Monitor將srec程序拷貝到SRAM程序區,等全部程序下載好以后,Monitor最后1條程序就會自動跳轉到程序的起始位置,執行SRAM里的程序。這樣就可以反復修改程序,反復下載程序,便于軟件的開發和調試。

4 結 語

通過將片上系統映射到FPGA,這樣可以在接近運行速度的前提下,驗證硬件和軟件。這樣不僅為軟件部分能盡早地進行開發與調試工作提供了原型,同時也可以在實際運行中發現一些在系統設計中沒有注意的地方。最終可以縮短設計周期,同時為ASIC設計一次成功提供了更大的把握。

在FPGA開發板上建立基于LEON2處理器的SoC平臺后,使用這個原型系統,就可以很容易驗證系統的性能,并且加速軟件開發調試流程。

參考文獻

[1]Gaisler Research.LEON2 Processor User′s Manual (XSTEdition),Version 110127,2005.

[2]邵洋,單睿,張鐵軍,等.基于可配置處理器的SoC系統級設計方法[J].計算機工程與應用,2006,42(26):96-98.

[3]張雁,曾田.VHDL及高層綜合[J].計算機與數字工程,2003,31(3):67-69,36.

[4]劉軍,郭立,鄭東飛,等.開放性32位RISC處理器IP核的比較與分析[J].電子器件,2005(4):158-162.

[5]Altera Corporation.Nios Embedded Processor Development Board.2002.

[6]LEON DSU Monitor User′s Manual(Version 1.0.11).2003.

[7]ALTERA Corp.Excalibur Embedded Processor Solutions:Nios.2002.

[8]RAJSUMANR.System on a Chip:Design and Test[M].Artech House,2000.

[9]MOURADS.Principle of Testing Electronic System[M].John Wiley & Sons,Inc,2000.

[10]林金永.面向SOC的設計方法研究[J].航天控制,2004,22(2):68-71.

[11]陳秀玲,周欣,陳黎平.新的片上可編程系統(SOPC)解決方案Nios[J].今日電子,2003(7):10-12.

[12]雷紹充,梁鋒,邵志標.對SoC芯片全面驗證的仿真結構的研究[J].半導體技術,2004(4):114-117.