基于CPCI總線和TS201的通用雷達信號處理板設計

許月圓 李冬梅 宮慧敏

摘 要:在介紹ADI公司TigerSharc系列處理器ADSP-TS201和PLX公司PCI9656這兩款芯片,詳細闡述處理板的整體結構和DSP與PCI9656的接口電路設計原理的基礎上,提出一種ADSP-TS201基于橋芯片PCI9656實現與CPCI總線通信的雷達信號處理板的設計方案,實現RocketIO到DSP數據的高速傳輸,它克服了傳統雷達信號處理板通用性差的缺點。

關鍵詞:CPCI總線;DSP;橋芯片;鏈路口

中圖分類號:TP368.1文獻標識碼:B

文章編號:1004 373X(2009)02 129 03

Design of Radar Signal Processing System Based on ADSP-TS201 and CPCI Bus

XU Yueyuan1,LI Dongmei2,GONG Huimin1

(1.Xidian Univesity,Xi′an,710071,China;2.27th Research Institute of CETC,Zhengzhou,450005,China)

Abstract:A design is proposed to implement the function of communication between CPCI bus and ADSP-TS201 based on the bridge chip PCI9656.TigerSharc processor ADSP-TS201 of ADI Company and the bridge PCI9656 of PLX Company are introduced in this paper,and the whole structure and design principle of interface circuit between PCI9656 and DSP are proposed.The design overcomes bad performance of the compatibility existing in the traditional radar signal processing system and implements the high speed transmission of data between RocketIO and DSP.

Keywords:CPCI bus;DSP;bridge;link port

0 引 言

隨著科學技術的發展,傳統的雷達信號處理系統由于專用性強,兼容性差,影響了系統的通用性和其擴展能力,不能滿足現代雷達實時高速的信號處理需求。設計通用并行信號處理系統己經成為高速實時信號處理發展的必然趨勢,而基于CPCI總線的多DSP信號處理模板設計是該領域的研究熱點之一。該設計針對傳統雷達信號處理系統通用性和擴展能力差提出一種ADSP-TS201基于PCI9656橋芯片實現與CPCI總線通信的高速、通用性強的信號處理系統,并介紹一種DSP與PCI9656的接口電路設計。

1 器件介紹

1.1 ADSP-TS201

ADSP-TS201是ADI 公司TigerSHARC 系列中集成了定點和浮點計算功能的高速DSP。ADSP-TS201內部4條相互獨立的128位寬度的內部數據總線,每條連接6個2 Mb內部存儲區塊中的一個,提供各自數據、指令集I/O訪問和28 GB/s的內部存儲器寬帶;處理器內核最高可工作在600 MHz,單周期能執行4條指令,每秒能進行3.4億次乘累加和2.8億次浮點操作,是面向通信和視頻領域的高端DSP。ADSP-TS201有14通道的DMA控制器;4個鏈路口可用于與其他DSP進行無縫聯接,實現高速度高數據吞吐率。鏈路口可以4位并行方式傳輸,也可以編碼為1位傳輸方式。通常以4位并行方式傳輸,當處理器核工作在500 MHz時,鏈路口也可工作在500 MHz,每個鏈路口的雙向數據吞吐率可達1 000 MB/s,4個鏈路口合起來數據吞吐率可達4 GB/s;集成SDRAM控制器最大支持256 M×32 b的內存容量,方便與外部SDRAM連接。ADSP-TS201適合對大數據量數據處理實時性要求高的應用領域。TigerSHARC 系列的DSP 接口豐富,外部設備接口包括SDRAM 控制器、EPROM 接口、主機接口、多處理器接口;其引導程序的加載方法也非常靈活,可根據實際系統設計的需要靈活選用。

1.2 PCI9656

PCI9656是PLX公司推出的與PCI9054相兼容的、能提供混合高性能PCI總線的接口控制芯片,采用了業界領先的數據流水線架構技術,符合PCI V2.2規范。PCI9656的工作狀態包括以下兩個方面:工作方式和局部總線操作模式。PCI9656的工作方式包括直接主模式、直接從模式和DMA模式,它的局部總線操作模式有M模式、C模式和J模式。它具有64位數據線66 MHz時鐘的PCI總線接口和32位數據總線66 MHz時鐘的Local端接口;配有的DMA引擎可實現數據的高速傳輸;具有PCI優先判決器,支持7個外部主控制器;可以通過消息管理I/O,提供兩種方式選擇,一是通過郵箱寄存器和門鈴寄存器;二是通過所提供的I2O接口。它有64 b/66 MHz PCI性能,符合PCI V2.2規范,采用數據。設計者可以將芯片32 b,66 MHz局部總線與各類高速設備,如DSP、存儲器、自定義ASIC和FPGA連接,通過PCI9656數據流水架構使其局部端連接設備具有64 b/66 MHz的PCI I/O性能。

2 系統工作原理

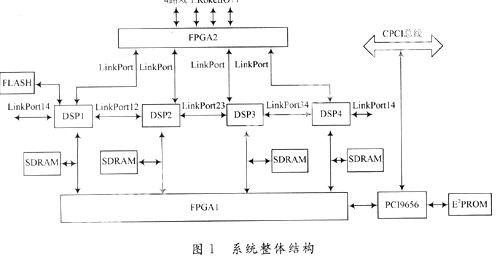

信號處理板上DSP的工作與主機相對獨立,主機通過CPCI總線給信號處理板傳送加載程序和一些控制信息,并監控信號處理板。采集數據通過4路全雙工Rocket_IO口發送給信號處理板。系統的整體結構如圖1所示。

2.1 DSP的電路設計

信號處理板中DSP對來自板外的采樣數據進行數據整理、相參積累和脈沖壓縮。4片DSP之間采用鏈路口方式實現點對點的通信。DSP采用主機與EPROM方式引導和加載程序,先通過FLASH將加載程序導入DSP1,然后用主機引導方式將傳入DSP1內的加載程序依次傳輸給其他3片DSP。由于DSP有專用的SDRAM尋址空間和外圍接口,DSP與SDRAM之間能實現無縫連接。該設計中每片DSP外掛1片256 Mb的SDRAM,保證了DSP足夠的存儲空間。

2.2 PCI9656與DSP連接設計

由于PCI9656與DSP接口不兼容,所以用邏輯轉換器件FPGA1實現它們之間的連接。FPGA1中設計有一個能與ADSP-TS201S直接通信的主機接口模塊,將ADSP-TS201S主機接口與FPGA1內的主機接口直接相連。PCI9656通過FPGA1內主機接口間接訪問ADSP-TS201S。FPGA1中設計16 K×32 b的雙口RAM,用于緩存PCI9656與DSP之間讀寫數據。FPGA1一端與4片DSP相連,另一端與PCI9656局部端相連。當出現多個DSP同時請求與PCI9656通信時,FPGA1內DSP開關選擇模塊對其進行仲裁。PCI9656根據主機的要求可以訪問任意一片DSP。PCI9656對信號處理板上4片SDRAM的訪問有2種方式。第一,通過DSP來間接的訪問SDRAM,DSP先將SDRAM中數據讀到其內部存儲區,然后PCI9656通過訪問DSP訪問SDRAM;第二,在FPGA1內設計SDRAM控制器,通過FPGA1內控制器直接訪問SDRAM。

2.3 PCI9656與CPCI總線連接設計

設計中信號處理板是6U規格,可與J1至J5五個連接頭相連。J1是32位PCI總線,J2用于64位PCI總線或用戶自定義I/O口;J3,J4和J5是用戶自定義I/O口。為了保證信號處理板的通用性和可擴展性,J1與J2連接頭作為64位數據寬度的CPCI總線。PCI9656一端與FPGA1相連另一端分別與J1和J2連接頭相連。需要注意的是PCI9656與CPCI連接的引腳必須插入10 Ω的匹配電阻,以降低對背板的干擾。

2.4 Rocket_IO與DSP的連接設計

信號處理板通過全雙工Rocket_IO口接收板外的采集數據,數據吞吐率可達1.25 Gb/s。 FPGA2實現Rocket_IO與DSP的LinkPort之間的接口轉換,其一端連接4路Rocket_IO口相連另一端連接每片DSP的1路LinkPort,即4路鏈路口。DSP的每路鏈路口數據吞吐率可達1 GB/s。FPGA2對Rocket_IO口送入的數據整理后,利用鏈路口傳輸給相應的DSP。任意一路LinkPort能與任意一路的Rocket_IO口通信,當多路LinkPort爭用一路Rocket_IO口或多路Rocket_IO口爭用一路LinkPort時,FPGA2內的總線開關模塊實現它們之間的仲裁。設計中信號處理板可以選用任意用戶自定義IO口作為Rocket_IO通道。

3 PCI9656與DSP的接口設計

PCI9656的局部端采用C模式,32位數據和32位地址線。PCI9656配置為直接從模式,即只有主機可以通過PCI9656申請局部端總線控制權訪問DSP。4片DSP與FPGA1連接方式相同,這里只給出1片DSP與PCI9656之間的接口邏輯轉換。DSP和PCI9656的連接如圖2所示。

PCI9656對DSP的訪問通過FPGA1間接實現,FPGA1內設計有實現邏輯轉換的主機接口模塊、用于數據緩存的雙口RAM模塊和DSP開關選擇模塊。

3.1 PCI9656讀DSP

(1) PCI9656使LHOLD變高申請局部總線控制權;FPGA檢測到后,立即使LHOLDA變高,告知PCI9656局部總線申請成功。PCI9656使ADS和LW/R變低,然后發送主機地址;FPGA1依據高位地址譯碼生成DSP片選信號,根據LW/R將主機接口配置為讀方式,同時使PCI9656的READY信號無效。

(2) FPGA1向相應的DSP發HBR和RD申請總線控制權并請求讀數據;DSP檢測到HBR后返回HBG和ACK。FPGA1檢測ACK到信號后,接收數據并緩存至雙口RAM。當數據傳輸完畢時DSP使RD和ACK無效,撤銷HBG,FPGA1接著撤銷HBR。

(3) FPGA1使READY有效,PCI9656檢測到該信號后,開始讀取雙口RAM中的數據。數據傳輸完畢后FPGA1使READY無效并收回LHOLDA,PCI9656接著撤消LHOLD,此次讀操作結束。

3.2 PCI9656寫DSP

(1) PCI9656使LHOLD變高申請局部總線控制權;FPGA檢測到后,立即回應使LHOLDA變高告知PCI9656局部總線申請成功。PCI9656使ADS變低、LW/R變高,然后發送主機地址;FPGA1根據高位地址譯碼生成DSP片選信號,根據LW/R將主機接口配置為寫方式,同時使能PCI9656的READY。

(2) PCI9656檢測到READY后,將數據寫入雙口RAM。數據傳輸完畢后PCI9656使READY無效,收回LHOLD;FPGA1接著撤消LHOLDA。

(3) FPGA1向相應的DSP發出HBR和WRL申請總線控制權并請求對DSP寫數據操作,DSP檢測到信號返回HBG和ACK。FPGA1檢測到ACK信號后,開始將雙口RAM中的數據發送給DSP。數據傳輸完畢后FPGA使WRL無效,撤銷HBR;DSP接著撤銷HBG和ACK。此次寫操作完成。

4 結 語

提出的基于CPCI總線的高速通用雷達信號處理板設計,繼承了CPCI總線可靠、可擴展、通用性強的特點。PCI9656橋芯片和FPGA1邏輯轉換芯片實現板外主機對DSP的訪問。通過FPGA2將 Rocket_IO口與DSP的LinkPort口互聯實現數據的高速傳輸。

參考文獻

[1]劉書明,羅勇江.ADSP TS20XS系列DSP原理與應用設計[M].北京:電子工業出版社,2007.

[2]蘇濤,蔡建隆,何學輝.DSP接口電路設計與編程[M].西安:西安電子科技大學出版社,2003.

[3]李貴山,陳金鵬.PCI局部總線及其應用[M].西安:西安電子科技大學出版社,2003.

[4]蘇濤,吳順君,李真芳,等.高性能DSP與高速實時信號處理[M].西安:西安電子科技大學出版社,2002.

[5]PLX.PCI 9656BA Data Book.2003.

[6]PICMG.CompactPCI Specification.1999.

[7]Analog Devices.ADSP-TS201 TigerSHARC Processor Hardware Reference.2004.

[8]Xilinx.Virtex-5 RocketIO GTP Transceiver User Guide.2007.

[9]徐鍵,戴紫彬.PCI9656型64位PCI總線接口電路及其應用[J].國外電子元器件,2005(8):54-56.

[10]包志強,吳順君,李明.基于CPCI總線的多DSP系統的接口設計[J].電子技術,2004(2):55-58.

作者簡介 許月圓 女,1983年出生,碩士研究生。研究方向為系統仿真與信息處理。

李冬梅 女,1967年出生,高級工程師。

宮慧敏 女,1982年出生,碩士研究生。研究方向為系統仿真與信息處理。