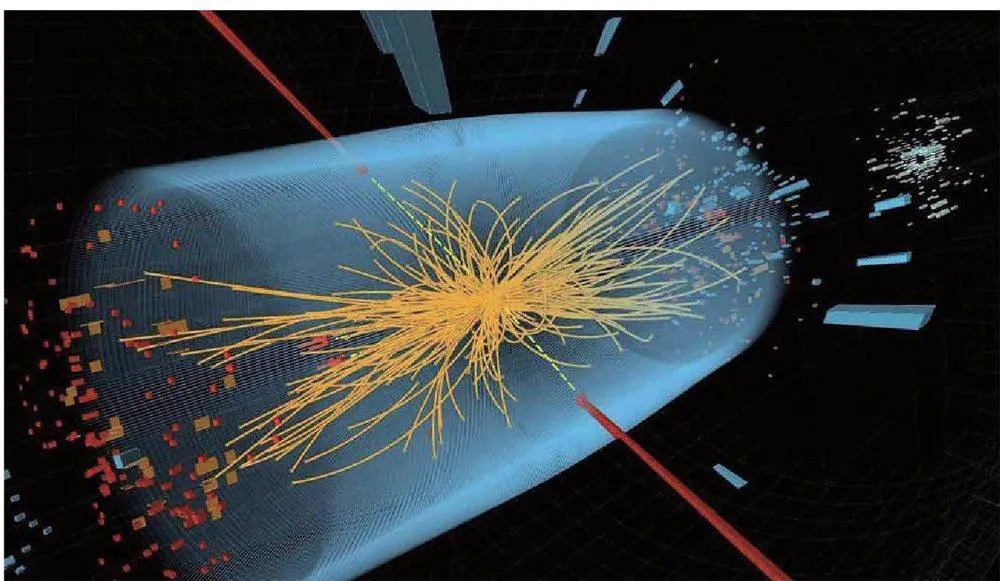

沒有上帝粒子就沒有人類

2013 年諾貝爾物理學獎頒發給比利時的弗朗索瓦·恩格勒和英國的彼得·希格斯,表彰他們在預測希格斯粒子( 即“上帝粒子”) 所做出的貢獻

關于上帝粒子你可能不知道的十件事

1、上帝粒子從哪里來?

物理學家普遍認為,上帝粒子來源于宇宙大爆炸。事實上,宇宙大爆炸被認為是包括上帝粒子在內的一系列基本粒子的最初起源。

2、上帝粒子如何使其他粒子產生質量?

上帝粒子會形成遍布宇宙空間的希格斯場,一些粒子在希格斯場中運動,就像在糖漿中穿行,因受到阻力而變得凝滯,粒子由此獲得質量。不同粒子受到的“阻力”不同,其所獲得的質量也有差異。

3、為什么說沒有上帝粒子,就沒有生命,沒有人類?

如果沒有上帝粒子,宇宙中的所有粒子都將以光速運動。這么快的速度運行,粒子將無法結合到一起,就不會產生原子、分子、DNA、蛋白質,也就不會有生命,不會有人類,不會有其他任何物質,宇宙將會是一片虛無。

4、科學家可能在十幾年前就捕捉到上帝粒子了?

2000 年,歐洲核子研究組織當時的旗艦加速器——大型正負電子對撞機打算結束運行,結果發現了一個跡象,看起來就像上帝粒子,擁有大約115 GeV的質量。科學家說服管理層,讓大型正負電子對撞機超期運行了6 個星期,在超期服役期間,更多看起來像是上帝粒子的事件出現了。科學家又要求再次延長運行時間,但是大型正負電子對撞機必須拆除,給更強大的對撞機(LHC)騰位置。2011 年,LHC 宣布了最新的結果,暗示上帝粒子如果存在的話,它的質量介于115-130 GeV 之間,這說明科學家可能在十幾年前就捕捉到上帝粒子了。

5、尋找上帝粒子過程中科學家有沒有動搖過?

2008 年8 月,歐洲核子研究中心開始運行新的大型質子對撞機。這架大型質子對撞機造價約為80 億美元。計劃實施時,將有來自34 個國家近2000 名科學家參加。樂觀估計,將在2010 年前后提供一個確切的答案。然而2011年8 月,歐洲核子研究中心表示:一些跡象表明,上帝粒子也許真不存在,只是人們的“幻想”。與此同時,該中心許多科學家也認為“上帝粒子不存在”

的可能性越來越大。

6、希格斯關于上帝粒子的論文曾經被拒?

1964 年, 希格斯寫了兩篇論文,每篇都只有兩頁長,內容就是現在被稱為希格斯場的東西。《物理快報》接收了第一篇論文,但拒掉了第二篇論文。著名物理學家南部陽一郎在評審第二篇論文的時候,建議希格斯加上一部分內容來解釋這一理論的物理學意義。希格斯加了一段話,預言這個場中會產生一種新的粒子,即上帝粒子。然后,他把改過的論文投給了那家雜志的對手——《物理評論快報》,結果發表了。

7、英國是不是舉辦過一場比賽,來尋找解釋希格斯場的最佳方法?

科學家很難向英國政府解釋清楚希格斯場。1993 年,英國科學部長威廉·瓦多格列佛發起一場比賽,讓科學家用一頁紙的篇幅向他解釋希格斯場,獲勝者是英國倫敦大學學院的物理學家戴維·米勒。米勒把希格斯場比作一個房間,房間里均勻分散著一大群為政客聚會服務的工作人員。一個無關緊要的人可以不受阻礙地在人群中穿來穿去,然而,如果是時任英國首相撒切爾夫人到場,一定會吸引大量的關注:聚會工作人員會圍攏在她周圍,減慢她穿行的速度,使她帶上某種“質量”。

8、霍金是不是用100 美元打賭不存在上帝粒子?

著名物理學家霍金曾和密歇根大學的教授凱恩用100 美元打賭,自信地認為被稱為“上帝粒子”的希格斯粒子不可能被找到。不過,當歐洲核研究組織宣布找到上帝粒子時,霍金稱贊了該發現的重要意義,并打趣地說:“這個發現應該能為希格斯贏得諾貝爾獎,不過害我輸了100 美元”。

9、上帝粒子名字里為何有“上帝”兩字?

最初上帝粒子一說出自一本科普讀物,事實上,很多科學家認為認為“上帝粒子”這個稱呼過分抬高了這種粒子的重要性。利用類似的神學詞匯來標注一個令人費解的亞原子粒子,似乎是為了觸怒那些反科學的宗教人士,或至少使他們游離于科學之外。“上帝粒子”

已經成為希格斯粒子的一種別稱,然而它卻既非物理也非神的意志,卻對兩方面產生了影響。“上帝粒子”是一種廉價的稱呼,它在稱呼上無疑抓住了人們的關注點,然而它的意思卻是那樣含糊,真正內容很難被人們洞悉。

10、希格斯不喜歡“上帝粒子”這個名字?

美國物理學家、1988 年諾貝爾物理學獎獲得者利昂·萊德曼曾著有科普書籍《上帝粒子:如果宇宙是答案,那么問題是什么?》。后來媒體也沿用了這一稱呼,常常將希格斯粒子稱作是“上帝粒子”。上帝粒子這個名字廣泛傳播,然而,作為一個無神論者,希格斯非常不喜歡這個名字。在此之前,謙虛的希格斯并不希望自己的名字冠在粒子前,但權衡之下,他終于接受了希格斯粒子這個名稱。