H.264/AVC編碼器在TMS320DM6437上的EDMA優(yōu)化*

崔 遙,趙 鍇,崔慧娟,唐 昆

(清華信息科學(xué)與技術(shù)國家實驗室,北京 100084)

1 引言

TMS320DM6437(簡稱DM6437)數(shù)字媒體處理器是一款高性能定點數(shù)字信號處理芯片,采用第三代高性能的超長字指令(VLIM)結(jié)構(gòu),主頻可達 400~700 MHz,峰值運算速率高達 3200~5600 MI/s(兆指令/秒)。DM6437芯片所特有的增強型直接內(nèi)存存取(Enhanced Direct Memory Access,EDMA)數(shù)據(jù)搬移工具,可以采用乒乓緩存機制,通過配置芯片上的EDMA寄存器,實現(xiàn)CPU與數(shù)據(jù)搬移的并行操作,提高CPU的運行效率,而H.264/AVC[1]編碼器中大量的數(shù)據(jù)搬移,正好可以利用EDMA進行優(yōu)化,提高編碼器的高速緩沖存儲器(cache)命中率和編碼速率。

2 DM6437 EDMA簡介

2.1 EDMA結(jié)構(gòu)和工作流程

EDMA在傳輸過程中完全不占用CPU資源,節(jié)省大量的時鐘周期,支持片內(nèi)存儲區(qū)到片外,片內(nèi)存儲區(qū)之間和片外存儲區(qū)之間的數(shù)據(jù)讀寫并且傳輸模式靈活,支持三維傳輸模式,可以對傳輸數(shù)據(jù)進行重排,大大增強代碼的靈活性。

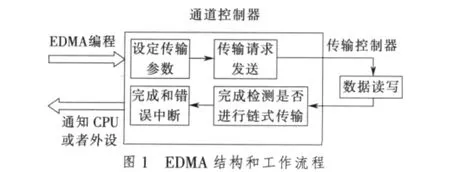

EDMA主要由EDMA通道控制器 (EDMA Channel Controller)和EDMA傳輸控制器 (EDMA Transfer Controller)組成,如圖1所示。EDMA通道控制器主要完成數(shù)據(jù)傳輸前的準備工作,如申請傳輸通道,配置傳輸參數(shù)到參數(shù)寄存器(PaRAM)中,發(fā)送傳輸請求以及傳輸完成檢測等工作。EDMA傳輸控制器主要是對EDMA通道控制器發(fā)送過來的傳輸請求進行處理,然后按照預(yù)先的設(shè)置,進行數(shù)據(jù)傳輸,具體參數(shù)配置主要是在EDMA通道控制器中完成。

2.2 EDMA傳輸控制器結(jié)構(gòu)

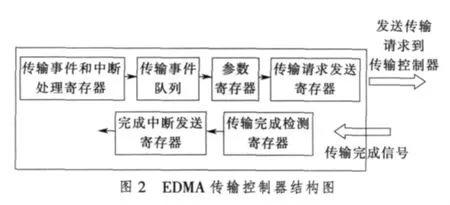

EDMA傳輸控制器主要包括傳輸事件和中斷處理寄存器、傳輸事件隊列、參數(shù)寄存器、傳輸請求發(fā)送寄存器和傳輸完成檢測寄存器以及完成中斷發(fā)送寄存器,結(jié)構(gòu)如圖2所示。傳輸事件和中斷處理寄存器用于觸發(fā)傳輸,傳輸事件隊列會按照優(yōu)先級對傳輸事件進行排序,參數(shù)寄存器用于存儲傳輸中需要設(shè)置的參數(shù),如源地址、目的地址、數(shù)據(jù)格式等參數(shù),傳輸完成檢測寄存器用于檢測傳輸是否完成,完成后是否進行鏈式傳輸,完成中斷發(fā)送寄存器用于在傳輸完成后向外設(shè)和CPU發(fā)送中斷信號。

2.3 EDMA的傳輸模式

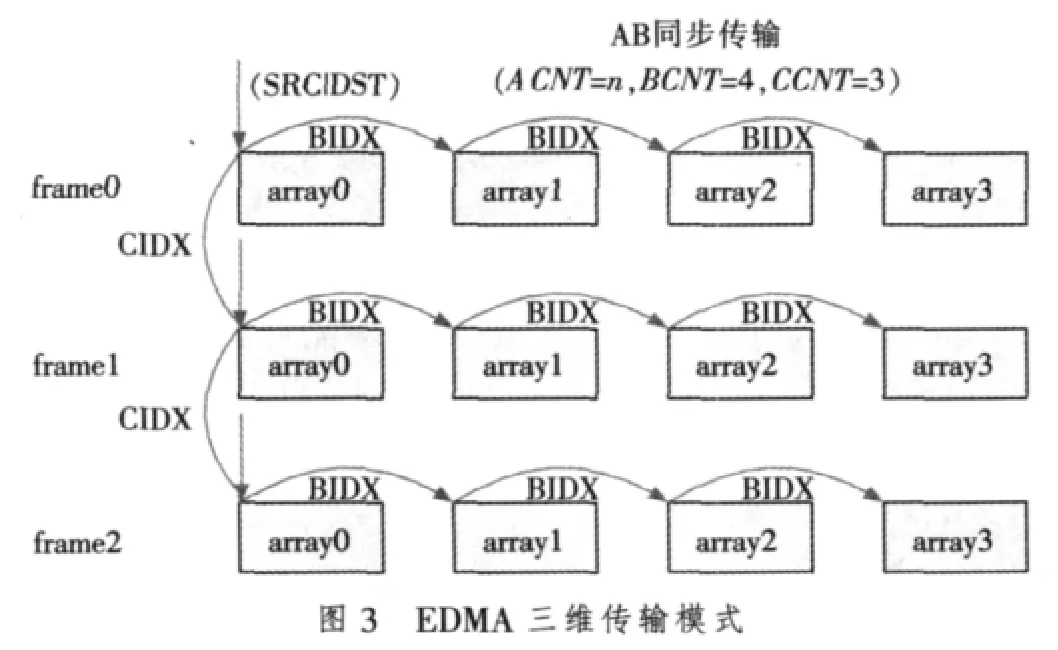

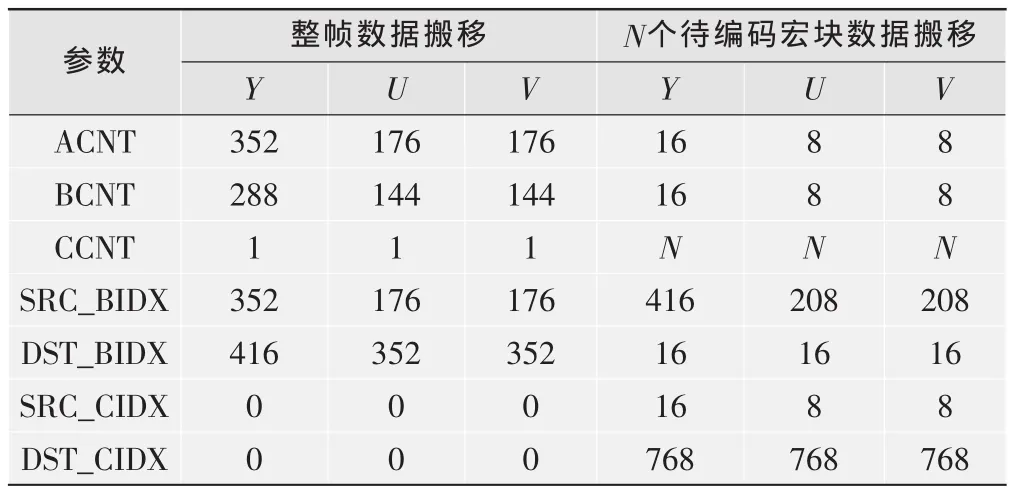

EDMA傳輸模式主要有2種:A同步模式和AB同步模式。A同步模式在每次傳輸被觸發(fā)后,會傳輸一個array,然后會產(chǎn)生一個中斷信號,AB同步模式每次傳輸一個frame,傳輸效率高,本文采用AB同步模式。ACNT,BCNT和CCNT分別代表三維傳輸數(shù)據(jù)塊的尺寸大小,如圖3所示,每個array由ACNT個字節(jié)組成,每個frame由BCNT個array組成,每個block由CCNT個frame組成。BIDX和CIDX分別表示第二維和第三維傳輸?shù)牡刂纷栽銎屏俊8鶕?jù)程序需要,對這幾個參數(shù)進行合理的設(shè)置,可以在數(shù)據(jù)傳輸過程中實現(xiàn)數(shù)據(jù)的重排,優(yōu)化數(shù)據(jù)存儲結(jié)構(gòu),提高cache命中率,從而最終提高代碼執(zhí)行效率。

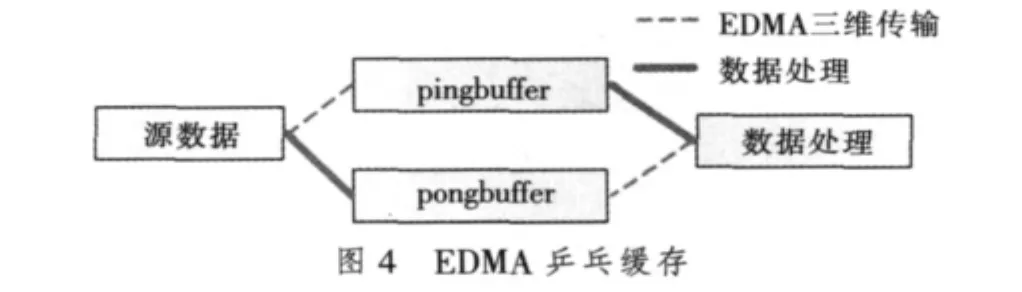

2.4 EDMA乒乓緩存機制

乒乓緩存機制是EDMA最重要的一種傳輸方式,如圖4所示。該方式可以實現(xiàn)EDMA與CPU的并行,本文兩處EDMA優(yōu)化均使用該傳輸方式。其實現(xiàn)主要是將傳輸目的緩沖區(qū)設(shè)置為原來目的緩沖區(qū)的2倍,然后分別用pingbuffer和pongbuffer作為這2塊緩沖區(qū)的指針,當(dāng)EDMA向pingbuffer存儲區(qū)傳輸數(shù)據(jù)時,編碼數(shù)據(jù)指針指向pongbuffer,當(dāng)pongbuffer中的數(shù)據(jù)編碼完成后,pingbuffer存儲區(qū)數(shù)據(jù)傳輸完畢,然后分別交換EDMA傳輸目的地址和待編碼宏塊的指針,即將pongbuffer緩沖區(qū)賦值給待編碼宏塊指針,將pingbuffer緩沖區(qū)賦值給EDMA傳輸?shù)牡刂分羔槨_@樣2個數(shù)據(jù)通路,在一路利用EDMA傳輸數(shù)據(jù)的同時,另一路由CPU進行編碼的數(shù)據(jù)運算。如果傳輸時間小于編碼運算的時間,則EDMA完全獨立于CPU在后臺運行,不耗費一個時鐘周期,因此實現(xiàn)了數(shù)據(jù)傳輸和CPU并行,提高了代碼的運行效率。

3 H.264/AVC編碼器EDMA優(yōu)化

3.1 編碼器數(shù)據(jù)存儲情況

H.264/AVC編碼器編碼步驟如下:1)編碼數(shù)據(jù)及輔助信息拷貝,主要包括兩部分數(shù)據(jù),一是待編碼宏塊數(shù)據(jù)從片外傳輸?shù)狡瑑?nèi),另一部分是周圍重建宏塊的數(shù)據(jù)信息(用于幀內(nèi)預(yù)測)和編碼信息(用于MV預(yù)測和熵編碼等)。2)宏塊分析,即根據(jù)率失真優(yōu)化得到該宏塊的最佳編碼模式。3)宏塊編碼,根據(jù)分析出來的最佳編碼模式,進行幀內(nèi)和幀間預(yù)測,得到殘差信息。4)重建編碼宏塊,并將當(dāng)前編碼宏塊的輔助信息(預(yù)測模式、MV信息等)寫入緩沖區(qū)(為編碼臨近宏塊使用)。5)宏塊熵編碼,根據(jù)宏塊編碼模式和殘差數(shù)據(jù)進行進一步的數(shù)據(jù)壓縮。通過以上分析,在幀數(shù)據(jù)讀入后進行邊界擴展和編碼前宏塊拆分階段,都涉及到了大數(shù)據(jù)量的搬移,因此對這兩部分進行EDMA優(yōu)化。

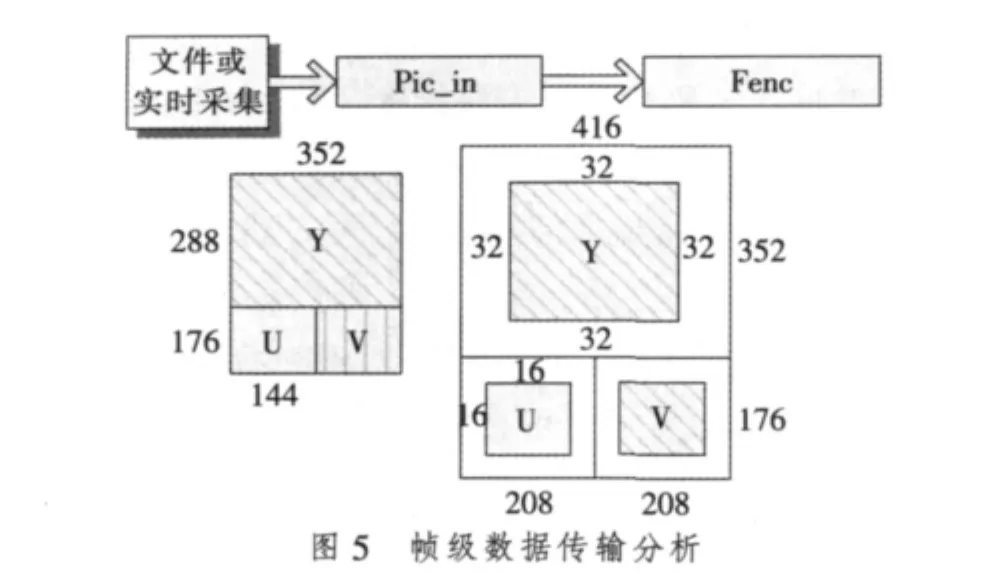

3.2 幀級EDMA優(yōu)化

編碼器在編碼前,首先會讀入一幀數(shù)據(jù)到片外存儲區(qū)Pic_in,為提高壓縮效率,支持越界搜索,對這一幀數(shù)據(jù)進行邊界擴展后存儲到片外存儲區(qū)Fenc,如圖5所示。而對幀數(shù)據(jù)進行邊界擴展,需要對整幀數(shù)據(jù)進行搬移,如果采用數(shù)據(jù)拷貝指令,占用了CPU的資源,費時費力,并且由于只有一塊存儲區(qū),編碼器每次必須等數(shù)據(jù)傳輸完成后,才能進行下面的操作,由于數(shù)據(jù)量大,等待時間較長,因此這里可以使用EDMA乒乓緩存機制進行優(yōu)化。

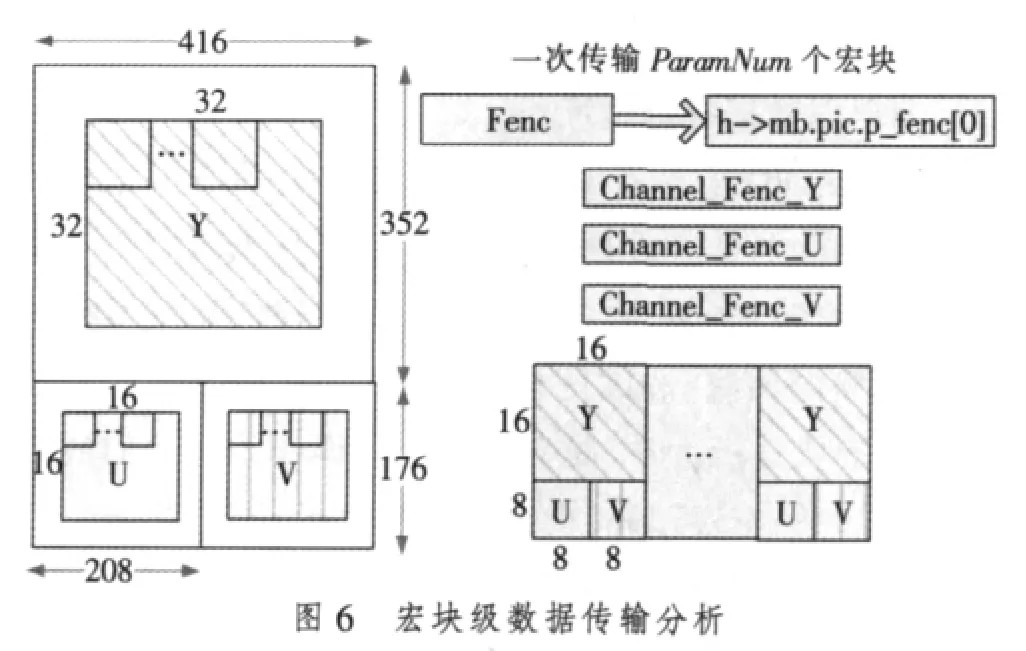

3.3 宏塊級EDMA優(yōu)化

為了更好地發(fā)揮EDMA在大數(shù)據(jù)量搬移上的優(yōu)勢,首先對程序進行修改。修改前,編碼器從片外整幀數(shù)據(jù)中讀入一個宏塊的數(shù)據(jù)到片內(nèi),然后進行編碼,但是一個宏塊的數(shù)據(jù)量較小,EDMA的優(yōu)勢難以得到發(fā)揮,因此對程序進行調(diào)整,編碼器每次讀入若干宏塊,如圖6所示,宏塊的個數(shù)通過ParamNum來控制,增加了每次傳輸?shù)臄?shù)據(jù)量。因此,進行調(diào)整后的編碼器,在這里也可以使用EDMA進行優(yōu)化。

幀級和宏塊級EDMA優(yōu)化的具體參數(shù)配置如表1所示。

表1 EDMA優(yōu)化配置參數(shù)

4 試驗結(jié)果與分析

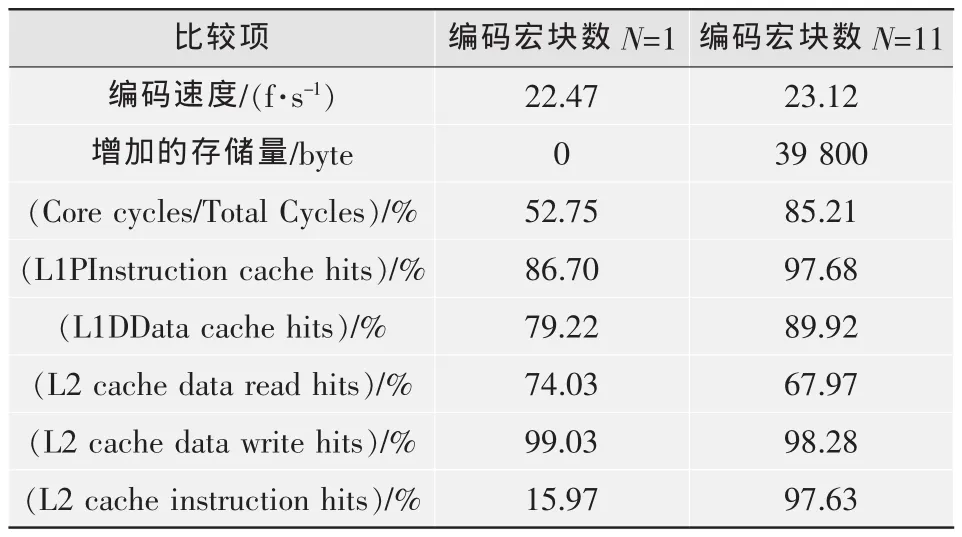

測試平臺使用DM6437開發(fā)板,采用典型測試序列Foreman(),對匯編優(yōu)化[2]過的x264[3]編碼器 cache命中率和編碼速度進行測試。根據(jù)DM6437上片內(nèi)存儲資源,對cache和內(nèi)部RAM配置如下:L1P存儲空間全部配置為cache,大小為32 kbyte;L1D存儲空間64 kbyte配置為內(nèi)部數(shù)據(jù)存儲存儲空間,16 kbyte配置為數(shù)據(jù)cache;L2存儲空間128 kbyte全部配置為cache(程序cache或者數(shù)據(jù)cache)。經(jīng)過多次測試,編碼器編碼前讀入的宏塊數(shù)目為11時,cache命中率得到顯著提高。具體的測試結(jié)果如表2所示。

表2 cache命中率影響對比

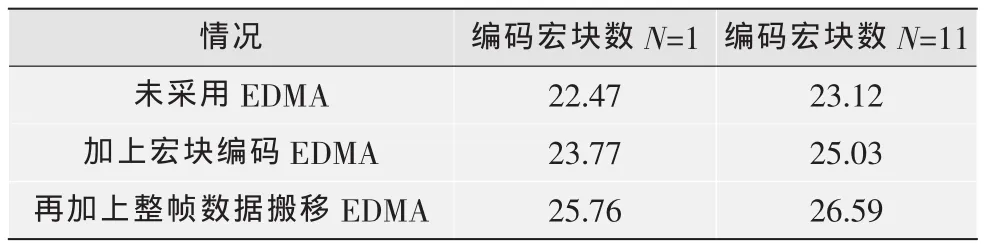

而采用EDMA優(yōu)化后,編碼速度也得到了改善,提高了大約3~4幀,并且一次讀入11個宏塊與一次讀入1個宏塊相比,前者采用EDMA優(yōu)化的效果更為明顯,如表3所示。

表3 編碼速率影響對比 f/s

5 小結(jié)

通過對H.264/AVC編碼器進行分析和結(jié)構(gòu)調(diào)整,采用EDMA乒乓緩存機制,對編碼器進行了優(yōu)化,提高了cache命中率和編碼速度,證明在處理大數(shù)據(jù)量的數(shù)據(jù)傳輸時,EDMA有其特有的優(yōu)勢。下一步將分析H.264解碼器的存儲結(jié)構(gòu)和程序流程,思考如何利用EDMA進行解碼器的優(yōu)化,以完成實時視頻通信的目標。

[1]WIEGAND T,SULLIVAN G J,BJONTEGAARD G,et al.Overview of the H.264/AVC video coding standard[J].IEEE Trans.Circuits and Systems for Video Technology,2003,13(7):560-576.

[2]彭燁.H.264/AVC編解碼器在TMS320C6400上的優(yōu)化實現(xiàn)[J].電視技術(shù),2008,32(9):21-23.

[3]X264 Codec[EB/OL].[2010-06-01].http://www.videolan.org/developers/x264.html.