高速差分信號的互連設計

趙增輝,劉中友,彭圻平

(中國電子科技集團公司第五十四研究所,河北石家莊050081)

0 引言

隨著高速數據業務需求的增加,如何高質量地解決高速IC芯片間的互連變得越來越重要。芯片間互連通常有 3種高速差分信號:LVPECL(Low Voltage Positive Emitter-Coupled Logic)、LVDS(Low-Voltage Differential Signals)、CML(Current Mode Logic)。在設計高速數字系統時,經常遇到不同接口標準IC芯片間的連接,為解決這一問題,本文首先簡要介紹每一種差分信號的主要特征,進而知道如何進行直流偏置,如何進行信號的互連設計。

1 主要的高速差分信號

1.1 LVPECL

LVPECL通常用于高速數據的串行或并行連接,標準的輸出負載是通過50 Ω阻抗跨接至V cc-2 V的電平上,在這種負載條件下,OUT+與OUT-的靜態電平典型值為V cc-1.3V,OUT+與OUT-輸出電流為14mA。LVPECL的信號擺幅為800mV,輸出阻抗很低(典型值為4~5 Ω),因此它有很強的驅動能力。但是,當LVPECL的輸出端通過傳輸線驅動負載時,應特別注意傳輸線路的阻抗匹配,防止低阻抗造成的失配導致信號時域波形產生“振鈴”現象。LVPECL的輸入是一個具有高輸入阻抗的差分對。該差分對共模輸入電壓需偏置到V cc-1.3 V,這樣允許的輸入信號電平動態最大。

1.2 CML

CML是一種簡單的高速接口,它的輸入與輸出是內在匹配好的,從而減少了外圍器件,更適合于在較高的頻率工作。CML接口典型輸出差分對集電極電阻為50 Ω,輸出信號高低電平切換是靠共發射極差分對開關控制。差分對發射極到地恒流源典型值為16 mA。假定CML輸出負載為一個50 Ω上拉電阻,此時單端CML輸出信號擺幅為 V cc~V cc-0.4 V。在這種情況下,差分輸出信號擺幅為800 mV,共模電壓為 Vcc-0.2 V,信號擺幅較小,功耗很低。但是CML接口自身驅動能力有限,多用于芯片間較短距離高速信號的互連。

1.3 LVDS

LVDS又稱 RS644總線接口,最基本器件就是LVDS驅動器和接收器。LVDS驅動器由驅動差分線對電流源組成,電流通常為 3.5 mA,負載阻抗為100 Ω。LVDS接收器具有很高輸入阻抗,因此驅動器輸出大部分電流都流過100 Ω匹配電阻,并在接收器輸入端產生大約350 mV電壓。當驅動器翻轉時,它改變流經電阻電流方向,因此產生有效邏輯“1”和邏輯“0”狀態。LVDS在 2.4 V的低電壓下工作,單端信號擺幅最低為200 mV,功耗低,適合做并行數據傳輸。

2 高速信號間的互連

高速信號間的互相連接主要通過直流耦合和交流耦合2種形式進行。下面主要以LVPECL到LVPECL、LVPECL到CML以及LVPECL到LVDS為例,詳細介紹信號互連的基本原理和實現方案。至于其他互連情況,讀者可以參考下面的例子自行推導即可。

2.1 LVPECL到LVPECL的連接

2.1.1 直流耦合

LVPECL標準的輸出負載是通過50 Ω阻抗跨接至V cc-2 V的電平上,這就構成了直流耦合的主要依據,直流耦合如圖1所示。

圖1 LVPECL直流耦合

該電路需要滿足以下方程:

在3.3V供電時,電阻按5%的精度選取,R1為130 Ω,R2為82 Ω。而在5 V 供電時 ,R1為 82 Ω,R2為130 Ω。

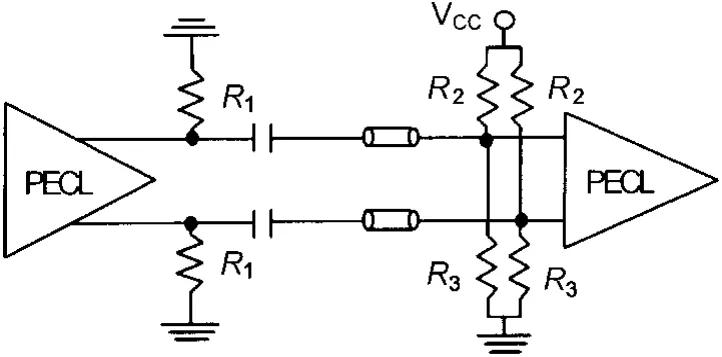

2.1.2 交流耦合

LVPECL與LVPECL的交流耦合方式如圖2所示。在交流耦合輸出到50 Ω的終端負載時,要考慮LVPECL的輸出端加一直流偏置電阻。LVPECL的輸出共模電壓需固定在Vcc-1.3 V,在選擇直流偏置電阻時僅需該電阻能夠提供14 mA到地的通路。LVPECL輸入直流偏壓應固定在 Vcc-1.3 V,輸入阻抗應該等于傳輸線阻抗。

圖2 LVPECL交流耦合電路

該電路需要滿足以下方程:

求解得:3.3 V 供電時:R1=142 Ω,R2=82 Ω,R3=130 Ω;

5 V 供電時 :R1=270 Ω,R2=68 Ω,R3=180 Ω。

然而這種方式給出的交流負載阻抗低于50 Ω,在實際應用中,3.3 V供電時,R1可以從142 Ω到200 Ω之間選取,5 V供電時,R1可以從 270 Ω到350 Ω之間選取,這樣輸出波形可以達到最佳。

2.2 LVPECL到CML的連接

2.2.1 直流耦合

在LVPECL到CML的直流耦合連接方式中,需要一個電平轉換網絡,如圖3所示。該電平轉換網絡的作用是匹配LVPECL的輸出與CML的輸入共模電壓。一般要求該電平轉換網絡引入的損耗要小,以保證 LVPECL的輸出經過衰減后仍能滿足CML輸入靈敏度的要求;另外還要求LVPECL端的負載阻抗近似為50 Ω。下面以CS1331的CML輸入為例說明該電平轉換網絡。

需要滿足以下方程組:

由于LVPECL的最小差分輸出擺幅為400 mV,而CS1331的輸入靈敏度為50 mV,因此電阻網絡的最小增益必須大于 50 mV/400 mV=0.125。當V cc=3.3 V時,求解上面的方程組,得到 R1=182 Ω,R2=82 Ω,R3=290 Ω,VA=1.35 V,VB=3.11 V,G=0.147,ZIN=49 Ω。LVPECL 到CS1331的直流耦合結構如圖4所示,對于其他的CML輸入,最小共模電壓和靈敏度可能不同,可以根據上面的考慮計算所需的電阻值。

圖4 LVPECL到LVDS的直流耦合電路

2.2.2 交流耦合

LVPECL到CML的交流耦合方式如圖5所示。根據2.2節的分析,需要在LVPECL兩個輸出端增加偏置電阻,當V cc=3.3 V時,電阻值選取范圍可以從142 Ω到 200 Ω。由于LVPECL的輸出信號擺幅大于CML的接收范圍,可以在信號通道上串一個電阻。當阻值為25 Ω時,CML輸入端的電壓擺幅變為原來的0.67倍。

圖5 LVPECL到CML的交流耦合連接電路

2.3 LVPECL到LVDS的連接

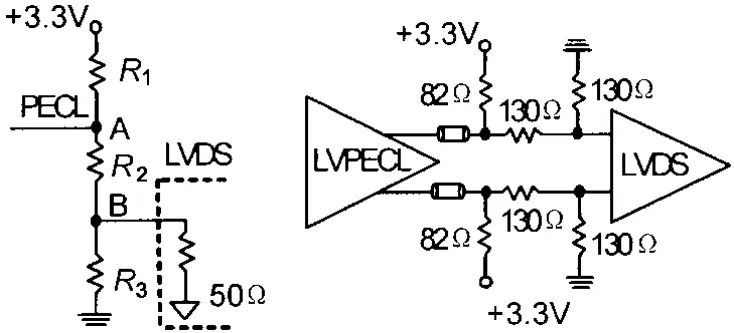

2.3.1 直流耦合

LVPECL到LVDS的直流耦合結構需要一個電阻網絡,設計該網絡時需要考慮以下幾點:首先,當負載是50 Ω接到Vcc-2 V時,LVPECL的輸出性能是最優的,因此考慮該電阻網絡應該與最優負載等效;然后還要考慮到該電阻網絡引入的衰減不應太大,LVPECL輸出信號經衰減后仍能落在LVDS的有效輸入范圍內。注意LVDS的輸入差分阻抗為100 Ω,或者每個單端到虛擬地為50 Ω,該阻抗不提供直流通路,這里意味著LVDS輸入交流阻抗與直流阻抗不等。LVPECL到LVDS的直流耦合所需的電阻網絡需滿足下面方程組:

解方 程 組得 :R1=82 Ω,R2=130 Ω,R3=130 Ω,VA=1.14 V,RAC=51.8 Ω,RDC=62.8 Ω,Gain=0.337。如圖4所示,假定LVPECL單端最小輸出電壓為300mV,在LVDS的輸入端可達到100mV,能夠滿足其靈敏度要求,如果LVPECL的最大輸出為1 V,LVDS的單端輸入電壓則為337 mV,同樣可以滿足指標要求。

2.3.2 交流耦合

LVPECL到LVDS的交流耦合結構如圖6所示,根據2.2節的分析,需要在LVPECL兩個輸出端增加偏置電阻,當V cc=3.3 V時,電阻值選取范圍可以從142 Ω到200 Ω。同時信號通道上一定要串接50 Ω電阻,以提供一定衰減。LVDS的輸入端到地需加5KΩ電阻,以提供近似0.86V的共模電壓(LVDS允許輸入共模電壓從0.2~2.2V范圍內變化)。

圖6 LVPECL到LVDS的交流耦合電路

3 交流耦合電容的選擇

當利用交流耦合結構時,耦合電容的選取應特別小心,該電容與負載阻抗一起構成高通濾波結構,非歸零的連0或連1出現時,電容會造成接收端電壓下降,產生過零點偏移,造成信號的抖動。

根據一階高通RC網絡的時域分析,經過計算:對于2.5 Gbps系統,當電容值為6.2 nF時,抖動為13 ps;當電容值為100 nF,抖動為1 ps;且電容值越大,抖動越小。但是實際的電容還需要考慮寄生阻抗,具體表現為寄生電阻(ESR)和寄生電感(ESL),寄生阻抗會導致信號產生反射;并且寄生阻抗越大,反射越強,嚴重降低信號的傳輸質量。在高頻傳輸的情況下,容值越大,寄生阻抗越大。因此,交流耦合電容的選擇并不是越大越好。對于2.5 Gbps的傳輸速率,采用10 nF的電容,可以取得較好的效果。

4 結束語

綜上所述,高速信號的互連通常有直流耦合和交流耦合2種方式實現。相對于交流耦合而言,多數情況下,直流耦合方案需要比較復雜的電阻分壓網絡匹配驅動端的輸出和接收端的輸入共模電壓。為了簡化電路設計,對于具有同種驅動電平的同類高速差分信號的互連建議采用直流耦合方式實現;其他互連情況建議采用交流耦合的方式實現。

[1]IEEE Standards Department:Draft Standard for Low Voltage Differential Sijnals(LVDS)for Scalable Coherent Interface(SCI),Draft 1.3 IEEE P1596.3-1995[S].

[2]ARSENAL CS1331/33/34/36/37/39 ASSP Hardware General Specification Issue 3.4 February 2[S],2007.

[3]Electrical Characteristics of Low Voltage Differential Signaling(LVDS)Interface Circuits(ANSI/TIA/EIA-644-A-2001),TR-30.2[S],March 1996.