一種基于FPGA的信號發生器設計實現

鄭 琴,魯 琴,宋承志

(武漢紡織大學 數學與計算機學院,湖北 武漢 430073)

一種基于FPGA的信號發生器設計實現

鄭 琴,魯 琴,宋承志

(武漢紡織大學 數學與計算機學院,湖北 武漢 430073)

應用VHDL語言及QuartusII軟件提供的原理圖輸入設計功能,結合電子線路的設計加以完成一個可應用于數字系統開發或實驗時做輸入脈沖信號或基準脈沖信號用的信號發生器,它具有結構緊湊,性能穩定,設計結構靈活,方便進行多功能組合的特點,經濟實用,成本低廉。

信號發生器;FPGA;QuartusII;VHDL語言

1 引言

隨著我國的經濟日益增長,社會對電子產品的需求量也就越來越大,目前,我國的電子產品市場正在迅速的壯大,市場前景廣闊。FPGA(Field Programmable Gate Array,現場可編程門陣列)在現代數字電路設計中發揮著越來越重要的作用。FPGA所具有的靜態可重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改,這樣就極大地提高了電子系統設計的靈活性和通用性,縮短了產品的上市時間并降低可電子系統的開發成本。

信號發生器是數字設備運行工作中必不可少的一部分,在傳統的信號發生器中,大都使用分立元件,而且體積龐大攜帶不便,且大部分只能輸出一種脈沖信號波形,而使用專用的數字電路設計的信號發生器,設備成本高、使用復雜。基于以上考慮,在中小型數字電路的設計和測試中,迫切需要設計一種小型易用成本低廉的信號發生器。

2 設計方案

利用VHDL編程,依據基本數字電路模塊原理進行整合。系統各部分所需工作時鐘信號由輸入系統時鐘信號經分頻得到,系統時鐘輸入端應滿足輸入脈沖信號的要求。組合波形信號經顯示模塊輸出。具備幅度和頻率可調功能,幅度可通過電位器調整,頻率控制模塊則是一個簡易的計數器,控制步徑為100HZ的可調頻率,最終送至脈沖發生模塊輸出脈沖信號,達到設計課題所要求的輸出波形頻率可調及幅度可調功能。幅度可調功能由于比較簡單,可以在FPGA外部利用硬件電路實現[2,3,8,9]。總體設計框圖如下圖1所示:

圖1 總體設計框架圖

采用VHDL語言來編程,然后下載文件到FPGA來實現。VHDL語言是電子設計領域的主流硬件描述語言,具有很強的電路描述和建模能力,能從多個層次對數字系統進行建模和描述,從而大大降低了硬件設計任務,提高了設計效率和可靠性,要比模擬電路快得多。該方案是利用FPGA具有的靜態可重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改,極大地提高了電子系統設計的靈活性和通用性,而且大大縮短了系統的開發周期。

3 軟件設計

3.1 波形產生模塊

本設計用VHDL語言根據傅立葉函數采集點進行掃描,分別產生正弦波、三角波和矩形波。以下介紹各種常用周期信號的傅立葉函數展開式[1,4,5,8,10,11]。

3.1.1 正弦波

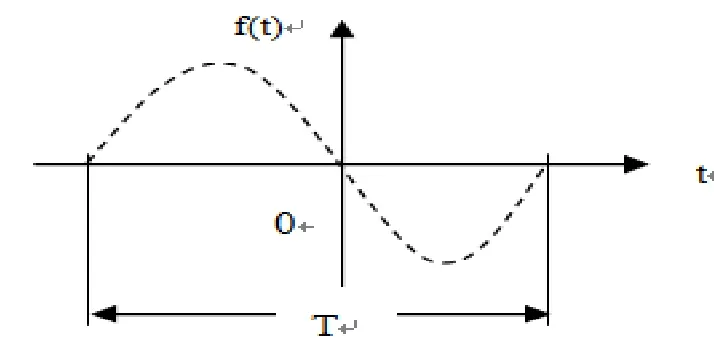

正弦波發生分為兩個步驟,即正弦波幅值采樣存儲和正弦波波形的還原輸出。幅值采樣是將一個周期正弦波進行64等分,如圖2所示,將64個采樣點進行量化處理,量化值=255*sin360/64(V),將64點量化值存入存儲器。正弦波形的產生是通過循環反復將存儲器中的64點采樣值通過DAC0832進行還原輸出,得到幅值正比于64點采樣值的正弦波。

3.1.2 矩形波

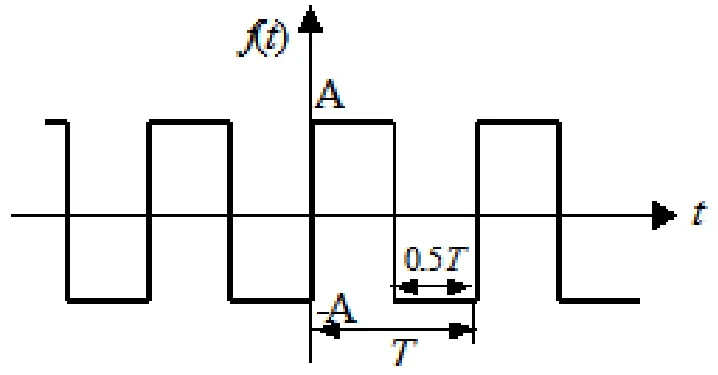

矩形波的實現較之正弦波發生簡單,由于矩形波是兩個電平值間的交替變換,因此波形采樣值的預存只要有兩個不同的數值就行了,為了使矩形波發生的頻率靈活可調,采用60個采樣值掃描輸出來實現,每半個矩形波周期采用三十個采樣值,循環反復將存儲器中的60點采樣值通過DAC0832進行還原輸出,得到幅值正比于點采樣值的矩形波。采樣圖如圖3所示。

3.1.3 三角波

由于三角波是線性的,比較簡單就可以產生,如果最低電壓設為15V,最高是255V,那么根據它的公式255/15=17,每個點的電壓只要依次加17就可以得到,一個波形所以采用簡單的加減算法就可實現,如圖4所示三角波的采樣圖。

3.1.4 基波

通過VHDL編程產生的正弦波、方波、三角波三種周期性波形即為基波。

圖5 頻率控制模塊流程圖

圖2 正弦波采樣圖

圖3 方波采樣圖

圖4 三角波采樣圖

圖6 選擇波形電路設計流程圖

3.1.5 諧波的產生

采用與基波產生的同樣原理,編程產生三種波形的諧波,所不同的是一個波形的周期采樣的點數不同,如果基波采樣點為63個,諧波采樣點數則為21個,其每點的電壓值為255*(sin360/60+sin360/20)(V),在對其進行循環掃描即可實現基波與諧波的線性疊加。

3.2 頻率控制模塊

系統要求頻率控制是在100HZ-1KHZ,步進為100HZ。在本題設計中只需借助FPGA便可完成。根據用戶需要的頻率[5,6,9],通過編程把頻率控制數值傳送給各個模塊,從而實現頻率的控制。如圖5所示。

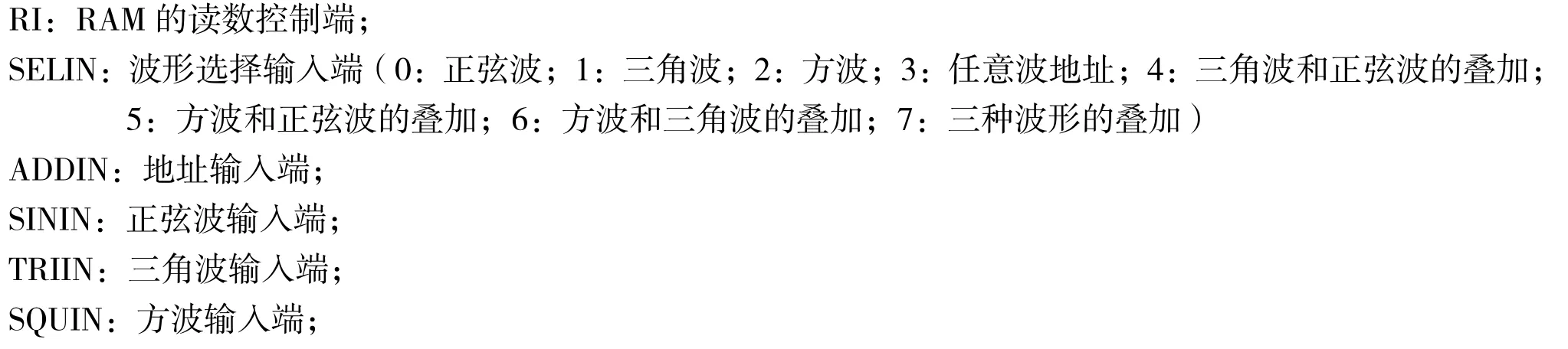

3.3 選擇波形模塊

這一部分主要是通過一個按鍵對波形進行循環選擇,按下確認按鈕后進行波形的調用。設計流程圖如圖6所示。

4 硬件電路設計

此次系統設計硬件部分通過 FPGA/CPLD實驗箱完成。為了避免干擾信號影響系統正常工作,未分配功能的FPGA引腳必須接地,在FPGA器件的電源端必須并連一0.01uF的退耦電容,在所有的輸入引腳上串聯100歐姆左右電阻減弱干擾信號影響,如有必要還應在輸入端設置上拉或下拉電阻。

4.1 濾波電路設計

圖7 濾波電路的設計

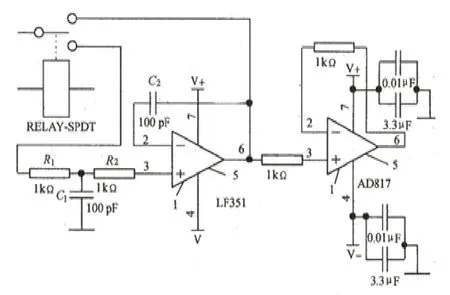

如圖7所示,設計D/A輸出后,通過濾波電路、輸出緩沖電路,使信號平滑且具有負載能力。

為保證穩幅輸出,選用 AD817,這是一種低功耗、高速、寬帶運算放大器 , 具有很強的大電流驅動能力。實際電路測量結果表明:當負載100Ω、輸出電壓峰-峰值10V時,帶寬大于500kHz,幅度變化小于土1%。

4.2 幅度控制電路設計

幅度控制電路采用一個電位器來控制波形的輸出幅度,電位器的型號為10K 歐。

5 系統調試

圖8 系統仿真波形

FPGA系統的軟硬件設計是緊密相連的,將軟件編譯綜合并且通過下載對FPGA進行適配,運行中的FPGA是由其內部的硬件結構控制讀出數據,從而產生波形。

系統仿真波形如圖8所示:

6 結論

系統以FPGA10K10器件為核心部件,可利用軟件編程實現了對D/A轉換信號的處理。努力做到了線路簡單、高性價比的特點,充分利用了軟件編程,彌補了硬件元器件的不足。

[1] 潘松,黃繼業. EDA技術實用教程(第二版)[M]. 北京:北京科學出版社,2005.2.

[2] 李小波,等.基于CPLD和單片機的低頻信號源設計[J]. 儀表技術與傳感器,2005, (11):46-48.

[3] 包明,等.基于FPGA的高速高精度頻率測量的研究[J]. 單片機與嵌入式系統應用,2003,(2):31-33.

[4] 王志鵬,付麗琴.可編程邏輯器件開發技術. Quartus II. 北京: 國防工業出版社,2005.3.

[5] 王道先. VHDL電路設計技術. 北京: 國防工業出版社,2004.1

[6] 候伯亨,顧新.VHDL硬件描述語言與數字邏輯電路設計[M].西安:西安電子科技大學出版社,2000.

[7] 曾繁泰.EDA工程的理論與實踐[M]. 北京: 電子工業出版社,2004.5.

[8] 尹佳喜,尹仕.基于CPLD的三相多波形函數發生器設計[J]. 電子工程師, 2005,(8).

[9] 高淼.基于FPGA的自治型SPWM波形發生器的設計[J]. 世界電子元器件, 2003,(10).

[10] 李剛強.FPGA設計中關鍵問題的研究[EB/OL]. http://www.edacn.net/viewarticle.php?id=27146,2005-10-15.

[11] Ralf N.Hardware/Software Co_designed for Data Flow Dominated Embedded System[M]. Kluwer Academic Publishers,1998.

The Design and Implementation of A Signal Generator based on FPGA

ZHENG Qin, LU Qin, SONG Cheng-zhi

(College of Mathmatics and Computer Science, Wuhan Textile university, Wuhan Hubei 430073, China)

VHDL language and QuartusII software application of the principle diagram provided input, combined with electronic circuit design function of the design to complete a can be used in the digital system development or experiment do input pulse signal or benchmark pulse signal with the signal generator, it has compact structure, stable performance, the structure design is flexible, convenient for the characteristics of the multi-functional combination, economic and practical, low cost.

FPGA; QuartusII; VHDL

TP302

A

1009-5160(2011)06-0061-04

鄭琴(1981-),女,講師,碩士,研究方向:計算機科學與技術.