數字視頻采集回放系統的SoPC設計

楊翠軍,錢 敏,曹云鵬,朱 靜

(蘇州大學 微電子系,江蘇 蘇州 215021)

0 引言

由于大規模集成電路(VLSI)、計算機和通信技術的迅速發展與結合,促進了視頻技術的進步與廣泛應用[1]。作為逐漸取代模擬視頻的數字視頻越來越受到人們的關注,日益成為一種廣泛應用的媒體,而其中數字視頻圖像采集是進行數字視頻處理技術的關鍵[2]。本文采用SoPC技術設計了一種嵌入式數字視頻圖像采集方案。可編程片上系統(System on Programmable Chip,SoPC)是Altera公司提出來的一種靈活、高效的SoC解決方案,是一種新的軟硬件協同設計的系統設計技術。它將處理器、存儲器、I/O口、LVDS、CDR等功能模塊集成到一個可編程器件上,構成一個可編程的片上系統[3]。本文利用該技術在FPGA芯片上配置NiosⅡ軟核處理器及相關接口模塊來實現硬件平臺,并利用Altera公司的軟件集成開發環境NiosⅡIDE進行軟件設計,控制整個采集流程,實現了數字視頻圖像的高速A/D轉換、存儲及顯示等功能。

1 PAL制數字視頻圖像

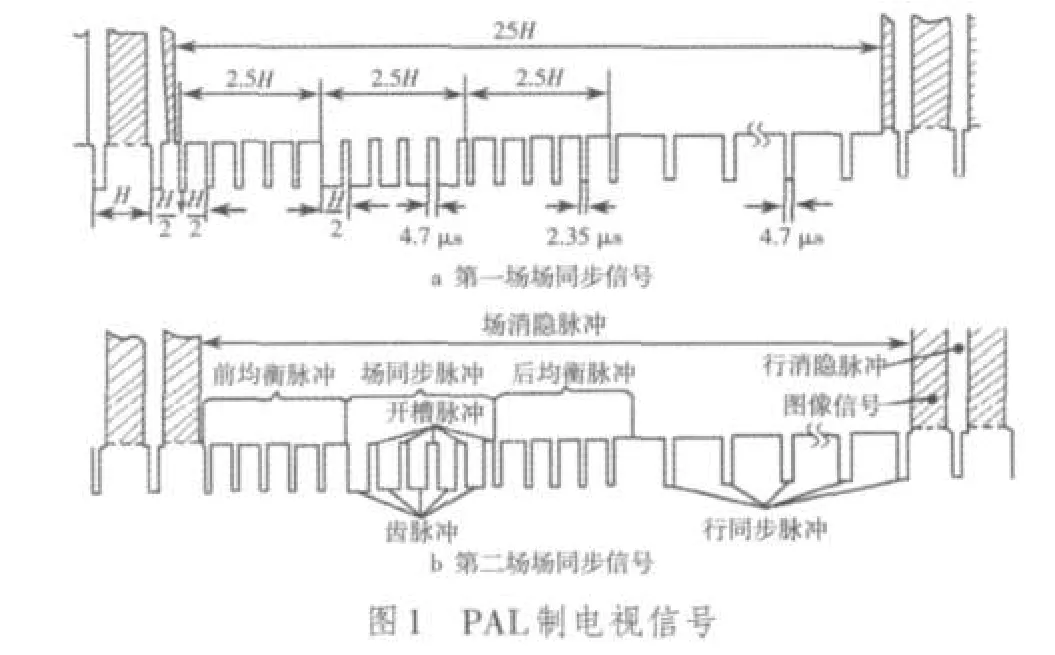

目前,世界上采用的電視信號制式主要有PAL制、NTSC制和SECAM制3種,中國采用的電視信號是PAL制。PAL電視制式規定,場掃描頻率為50 Hz,每幀圖像的掃描行數為625行。PAL制電視信號如圖1所示[4-5],圖中H為行同步信號的周期,標稱值為64 μs。

PAL制電視信號轉化為數字視頻信號后,數據格式一般符合ITU 656 YUV 4∶2∶2標準,其主要特征有:

1)25 f/s的幀率,每幀分為奇數場和偶數場。每幀掃描625行,其中有效圖像數據572行,每行采樣864個像素,其中有效像素720個。

2)有3個正交分量。亮度分量Y、色度分量U(Cb)和V(Cr),Y表示明亮度(灰度值),Cb和Cr表示色度(色彩及飽和度)。其中亮度分量Y每行采樣864次,色度分量Cr和Cb每行采樣432次。

3)8 bit或者10 bit的PCM編碼。量化時0和255用于同步;1~254表示采樣結果的PCM碼;對于亮度分量Y,16表示黑色,235表示白色;對于色度分量Cb/Cr,128表示沒有色度。

4)有3個信號用于同步輸出的數據。行同步信號、場同步信號和像素同步信號[6]。

2 采集模塊工作原理及硬件平臺構建

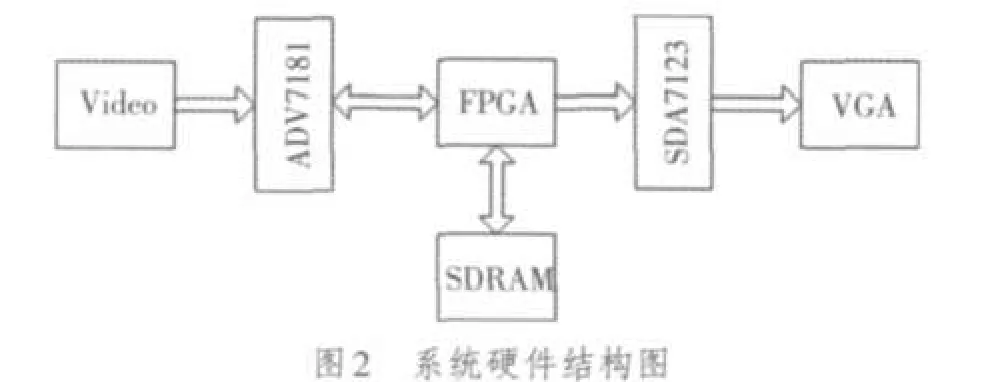

工作原理為:由視頻信號源輸出PAL制模擬信號,采集開始。首先由I2C配置好后的視頻解碼芯片ADV7181將輸入的模擬視頻信號進行解碼,輸出8 bit格式為YCbCr 4∶2∶2復合視頻數字信號,接著利用視頻圖像處理模塊對視頻數字信號進行4∶2∶2到4∶4∶4的格式轉化,YCbCr到RGB色彩空間的轉換等處理,再通過視頻編碼芯片SDA7123進行D/A轉換,最后在VGA監視器上顯示出來。

本文選用Altera CycloneⅡ系列EP2C35型號的FP?GA芯片。該芯片具有33 216個邏輯單元、475個用戶自定義I/O接口、35個嵌入式乘法器和4個鎖相環。在FP?GA中設計了以下模塊:PLL、NiosⅡ嵌入式軟核處理器、掛接在Avalon總線上的JTAG UART,PIO,Timer,System ID,SDRAM Controller,Flash(CFI)Controller等內核以及用戶定制的邏輯外設模塊freedev_i2c,serial_segment,freeedev_bt656,freedev_sram。在FPGA外圍有視頻解碼芯片ADV7181,用于存儲的SDRAM,視頻編碼芯片SDA7123等。圖2為系統硬件結構圖。

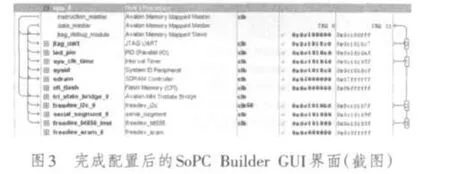

在系統硬件平臺中,嵌入到FPGA的處理器和各接口模塊是設計的關鍵。利用Altera公司的QuartusⅡ軟件中集成的SoPC Builder開發工具來創建設計基于處理器、外圍設備和存儲器的嵌入式系統將大大縮短整個設計周期。下面主要對NiosⅡ軟核處理器、ADV7181及其I2C配置、視頻圖像采集模塊、視頻圖像解碼及顏色轉換模塊等幾個關鍵模塊的設計進行介紹。

2.1 NiosⅡ軟核處理器

NiosⅡ處理器是Altera公司推出的第二代用于可編程邏輯器件的可配置的軟核處理器。由于處理器是軟核形式,具有很大的靈活性,因此,可以在多種系統設置組合中進行選擇,達到性能和成本的要求[7]。NiosⅡ處理器系列包括三種內核:高速內核(NiosⅡ/f)、經濟內核(NiosⅡ/e)、標準內核(NiosⅡ/s)。本文采用的CycloneⅡ系列的EP2C35芯片邏輯資源十分豐富,加上采集系統實時處理對CPU的性能要求較高,因此選用了高性能的NiosⅡ軟核作為本系統的CPU。接著再完成其他外設模塊的添加,即完成了嵌入式系統的設計。圖3為完成配置的SoPC Builder GUI界面。

2.2 ADV7181及其I2C配置

本文采用ADV7181芯片來完成模擬視頻信號的A/D轉換。ADV7181是Analog Device公司推出的一款高性能的集成視頻解碼芯片,能自動檢測并轉換標準NTSC,PAL和SECAM制式的電視信號為8 bit或16 bit的YCb?Cr 4∶2∶2復合數字視頻。

ADV7181支持I2C串行總線接口,通過I2C接口對芯片內部相關控制寄存器進行配置。圖4為I2C總線傳輸時序。本文中的freedev_i2c模塊是用戶自定制邏輯實現的,編寫verilog代碼,實現I2C協議,并通過Avalon總線接口與NiosⅡ軟核處理器相連。

2.3 視頻圖像采集模塊

freeedev_bt656模塊對ITU-R BT.656 YCrCb 4∶2∶2格式的數字碼流進行采集處理,并作為用戶自定義外設掛接在Avalon總線上。因此,模塊的端口要符合Avalon接口規范,分為主端口和從端口。主端口為發起傳輸的Avalon信號類型的集合,從端口為響應傳輸請求的Ava?lon信號類型的集合。freeedev_bt656模塊通過slave port來設置模塊工作參數和模式,視頻采集部分以輸入視頻時鐘采集數據并緩存到視頻FIFO中,master port部分讀視頻FIFO中的數據,并支持突發式傳輸將數據存放到內存中,從而實現視頻圖像的采集與存儲。

2.4 視頻圖像解碼及顏色轉換模塊

本文中的Tv_to_VGA模塊完成視頻圖像的解碼及顏色轉換功能。從ADV7181輸出數字碼流的格式為ITU-R BT.656 YCrCb 4∶2∶2,即每采4個亮度信號,就各采樣2個色差信號。因此在顏色變換之前,采用“nearest neighbor”[8]像素縮放方法,即通過復制相鄰采樣點的色差信號的方法將其格式轉化為YCrCb 4∶4∶4。視頻圖像輸出部分的設計采用了SDA7123視頻D/A轉換器,實現數字RGB轉換為模擬RGB(VGA)信號輸出的功能,因此在Tv_to_VGA模塊中也要完成YCrCb到RGB顏色空間轉換的功能,輸出8 bit的數字RGB信號、行場同步信號和VGA時鐘及消隱等信號,將這些信號送給SDA7123芯片進行D/A轉換,最后送給VGA監視器。

3 采集模塊的軟件設計

系統的軟件設計是在NiosⅡ集成環境下完成的,NiosⅡ集成開發環境(IDE)是NiosⅡ系列嵌入式處理器的基本開發工具。設計中以C語言的形式并利用IDE集成環境提供的硬件抽象層(HAL)的函數來完成軟件程序的編寫。

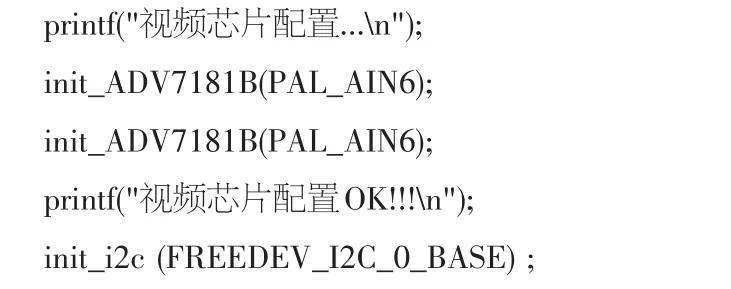

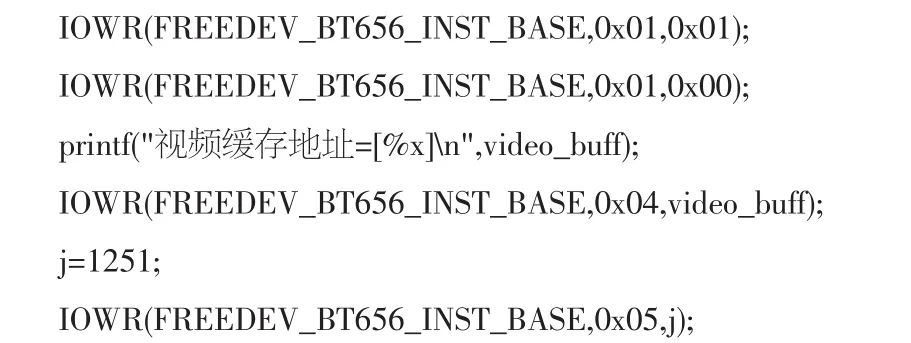

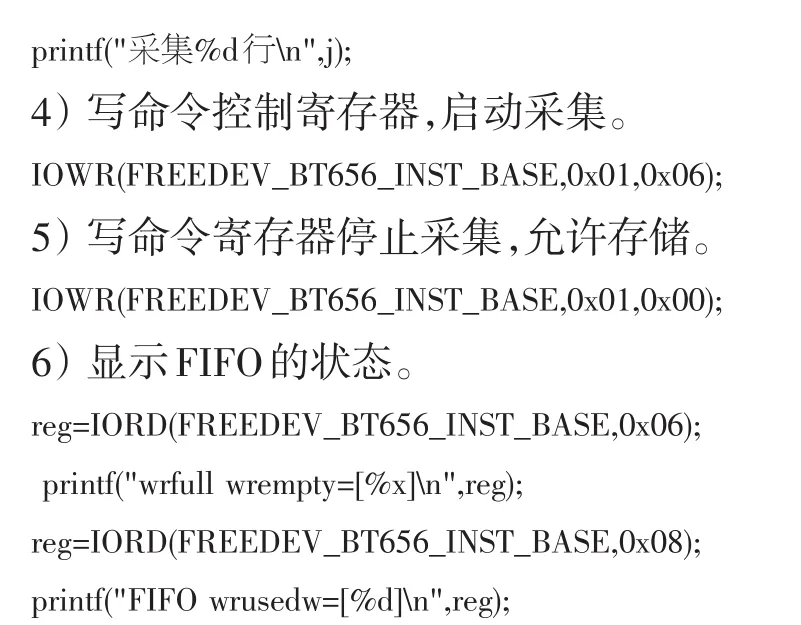

在采集系統啟動后,首先初始化視頻I2C控制器,對ADV7181進行配置初始化以及清空FIFO緩沖器等,接著寫命令寄存器,啟動采集。在采集過程中,通過讀FIFO的狀態,并利用printf函數輸出就可以在IDE界面的Con?sole控制臺中查看采集過程中FIFO的即時狀態,程序中幾個主要部分如下:

1)按照PAL的設計要求對ADV7181B相關寄存器進行配置。

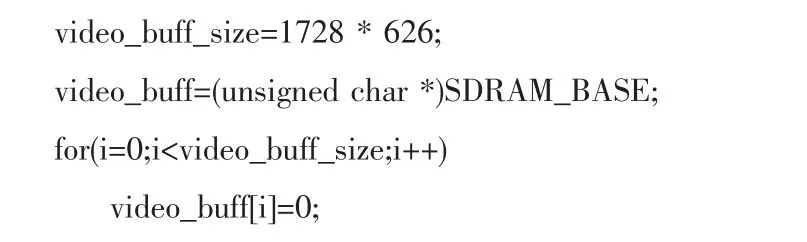

2)在SDRAM中開辟視頻緩存空間,定義其大小,并將其初始化為0。

3)寫命令控制寄存器,禁止采集和存儲,并清空FIFO。

4 采集系統測試及結論

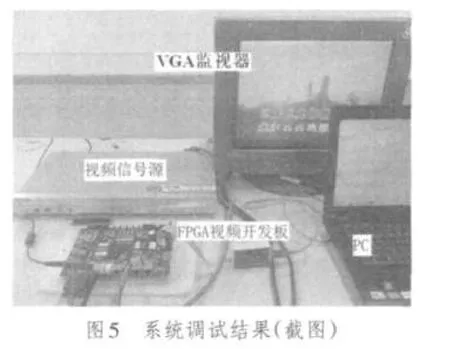

在實驗室條件下對系統進行測試。啟動系統,開啟視頻源進入視頻采集處理過程,并最終在VGA監視器上顯示出穩定清晰的視頻圖像,圖5為系統調試結果。

在采集過程中使用Altera SignalTapⅡ嵌入式邏輯分析儀對FPGA信號及狀態進行檢測,圖6為SignalTapⅡ檢測波形,其中A處的YCrCb 4∶2∶2碼流為連續的80h10h,表明此時段正處于視頻消隱階段,B處表明在消隱階段解碼后RGB輸出00h,C處表明一個行同步信號的使能,分析得到檢測波形符合設計的要求。

本文采用SoPC技術,通過在CycloneⅡFPGA芯片上配置NiosⅡ軟核處理器及相關接口模塊來實現硬件平臺,并利用Altera公司的軟件集成開發環境NiosⅡIDE進行軟件設計來控制整個采集流程。實現了數字視頻圖像的高速A/D轉換、存儲及顯示等功能。由于采用SoPC技術,模塊具有設計靈活、采集速度快和擴展升級性好等優點。

[1]黎洪松.數字視頻技術及其應用[M].北京:清華大學出版社,1997.

[2]聶飛,馮宗哲,郭寶林,等.嵌入式視頻采集系統的實現方法研究[J].電視技術,2003,27(8):46-49.

[3]周立功.SOPC嵌入式系統基礎教程[M].北京:北京航空航天大學出版社,2006.

[4]宋承杰,王景存.基于FPGA的視頻字符疊加的設計與實現[J].電視技術,2009,33(12):24-27.

[5]劉韜,樓興華.FPGA數字電子系統設計與開發實例導航[M].北京:人民郵電出版社,2005.

[6]錢敏,李富華,黃秋萍,等.基于HDL的PAL制數字視頻圖像采集控制器設計[J].微電子學與計算機,2007,24(12):191-194.

[7]王曉迪,張景秀.SOPC系統設計與實踐[M].北京:北京航空航天大學出版社,2008.

[8]JACK K.Video demystified[M].Burlington:Newnes,2005.