基于ADV7125的嵌入式系統VGA接口設計

鄭佃好,張紅雨,張洪斌

(電子科技大學電子工程學院,成都611731)

鄭佃好(碩士研究生),主要研究領域為嵌入式系統設計、射頻識別、模糊控制。

引 言

目前VGA接口是計算機系統以及智能儀器中重要的標準輸出接口,但是大部分硬件系統選擇LCD終端輸出。很多顯示設備,如常見的CRT或LCD顯示器一般都采用統一的15針VGA顯示接口。如需要外接這些設備,則需要把LCD輸出信號的接口轉換為VGA接口。本設計是在三星公司芯片 S3C2440平臺下,利用最高頻率可以達到330 MHz的ADV7125芯片,設計了能夠把輸出的LCD信號轉換為VGA信號的轉換電路。該設計方案具有電路簡單、價格低廉、輸出圖像清晰穩定等特點。

1 ADV7125芯片介紹

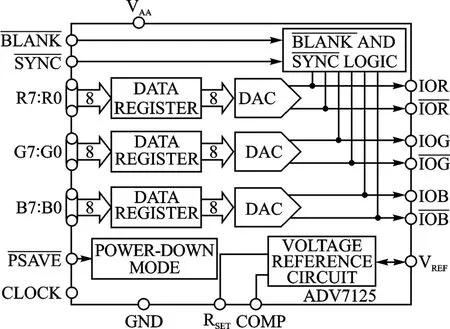

ADV7125是一款單芯片、3通道、高速度的數模轉換器。內置3個高速、8位、帶互補輸出的視頻DAC、1個標準TTL輸入接口,以及1個高阻抗、模擬輸出電流源。它具有3個獨立的8位寬輸入端口。只需1個+5 V/+3.3 V單電源和時鐘便能工作。ADV7125還具有其他視頻控制信號:復合同步信號控制端消隱信號控制端以及省電模式控制端。它能夠與各種高分辨率彩色圖形系統兼容[1]。ADV7125功能框圖如圖1所示。

ADV7125有3個視頻數據寄存器DATA REGISTER和一個視頻控制寄存器POWER-DOWN MODE。數據寄存器的3個輸入端分別連接紅綠藍三色的數字視頻信號,數據寄存器后面緊跟數模轉換單元,將數字信號轉換為模擬信號;控制寄存器將數字的消隱信號、同步信號轉換合并。數模轉換后的模擬視頻信號和控制寄存器輸出的同步、消隱控制信號共同作為ADV7125的輸出信號,此輸出信號大小受Rset端和地之間接入的外加電阻RSET大小的控制。

圖1 ADV7125功能框圖

2 ADV7125芯片用于VGA轉換的基本原理

ADV7125芯片用于VGA轉換的基本原理是,將S3C2440輸出的數字視頻信號轉換為模擬的VGA輸出信號,模擬的VGA輸出信號的大小受ADV7125芯片外圍參考電壓VREF和外加電阻 RSET的控制,(VREF和 RSET的具體接法如圖4所示)其關系如下:

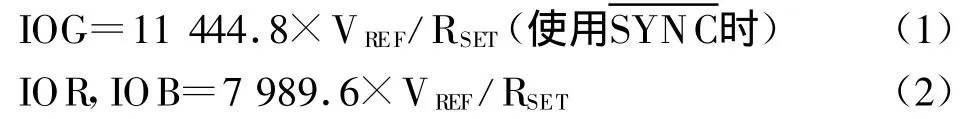

式中IOG、IOR、IOB分別代表綠、紅、藍三色信號的幅度。當不用復合同步信號時,需要把端連接低電平,這時IOG的關系式同式(2)。

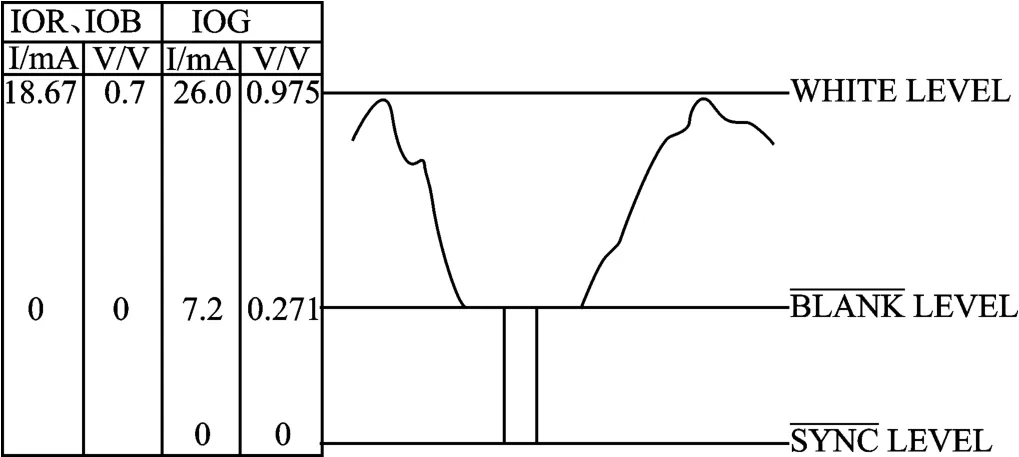

圖2 ADV7125的端 對輸出視頻信號的影響

表1 典型的視頻輸出真值表

對應圖2和表1可得到以下結論:

①當IOR、IOG 、IOB三端的DAC輸入為0x00時,代表屏幕最黑,此時對應圖2為對應表1為第7行。從圖2左面列表可以看到,IOR、IOB端的電流、電壓分別是0mA、0V,IOG端的電流、電壓分別是7.2 mA、0.271 V。即電流相差7.2 mA。

②當IOR、IOG、IOB三端的DAC輸入為0xFF時,代表屏幕最白,此時對應圖2為WHITE LEVEL,對應表1為第2行。從圖2左面列表可以看到,IOR、IOB端的電流、電壓分別是18.67 mA、0.7 V,IOG端的電流、電壓分別是26.0 mA、0.975 V。即電流相差7.3 mA。

從表1,可以得到以下的結論:

面對這種情況,依托學校資源,由不同所有制經濟主體共同出資成立獨立經濟實體,實現決策、培養、評價、改進的混合所有制經濟,應該是一種不錯的校企合作培訓模式。它突破了合作方各自為政的教育模式,實現了從理念、決策、培養方案到資源調配的統一,有利于校企合作培養模式的質量升級。

3 VGA接口設計

根據需要,把LCD信號轉換為VGA信號,轉換時必須根據VGA信號的時序進行轉換。VGA信號一共包括5部分,分別是紅(R)、綠(G)、藍(B)三色信號和行(H)、場(V)同步信號,紅(R)、綠(G)、藍(B)三色信號和行(H)、場(V)同步信號根據S3C2440的配置時序,由S3C2440以數字信號的形式輸出,之后由ADV7125對紅(R)、綠(G)、藍(B)三色信號進行轉換,行(H)、場(V)同步信號直接進入VGA接口中,不需要轉換。下面分別介紹VGA信號的時序、硬件連接、軟件設計以及注意事項。

3.1 VGA時序信號

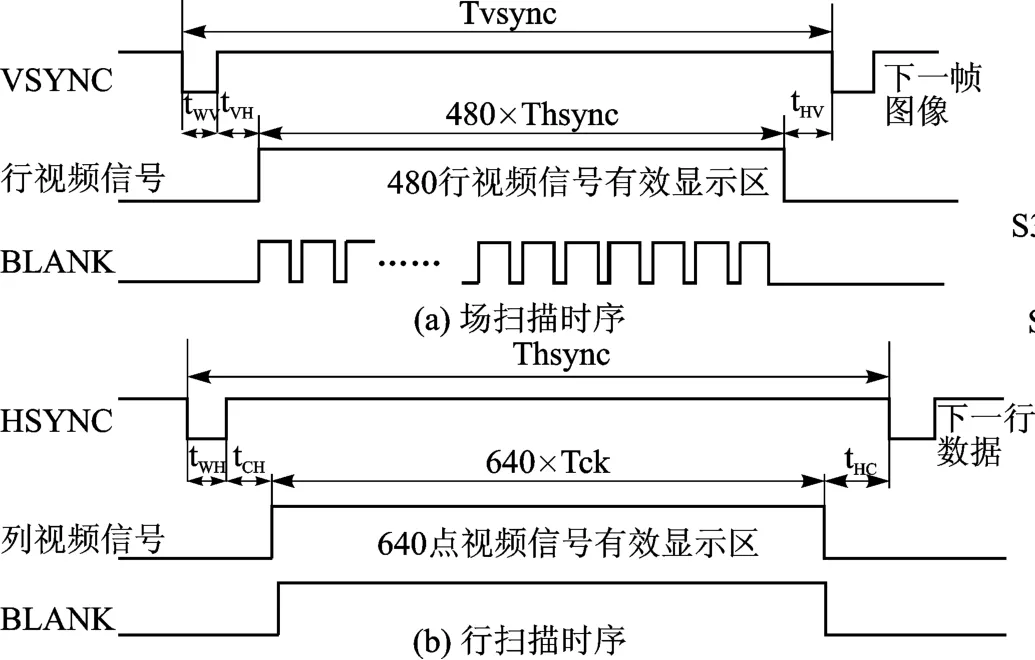

以分辨率為640×480、刷新頻率為60 Hz、16位的彩色顯示模式為例,VGA信號的掃描時序如圖3所示。

圖3 VGA信號掃描時序圖

在場掃描時序中,VSYNC為場同步信號,Tvsync是指顯示器掃描1幀完整畫面需要的時間,大小為16 667 μ s;VSYNC信號每場有525行,其中480行為有效顯示行,45行是場消隱期。場消隱期包括場同步時間(低電平場同步脈沖)tWV(2行/63 μ s)、場消隱前肩tHV(13行/412 μ s)、場消隱后肩 tVH(30 行/952 μ s),共 45 行 。

在行掃描時序中,HSYNC為行同步信號,Thsync是指顯示器掃描一行需要的時間,大小為31.75 μ s,該周期通過Hsync(行同步脈沖)來同步,脈沖的寬度tWH=3.81 μ s。每顯示行包括800點,其中640點為有效顯示區,160點為行消隱期(是非顯示區)。行消隱期包括行同步時間tWH(3.81 μ s),行消隱前肩 tHC(0.516 μ s)和行消隱后肩tCH(1.786 μ s),共 160 個點時鐘 。

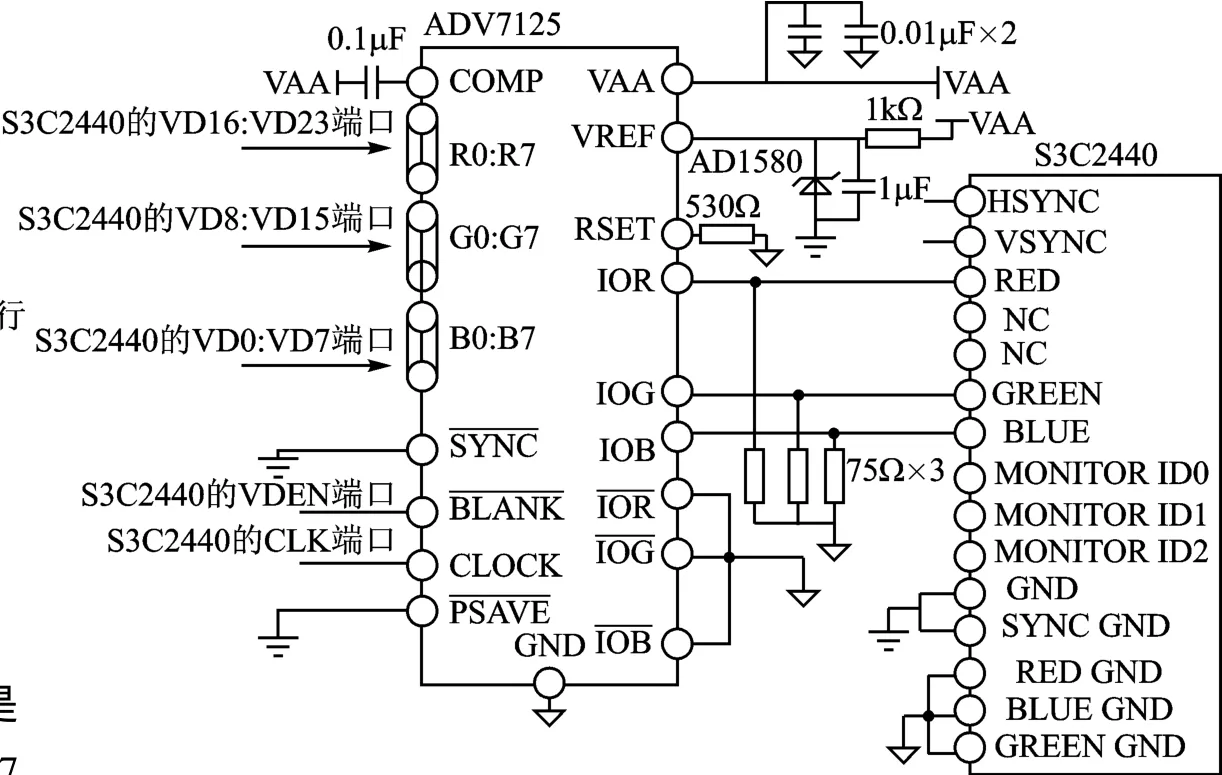

3.2 S3C2440和ADV7125的電路連接

設計中主要使用S3C2440處理器的 LCD控制器接口,它主要通過 DMA方式占用系統總線,支持彩色 TFT液晶屏,支持 16 bbp無調色真彩。LCD接口數據的低8位,中間8位和高8位分別與 ADV7125芯片的BLUE信號、GREEN信號和 RED信號相連,這樣就完成了S3C2440處理器與ADV7125芯片之間數字信號的傳輸。ADV7125芯片的時鐘信號采用LCD接口的時鐘信號,信號與VM(VSDN)信號相連接,SYNC同步信號接地。COMP端用于內部參考運放的補償,用 0.1 μ F的陶瓷電容連接在COMP與模擬電源VAA之間,防止自激振蕩以增加穩定性。采用AD1580作為參考電壓,AD1580輸出信號穩定,能夠很好地滿足電路設計的需要。RSET引腳與地之間接一個530 Ω的電阻,用來控制視頻信號的滿幅度。在圖像系統中,不會自動產生復合同步信號利用本設計可以實現視頻同步信息編碼直接進入綠色信道。如果不需要,把輸入端與邏輯低電平相連。S3C2440和ADV7125的電路連接如圖4所示。其中 VD0、VD1、…VD23、VDEN 、CLK 、HSYNC、VSYNC為S3C2440的輸出端。

圖4 ADV7125和S3C2440的電路連接

3.3 電路連接需要注意的問題

ADV7125可以用于灰度視頻信號輸出。例如:僅用于1個通道進行視頻輸出,這時其他兩個不用的視頻數據信道都應該與邏輯0相連,不用的模擬輸出應該與使用的信道一樣連接相同的負載。

為了實現ADV7125的最優噪聲性能,對PCB的設計必須特別注意。ADV7125電源和地線上的噪聲應該優化。可以通過屏蔽數字輸入和提供好的退耦達到這一點。VAA和GND的引線長度應該盡量短,這樣可以減小電感環路。在設計PCB時應盡量把模擬地與數字地分開,地線應該通過1個磁珠與PCB大面積鋪地相連,并且磁珠應該盡可能的靠近ADV7125器件的地引腳。電路中使用的電容應該盡可能的靠近對應引腳,,并且電容的引線應該盡可能的短,這樣可以減小引線電容。由于使用頻率非常高,時鐘引線應盡可能地短,這樣可以減小噪聲的抖動。視頻輸出信號應該由數字地平面覆蓋,這樣可以增大高頻電源抑制比。

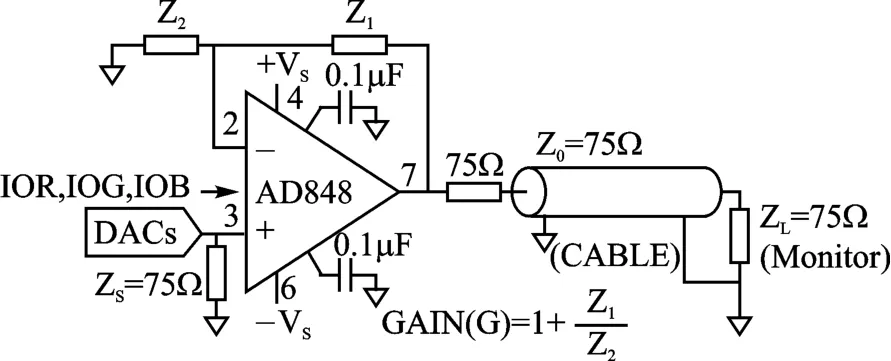

由于模擬RGB信號采用高阻電流源輸出方式,可以直接驅動75 Ω的同軸傳輸線。長于10 m的電纜可能會對高頻模擬輸出脈沖衰減。使用輸出緩沖可以補償電纜的失真。這些緩沖器在整個輸出電壓擺幅期間,必須有足夠的電流。常見的有AD84x系列的單片運放。在較高的頻率下(如80 M Hz),推薦使用AD848。其典型增益電路如圖5所示。

圖5 VGA信號長距離傳輸的典型增益電路

通過簡單的計算可以得知其增益為:GAIN=1+Z1/Z2。改變緩沖電路的增益器件Z1、Z2來滿足所要求的視頻電平。

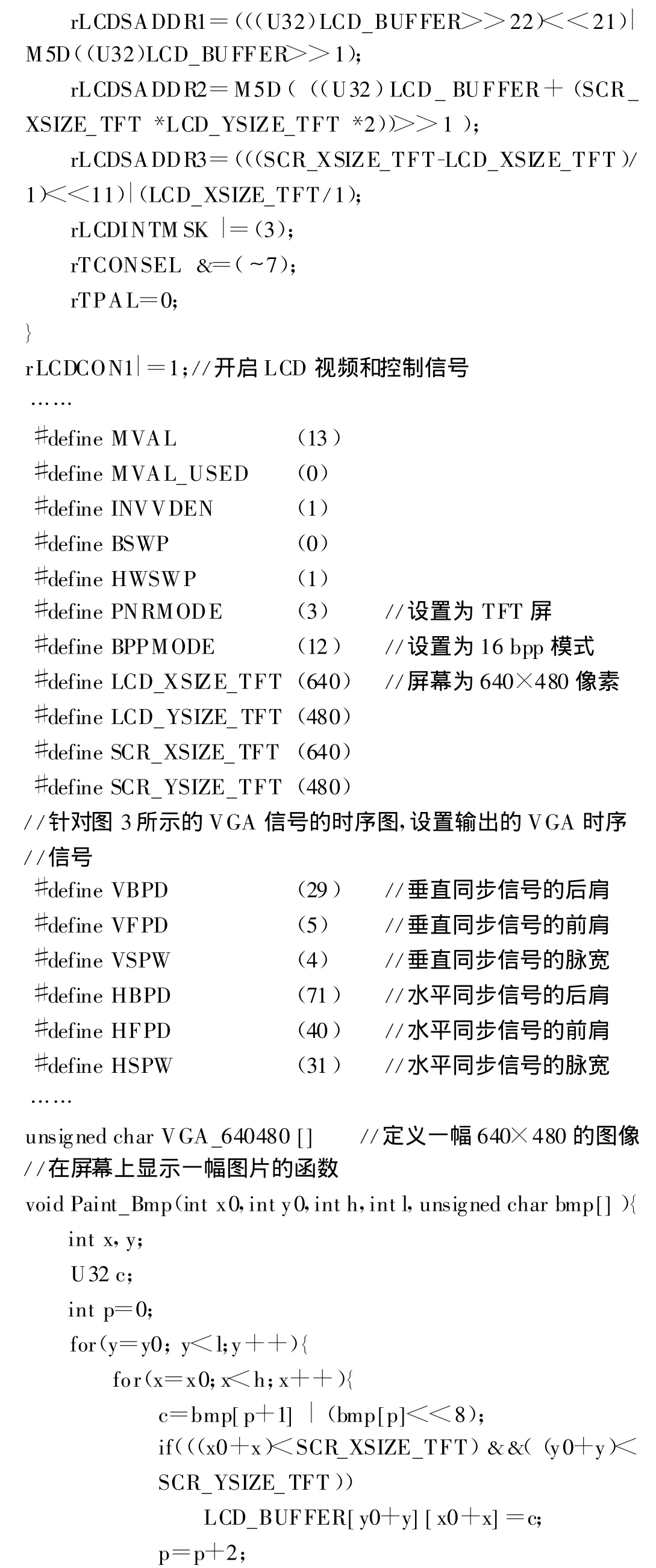

3.4 相關的軟件設置

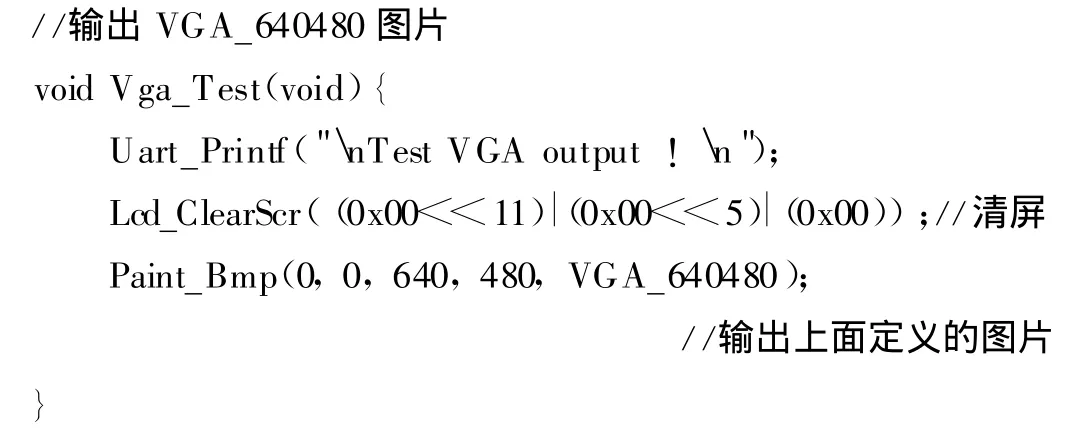

下面以簡單的測試程序為例來說明相關軟件的編寫。

軟件設計的基本流程如圖6所示。具體過程如下:

①首先對LCD的功能寄存器進行初始化,主要設置LCD控制寄存器1~5,LCD緩沖區起始地址控制寄存器;屏蔽LCD中斷。

②其次對LCD的輸出時序(VGA信號時序)進行設置。設置分辨率、周期、前(后)信號、同步脈沖。

③再次是對視頻信號進行設置,主要是使能LCD視頻信號的輸出。

④用一幅圖像的輸出來測試VGA的顯示是否正常。

主要代碼如下所示:

圖6 軟件設計流程

結 語

本文結合S3C2440處理器和ADV7125芯片的特點,介紹了LCD轉VGA方案,該方案簡單易行,適用于嵌入式系統設備的VGA信號輸出。ADV7125芯片有多種頻率可供選擇。本設計也可以用于灰度級輸出的信號中,在此基礎上進行一些簡單的修改,可以滿足高分辨率,高刷新頻率的環境要求。

[1]ADV7125芯片數據手冊[OL].[2011-03].http://www.analog.com/static/imported-files/data_sheets/ADV7125.pdf.

[2]王恒心,熊慶國.基于FPGA/CPLD的嵌入式VGA顯示系統[J].微計算機信息,2008,24(9-2):146-148.

[3]喬義川,馮麗輝.一種基于S3C2410的LCD轉VGA簡易技術方法研究[J].云南師范大學學報,2009,29(4):42-45.

[4]范金龍,王景中.基于CH7004的嵌入式系統VGA接口設計[J].電子設計工程,2009,17(9):6-8.