嵌入式WinCE平臺下的頻譜數據傳輸控制

韋晏旭,王志剛,羅光坤

(電子科技大學自動化工程學院,成都611731)

韋晏旭(碩士生),研究方向為 ARM+WinCE+FPGA、VC++6.0、智能儀器軟件開發技術等。

引 言

頻譜分析儀是微波測量儀器中最基礎、最常用的儀器之一,被譽為頻域示波器,廣泛應用于電子對抗、航空航天、移動通信、廣播電視、科研生產等各種領域,是軍用和民用電子測試不可或缺的設備[1]。隨著現代科研向精、深和尖的方向發展,頻譜測量在各領域內發揮的影響越發顯得深遠。目前,頻譜分析儀的開發在國內也處于前沿陣地。綜合起來看,由于超外差式頻譜分析儀在分析射頻或微波毫米波范圍內的高頻信號頻譜上具有明顯優勢,本文便采取了這種由射頻前端、數字掃頻、中頻濾波、視頻檢波以及頻譜數據實時采集與顯示的整機設計方案。

現代頻譜儀除了對測量精度和測頻帶寬要求越來越高外,同時也更加強調低成本、便攜性以及可靠性。那么,智能儀器開發中就客觀要求在不影響其測量性能的前提下構建一種滿足這種新需求的軟硬件平臺。頻譜儀在實際測量中,需要實現頻譜數據在儀器顯示屏上的實時刷新,那么頻譜數據的實時采集就顯得尤為重要。

WindCE作為保護模式的操作系統,運行其上的應用程序只能訪問系統管理的虛擬內存地址。本文在以總線方式進行數據訪問操作時,首先完成外部設備的物理地址到系統內存地址虛擬映射[2],從而使外部數據FIFO所構成的緩存邏輯成為可操作的設備單元。其次,由于頻譜儀掃頻時間過程是根據前端射頻、中頻及濾波器等硬件特性決定的,頻譜數據的產生快慢受到掃描時間的限制,掃描時間越長則經過FFT或者濾波及檢波算法后的數據在緩存FIFO中的寫入速度就越慢。為了滿足頻譜數據的實時讀取和顯示,ARM與FPGA間的數據通信利用頻譜數據的實時有序讀取機制。

1 系統概述

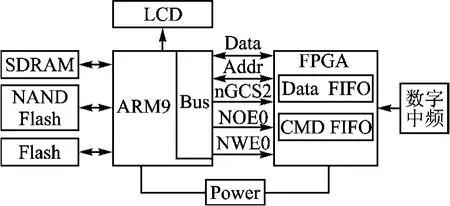

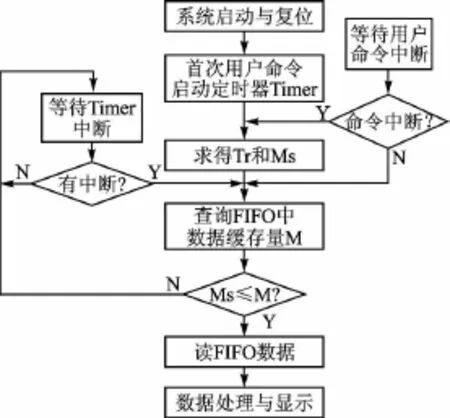

該平臺使用的主控CPU型號為Samsung公司具有ARM9內核的 S3C2440A,用于頻譜數據濾波、檢波等。數據緩存FIFO用的FPGA為Xilinx公司的Spartan 3AN,SDRAM與NAND Flash均為64 MB,Flash存儲設備支持SD卡和USB存儲。軟件層采用了WinCE 5.0作為操作系統平臺。WinCE系統的應用程序只能訪問虛擬地址,當.exe可執行代碼裝載入內存時,通過地址重定位實現了地址映射,使之能夠訪問實際的外設物理地址[3]。在數據實時采集過程中,為了滿足有序讀取的要求,在FPGA中設計獨立的FIFO數據緩存單元和記錄其中數據緩存量的RAM單元。通過實時監測RAM中的數據量記錄值,以保證監控程序依據掃頻及硬件處理的頻率掃描時間完成實時適量數據采集過程。嵌入式ARM頻譜儀系統數據采集平臺結構框圖如圖1所示。

圖1 系統數據采集平臺結構框圖

2 頻譜數據緩存FⅠFO的訪問機制

2.1 內存管理機制

WinCE5.0是保護模式下的基于優先級的多任務32位操作系統[8],因此WinCE系統的虛擬尋址能力可達到4 GB。但是與桌面Windows操作系統的內存管理相比,其虛擬內存管理是獨特的。Windows XP的每個進程獨享4 GB的虛擬地址空間,而WinCE中所有進程共享一個4 GB的虛擬地址空間。這4 GB的虛擬地址空間又被分為兩個2 GB區域:低地址2 GB是用戶空間,為應用程序所使用,應用程序申請的內存都會從低2 GB地址空間中返回;高地址2 GB是內核空間,供WinCE操作系統本身使用[2]。

從0x8000 0000開始是WinCE內核使用的虛擬地址空間。虛擬地址0x8000 0000~0x9FFF FFFF是帶緩沖的虛擬內存,用來靜態映射所有的物理地址;而虛擬地址0xA000 0000~0xBFFF FFFF是不帶緩沖的,它會重復映射所有的物理內存,如圖2所示。由于在驅動程序中會直接訪問設備I/O或者寄存器,就要使用0xA000 0000這段物理地址。

圖2 內核映射的物理內存

2.2 內存映射的實現

2.2.1 映射關系

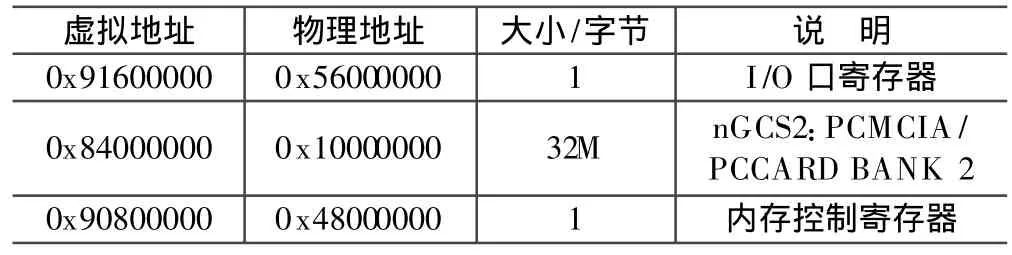

在ARM處理器中,WinCE的靜態內存映射關系是由OAL層中的 OEMAddress-Table數組決定的,如表 1所列。當選擇NGCS2作為外設的片選信號時,其有效的物理內存起始地址是0x1000 0000,對應的虛擬內存起始地址為0x8400 0000;地址空間對應關系為128 MB與32 MB。通過這個映射表還可以看到I/O和內存控制器的映射。由于內存的虛擬映射只能選擇無緩沖區,故其虛擬映射首地址都必須再增加0x2000 0000,分別成為 0xB160 0000、0xA400 0000 、0xB080 0000 。

表1 OE MAddress-Table

2.2.2 映射實現

虛擬內存映射主要用到3個API函數:VirtualAlloc、VirtualCopy和VirtualFree。VirtualAlloc函數申請虛擬內存,用于在本進程的虛擬地址空間中申請一塊空間;VirtualCopy完成外設物理地址與虛擬空間地址的綁定;而VirtualFree用來釋放所申請的進程虛擬空間,以及映射綁定關系[4]。具體映射步驟為:映射I/O控制寄存器→配置片選信號→映射內存控制器→配置位寬、時序等→映射FPGA中的外設端口地址[3]。

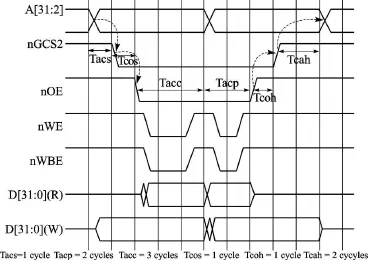

2.3 ARM與FPGA通信時序邏輯

在程序實現時,為了提高程序的模塊化和可移植特性,自定義兩個讀寫FPGA中數據緩存FIFO的接口函數:UINT ReadEXDevice(const int port)和void WriteEXDevice(const int port,unsigned short data)。Port號為程序讀寫數據FIFO的地址端口號,通過映射關系,相應虛擬地址的片選信號nGCS2有效。當設置Data Bus的數據寬度是 32位時,則Address Bus的有效地址線為 A2~A31。讀寫使能信號nOE與nWE連同地址信號在FPGA中經邏輯譯碼,實現了對FIFO和RAM的有序訪問。時序過程參考總線訪問時序圖,如圖3所示。

3 數據讀取機制

3.1 頻譜測量數據緩存及實時監測

FPGA中數據緩存FIFO以及緩存量記錄單元RAM的邏輯設計,解決了ARM與DSP、濾波檢波邏輯模塊之間數據的跨時鐘域傳輸以及實時監測數據緩存量的問題。設計的FⅠFO為頻譜數據緩沖FⅠFO,數據位寬為32位,數據緩存深度為1024個單元;記錄數據量的RAM單元類似一個寄存器,ARM通過總線方式訪問其地址空間即可得到其中的記錄值,作為實時讀取量的判斷依據。這兩者的設計均可在Xilinx ISE集成開發環境下通過調用IP Core實現[6]。

圖3 總線訪問時序圖

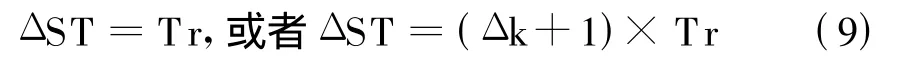

3.2 掃描時間及讀取次數與單次讀取數據量的關系

頻譜儀的射頻前端、掃頻、中頻處理以及RBW和VBW各處理環節的硬件響應特性是儀器掃描時間[5]的根本性決定因素,RBW越小或者掃頻寬度SPAN越寬,其掃描時間越長,則頻譜數據產生速度就越慢。掃描時間ST(Sweep Time)的經驗參考關系式如下:

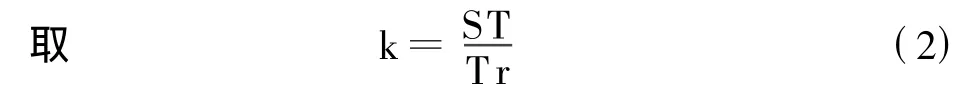

其中,k為濾波器系數。頻譜儀在不同的硬件條件下,k的取值也是不同的。

頻譜儀在實際測量中,其前端各硬件模塊需要實現它本身的功能,即在特定的掃描時間ST內產生滿足用戶要求測量精度的有效掃頻點數Ns。

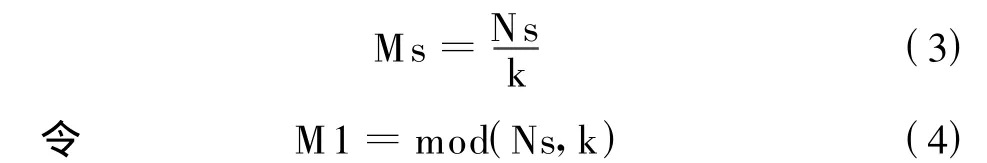

在同等條件下,若頻譜數據點數越多,則其測頻精度會越高,本方案中選擇了全部有效掃頻點數Ns為1000點(1000p)。經處理轉換后頻譜數據在送LCD顯示時,由于數據線帶寬、時鐘頻率和屏幕視頻幀刷新率等的限制,每刷新一次則需要一定的刷新時間Tr。那么,要實現譜線的實時刷新,就需要有對整個Ns的讀取次數k和單次讀取量Ms的算法關系。具體算法如下:

其中,mod表示Ns對k求余函數,以下同。

由式(4)知道,若M1=0,則讀取次數k沿用式(2),單次讀取量Ms沿用式(3)。

若M1不為 0,如果M1<Ms,則:

且最后一次讀取量為M1。

又如果M1≥Ms,則:

且根據式(6)知,最后一次讀取量為M2。

刷新全屏誤差時間計算公式為:

經式(8)分析計算得知,Tr單位為ms級,而 Δk不會超過5,那么總的誤差時間ΔST不會超過0.5 s。在頻譜儀的實際測量中,這完全滿足LCD上的頻譜刷新顯示高保真度的要求精度。經驗證,該算法具有實際應用價值。

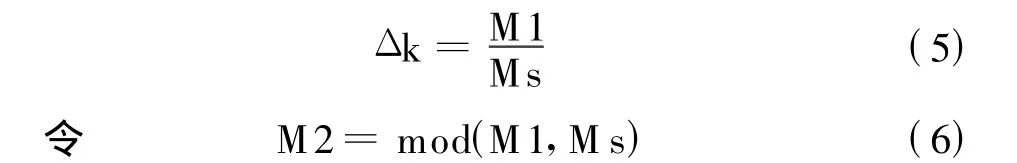

3.3 數據采集、處理與實時顯示的程序實現流程與協調機制

應用層軟件集成開發環境采用EVC4.0,是微軟公司提供的一種專門針對嵌入式設備進行軟件開發的工具[7]。程序開發方法與步驟與常用的VC++6.0類似,而且也自帶了大多數與VC++6.0相同的函數庫,極大地縮短了開發周期。對于用戶監控程序來講,其執行流程與設計框架將決定著儀器性能能否充分發揮、是否符合用戶操作習慣等。本系統監控軟件數據讀取流程如圖4所示。

圖4 數據讀取流程

4 測試結果及誤差分析

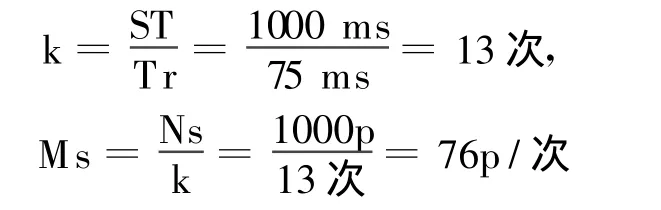

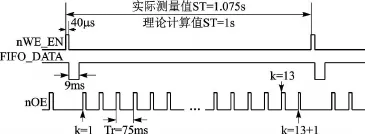

系統人機監控軟件分別進行了2次數據讀取測試,第1次用戶設置掃描時間ST為1 s,則有:

M1=mod(Ns,k)=mod(1000p,13次)=12p,可知M1<Ms,則k=k+1=(13+1)次,那么全頻帶數據讀取次數為14次,且最后一次數據讀取量為M1=12p,顯示過程時間誤差由式(9)得ΔST為Tr,即為0.075 s。總線訪問時序結果如圖5所示。

圖5 總線訪問時序(理論值ST=1 s)

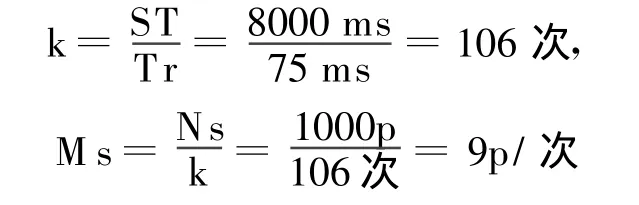

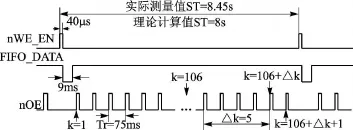

第2次用戶設置掃描時間為8 s,則有:

M1=mod(Ns,k)=mod(1000p,106次)=46p,可知 M1>Ms,則k=k+Δk+1=(106+Δk+1)次,其中次。則k=k+Δk+1=(106+5+1)次,那么全頻帶數據讀取次數為112次,且最后一次數據讀取量由式(6)可知為1p,顯示過程時間誤差由式(9)得 ΔST為(Δk+1)×Tr,即為0.45 s。總線訪問時序結果如圖6所示。

結 語

圖6 總線訪問時序(理論值ST=8 s)

本文設計并實現了一種基于FPGA+ARM的硬件平臺,以及在WinCE操作系統運行環境下對頻譜數據進行實時有序讀取并完成實時刷新顯示的頻譜儀上層交互式軟件控制系統。通過WinCE虛擬映射機制,可以有效實現ARM與外圍設備的無縫連接,完成大量數據的快速傳輸通信。頻譜分析儀在對信號頻率測量中是實時掃描過程,那么人機監控軟件的實時有序讀取數據,保證了譜線在LCD上的高真度顯示。該系統的實現使得頻譜儀具有更好的便攜性和更完善的功能,而且開發周期短,在同領域的開發中有借鑒意義。

[1]羅伯特·A·威特.頻譜和網絡測量[M].北京:科學技術文獻出版社,1997:213-225.

[2]何宗鍵.Windows CE嵌入式系統[M].北京:北京航空航天大學出版社,2006:55-58.

[3]黨曉輝,謝華,戴志堅,等.基于WinCE的I/O控制軟件設計[J].電子測量技術,2009,9(9):100-102.

[4]Richter J.Windows核心編程[M].北京:機械工業出版社,2008:156-170.

[5]劉祖深.頻譜分析儀原理與誤差來源[M].北京:工業器材出版社,1997:45-50.

[6]薛小剛,葛毅敏.Xinlinx ISE 9.X FPGA/CPLD設計指南[M].北京:人民郵電出版社,2007:162-165.

[7]汪兵,李存斌,等.EVC高級編程及其應用開發[M].北京:中國水利水電出版社,2005:67-69.

[8]張冬泉,譚南林,王雪梅.Windows CE使用開發技術[M].北京:電子工業出版社,2006:18-21.