GPS 信號中斷時慣導(dǎo)芯片的位置信息感知系統(tǒng)設(shè)計

武震,宋茂忠

(南京航空航天大學 電子信息工程學院,南京 210016)

武震(碩士研究生),主要研究方向為數(shù)字通信;宋茂忠(教授),主要研究方向為調(diào)制技術(shù)、通信跟蹤系統(tǒng)、衛(wèi)星導(dǎo)航、無線定位。

引 言

當今社會,GPS衛(wèi)星定位系統(tǒng)早已廣泛應(yīng)用于人們的社會生活中,如交通工具導(dǎo)航、個人定位服務(wù)等。但在某些情況下,由于物體遮蔽、散射等原因,我們無法實時接收到GPS衛(wèi)星信號(比如列車進入隧道)。所以有必要研究在GPS信息缺失的情況下,如何通過一定的算法產(chǎn)生模擬GPS信息,從而實現(xiàn)全天候的無縫位置感知。這在某些對位置信息敏感的場合中就顯得非常急迫和重要。

1 慣導(dǎo)芯片簡介

ADIS16003是ADI公司的一款低成本、低功耗,具有SPI接口的雙軸加速度計,屬 MEMS傳感器件[1]。它可以測量動態(tài)和靜態(tài)加速度并以數(shù)字量輸出,測量范圍最小可以達到±1.7g,同時還集成了溫度傳感器,可用于慣性導(dǎo)航、振動檢測和穩(wěn)定性測試等場合中。

SPI是串行外圍設(shè)備接口,是Motorola公司首先在其MC68HCXX系列處理器上定義的。目前已廣泛應(yīng)用在EEPROM、Flash、實時時鐘、A/D轉(zhuǎn)換器以及數(shù)字信號處理器和數(shù)字信號解碼器之間,是一種高速的全雙工同步通信總線。SPI通信只需要4根線,分別為SDI(數(shù)據(jù)輸入)、SDO(數(shù)據(jù)輸出)、SCK(時鐘)和CS(片選)。通信是通過數(shù)據(jù)交換的方式完成的。SPI接口使用串行通信協(xié)議,由SCK提供時鐘脈沖,SDI、SDO則基于此脈沖完成數(shù)據(jù)傳輸。數(shù)據(jù)輸出通過SDO線,數(shù)據(jù)在時鐘上升沿或下降沿時改變,在緊接著的下降沿或上升沿被讀取,完成一位數(shù)據(jù)傳輸。數(shù)據(jù)輸入也使用同樣的原理。

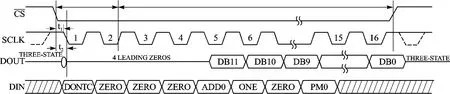

ADIS16003的SPI接口通信時序及控制寄存器配置如 圖1、圖2所示。其中,常用控制字為00000100和00001100,分別表示以正常模式采集X軸和Y軸雙軸軸向加速度。

2 系統(tǒng)工作原理及主要控制信號說明

本文研究了如何在移動端GPS信息缺失的情況下,使用SPI協(xié)議建立FPGA與慣導(dǎo)芯片ADIS16003之間的通信,從而獲取移動物體當前的加速度。DSP將通過EMIF接口讀取此加速度,并根據(jù)之前有效的GPS信息推算出當前的概略GPS信息(經(jīng)緯度、速度和時間等)。

圖1 ADIS16003SPI接口通信時序

圖2 芯片控制寄存器配置

2.1 工作原理

FPGA驅(qū)動ADIS16003慣導(dǎo)芯片工作包括初始啟動和正常啟動兩種模式。

(1)初始啟動模式

FPGA上電復(fù)位時自啟動ADIS16003芯片,配置ADIS16003控制寄存器,并讀取芯片測得的雙軸軸向加速度初始值,存儲到EMIF接口的0x068~0x069地址空間供DSP讀取,用作誤差校正之用(此模式工作在移動端處于靜止狀態(tài)時,且此模式僅由DSP讀取1次)。

(2)正常啟動模式

初始啟動模式完成之后,F(xiàn)PGA將自動轉(zhuǎn)入數(shù)據(jù)采集階段,源源不斷地通過SPI接口從ADIS16003芯片中采集雙軸軸向瞬時加速度,以備DSP使用[2-3]。加速度每秒采集8次,每隔0.125s采集一次。每秒都將得到8組結(jié)果,分 別 為 ax0ay0、ax1ay1、ay2ay2、ax3ay3、ax4ay4、ax5ay5、ax6ay6和ax7ay7,存儲于FGPA內(nèi)部的8個中間寄存器單元reg0~reg7(非EMIF接口,每個輸出結(jié)果為12×2位,存儲于32位的寄存器組中),并隨著時間的推移不斷地刷新。這么做的目的是確保這8個寄存器組中始終保存有最近1s的移動物體加速度信息,以保證加速度信息的準確性和有效性。當CPU通過GPS接收天線檢測到GPS信息丟失時,CPU通過PCI接口給FPGA配入spi_cmd_val信號(高電平有效),同時通過HPI接口給DSP寫入信息丟失前2s的GPS信息(包括經(jīng)緯度、速度和時間),作為定位基點。FPGA檢測到spi_cmd_val信號有效后,立即將中間寄存器單元reg0~reg7中存儲的瞬時加速度送入EMIF接口的0x060~0x067地址單元(32位),同時拉高int_spi_done信號,產(chǎn)生外部中斷INT0(拉低DSP的INT0引腳)通知DSP從EMIF接口讀取加速度信息,并通過后續(xù)軟件算法進行信號處理,轉(zhuǎn)化為移動端經(jīng)緯度信息。再通過DSP的HPI接口上報給CPU,從而使高層獲取移動端當前GPS信息,即完成了GPS位置信息的模擬。加速度存儲格式如表1所列。其中包括初始和瞬時加速度值,共占用32位EMIF接口10個地址單元。

表1 加速度存儲格式

2.2 主要控制信號說明

①spi_cmd_data:ADIS16003芯片控制字(寄存器),8位,F(xiàn)PGA配入。

②spi_cmd_val:GPS信號缺失時 ADIS16003啟動信號,CPU發(fā)出,脈沖觸發(fā)。

③spi_cmd_val_reg:ADIS16003啟動信號寄存器,及時存儲觸發(fā)脈沖,持續(xù)一個時鐘后清0。

④spi_data_i:ADIS16003串行輸出信號,包括雙軸軸向加速度,每個spi_clk時鐘下降沿輸出一位,16個時鐘周期完成一次運算。

⑤spi_cs:SPI片選信號,低電平有效。

⑥spi_clk:SPI通信時鐘信號,由主時鐘分頻得到,此處進行32分頻。

⑦spi_data_o:ADIS16003控制字輸入信號,8位串行輸出,spi_clk時鐘上升沿動作。

⑧spi_rdata:ADIS16003運算結(jié)果,12位,每個spi_clk下降沿輸出一位,采取移位拼接方式(向左移),在第16個時鐘下降沿輸出一次完整的采集結(jié)果(每次采集至少需要16個時鐘周期)。

⑨spi_state:SPI工作狀態(tài)信號,0為IDLE,1為BUSY,2為DONE,采用有限狀態(tài)機進行設(shè)計。

⑩spi_wr_cnt_o、spi_wr_cnt_i:十六進制計數(shù)器,時鐘上升沿和下降沿分別計數(shù)[4]。

整個系統(tǒng)工作流程如圖3所示。

圖3 系統(tǒng)工作流程

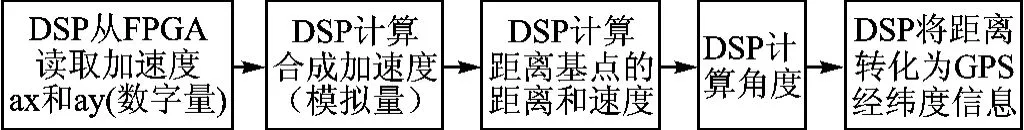

2.3 DSP后續(xù)軟件處理流程

DSP后續(xù)軟件處理流程如圖4所示。DSP在CCS 3.3軟件環(huán)境下計算完成。此處的基點(basepoint)是指最接近GPS信號消失前的具有有效GPS信息的移動物體位置,即GPS消失前2s的移動端GPS信息(每秒測量1次)。角度計算是指DSP將距離信息轉(zhuǎn)換為GPS經(jīng)緯度信息。

圖4 DSP后續(xù)軟件處理流程

3 程序?qū)崿F(xiàn)及功能仿真

3.1 芯片資源

本系統(tǒng)采用的FPGA芯片為Cyclone III系列的EP3C120F80C7器件,DSP芯片為 TMS320VC5510[5],慣導(dǎo)芯片采用ADIS16003。各芯片接口和主要信號流向示意圖如圖5所示,包括PCI、SPI、EMIF和 HPI等主要外設(shè)接口。

圖5 各芯片接口和主要信號流向示意圖

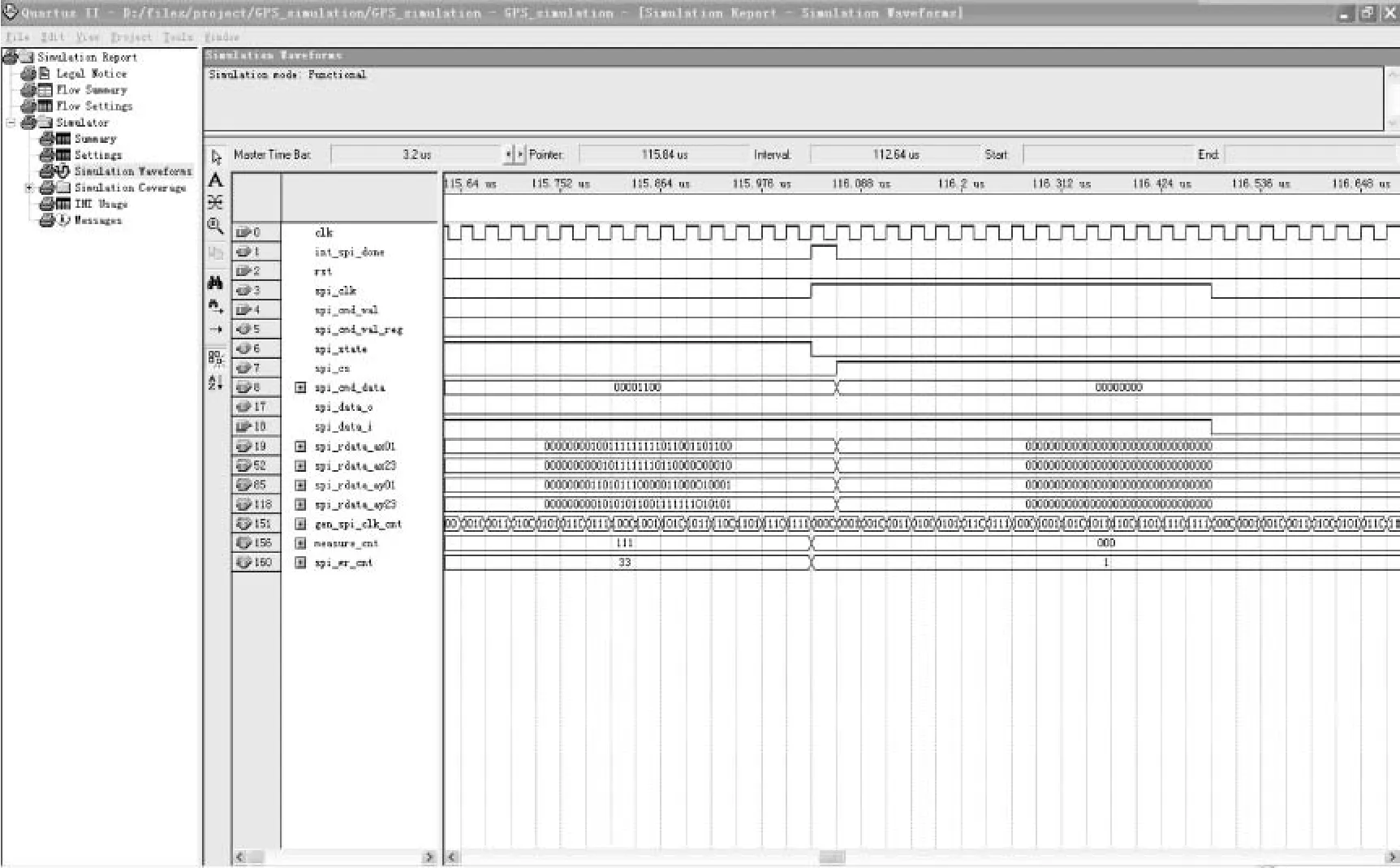

3.2 軟件功能仿真

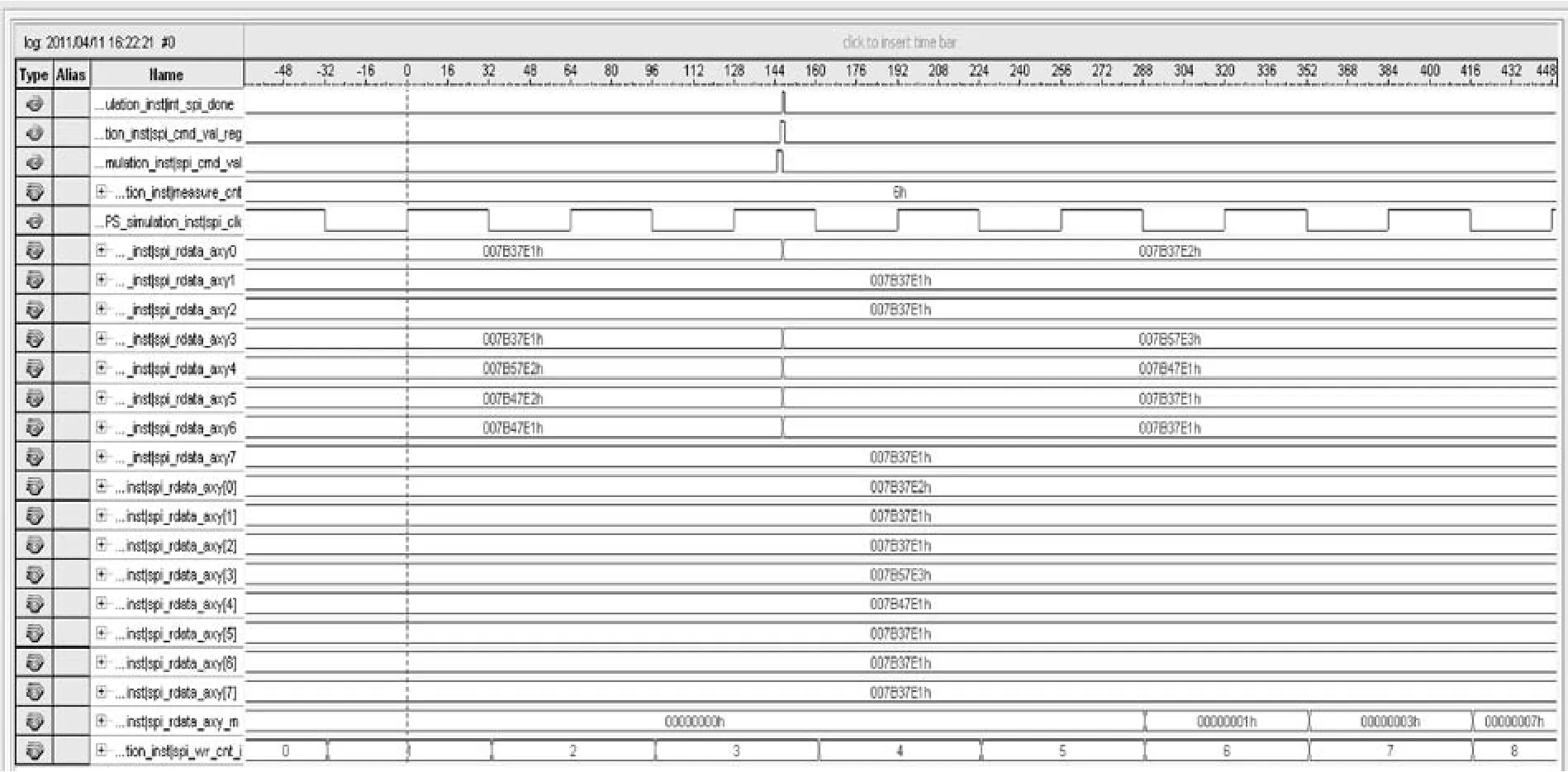

本系統(tǒng)的底層SPI通信部分使用FPGA進行驅(qū)動,采用Verilog HDL語言編寫程序,并在Quartus 10.1集成環(huán)境下進行功能仿真驗證[6-7],如圖6所示。結(jié)果顯示,數(shù)據(jù)采集符合設(shè)計邏輯,當所有數(shù)據(jù)采集完成一次之后立即送出中斷信號觸發(fā)DSP讀取。

4 測試結(jié)果

圖6 Quartus 10.1仿真結(jié)果

圖7 SignalTap加速度在線采集實測波形

利用SignalTap II Logic Analyzer在線邏輯分析儀進行板上硬件實際調(diào)試,圖7為SignalTap加速度在線采集實測波形。測試結(jié)果顯示數(shù)據(jù)采集和處理符合芯片時序要求;FPGA與DSP的EMIF接口配合良好,經(jīng)過后續(xù)DSP軟件算法處理后能成功推算出移動物體當前的GPS信息,及時上報CPU(每秒1s)。其中SPI總線通信時鐘為1.4MHz。經(jīng)過測試,系統(tǒng)完全能夠達到設(shè)計要求,已在某大型通信系統(tǒng)中得到應(yīng)用。

結(jié) 語

通過本系統(tǒng)的設(shè)計和調(diào)試過程可以看出,使用FPGA作為物理層驅(qū)動具有SPI接口的數(shù)字芯片是簡單而有效的一種數(shù)字設(shè)計方案,可以較容易地滿足芯片的時序要求。通過與EMIF接口的配合還可以很好地利用DSP芯片完成眾多嵌入式系統(tǒng)的設(shè)計。

[1]Analog Device.ADIS16003Datasheet,2005.

[2]孫彪.基于ADIS16355MEMS芯片的慣性測量組件系統(tǒng)設(shè)計[J].電子設(shè)計工程,2010(1):89-90.

[3]湯霞清,晏昌平,劉培.MEMS傳感器ADIS16350接口轉(zhuǎn)換的設(shè)計與實現(xiàn)[J].現(xiàn)代電子技術(shù),2010(18):145-147.

[4]孫世國,陳帥,陳倩,等.基于FPGA的SPI 4.2接口設(shè)計[J].微計算機信息,2009,25(2):189-190.

[5]Texas Instruments.TMS320VC5510/5510A 產(chǎn)品數(shù)據(jù)手冊[OL].[2011-05].http://www.ti.com.

[6]祁曉磊,蔡學良,孫德瑋.用Verilog HDL進行FPGA設(shè)計的原則與方法[J].電子測試,2008(3):67-71.

[7]王金明.數(shù)字系統(tǒng)設(shè)計與Verilog HDL[M].3版.北京:電子工業(yè)出版社,2010.