對全速測試中時序例外路徑的處理方法的改進

韓少鋒,管成程

(1 羿發科技深圳有限公司北京分公司,北京 100080;2 青島港灣職業技術學院 電氣工程系,青島 266404)

0 引言

ATPG (Automatic Test Pattern Generation )是指由EDA工具基于可掃描的測試結構自動生成測試向量的結構化測試方法。由于時鐘速度的提高和工藝尺寸的減小會給芯片帶來相關的缺陷,因此全速測試對于現代芯片設計必不可少。目前,高級的ATPG工具都支持基于掃描的全速測試技術,許多資料也都給出了生成全速測試向量的基本流程。本文則主要探討在生成全速測試向量時,如何處理錯誤路徑和多周期路徑。因為如果這些時序例外沒有被正確處理的話,可能會導致良好的芯片無法通過全速測試,進而造成良率的降低。

1 術語解釋

在今天的電路設計流程中,STA主要用來確保電路里沒有時序上的錯誤。其中,STA工程師會經常使用“錯誤路徑”這個術語,它是指某一條路徑雖然在芯片中客觀存在,但是STA工具不去對它做時序上的檢查,也就是說在芯片正常工作過程中,這條路徑上不會有單周期時鐘數據的傳遞。然而,在輸入全速測試向量時,會把非功能性的狀態值引入電路,從而使這些路徑在基于掃描的全速測試中被敏化。

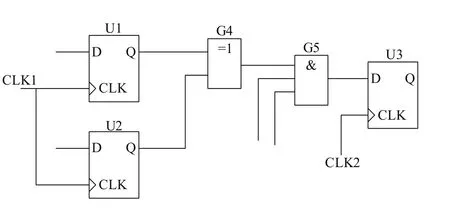

在運行時序分析之前,STA工程師會把所設計的電路裝載到STA工具里,指定時鐘和時序約束,然后加入時序例外信息。這些時序例外信息被用來覆蓋默認的單周期時鐘約束,可以被應用到任意時序路徑上。常用的STA工具是來自Synopsys公司的PrimeTime,指定錯誤路徑的命令是set_false_path,它有許多參數,比如-from, -to,-through等等,-from定義了錯誤路徑的起點,可以是輸入端口或寄存器時鐘接腳;-through定義了路徑的途徑點,可以是單元、接腳或端口;路徑的終點由-to定義,可以是寄存器的數據接腳或輸出端口。自由組合這些參數就可以指定芯片中的任意一條路徑。比如圖1是實際電路中的一部分,可以用set_false_path做如下設定:

set_false_path –from CLK1 –to CLK2

set_false_path –from CLK1 –to U3/D

set_false_path –through G5/out

如果通過某一根接腳、某一個單元,或者某一個端口的全部路徑都是錯誤路徑,那么使用set_disable_timing命令比set_false_path命令效率更高。

通過指定錯誤路徑,STA工具就不會對這些路徑進行時序方面的評估,從而使電路在邏輯仿真和物理上的布局布線中滿足時序收斂的要求。

圖1 錯誤路徑的邏輯電路圖

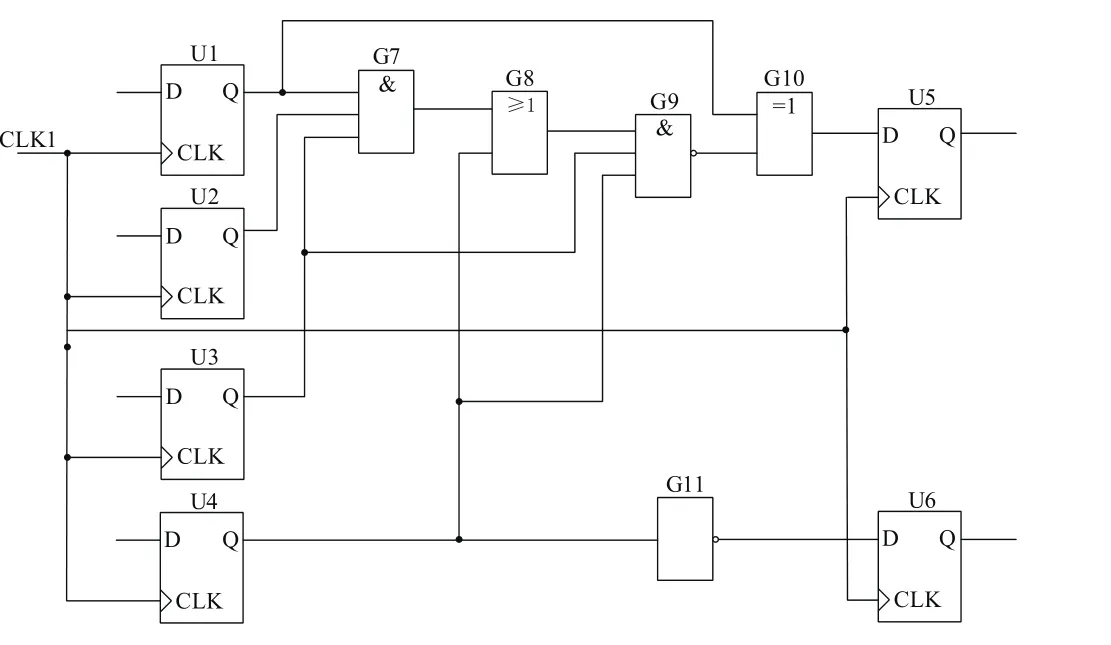

多周期路徑是指數據穿過一條路徑的全部時間延遲大于一個時鐘周期,在STA工具中指定多周期路徑的方式和參數類似于指定錯誤路徑,所用到的命令是set_multicycle_path。如圖2所示,從U1到U5的延遲要大于一個時鐘周期,所以可以使用下面的命令來表示:

set_multicycle_path –from U1 –to U5

圖2 多周期路徑的邏輯電路圖

STA過程結束之后,可以使用write_sdc命令,把所有的時序例外信息都寫成SDC(Synopsys Design Constraints)格式的文件,供其他工具使用。

2 處理時序例外的傳統方法

在ATPG中處理時序例外路徑的傳統方法依賴于加入約束或者使用向量屏蔽功能。通常的做法是分析路徑,加入合適的單元約束,比如給錯誤路徑或者多周期路徑的起點單元或者(和)終點單元強制賦予X值。

這種方法在某些情況下可以起作用,但是它也有一些缺點。首先,確定正確的單元位置是個手工過程,任務繁重。其次,這種方法過于保守,所以測試結果和產品質量會受到影響。當一個X約束被加到捕捉單元時,所有這條路徑上的原本能夠觀察到的錯誤現在都變得不可觀了。這個缺點還導致了第三個潛在的問題,當設計變大,測試向量的數量增加時,許多公司都會使用測試壓縮技術。此時,過多的X約束值會影響測試壓縮技術的使用,給測試結果帶來非常嚴重的負面影響。

最后,對于那些復雜的時序例外路徑,產生完整的約束和屏蔽值是非常困難的,也是容易出錯的。這些都會導致測試向量在自動測試設備(ATE)上無法通過。

3 處理時序例外的新方法

為了克服傳統方法的保守性和其他缺點,一種在全速測試向量生成過程中處理錯誤路徑和多周期路徑的新方法被提出來。這種方法不需要繁瑣的手工過程去產生單元約束和向量屏蔽,而且所生成的全速測試向量也不會在ATE上不能通過。這種自動化的方法由下列幾個步驟組成。

3.1 輸入時序例外路徑

ATPG工具讀入包含有時序例外路徑信息的SDC文件,在這個文件中,錯誤路徑由set_false_path命令和set_disable_timing命令指定,多周期路徑由set_multicycle_path命令定義。除此之外,ATPG工具還能自動處理如下的命令:set_case_analysis, creat_generated_clock,creat_clock 和 set_hierarchy_separator等。

如果沒有SDC文件的話,還可以使用ATPG工具自帶的命令來指定時序例外路徑信息,它們是add false path和add multicycle path。

3.2 標記相關路徑

在讀入時序例外信息之后,這些路徑會在電路中被標記出來,并且在生成全速向量的過程中被使用到。注意電路中的某個節點作為前面路徑的終點的同時,也可以作為后面路徑的起點。

3.3 檢查路徑敏化

檢查一條時序例外路徑的起點的初始邏輯值。如果在這個起點處發現有一個全速電平轉換,那么這個起點的初值就被儲存起來,同時加入一個X值(X代表未知的邏輯值)。通過事件驅動邏輯仿真,加入的X值就沿著完整的時序例外路徑向前傳播。在此仿真進行過程中,X值傳播所經過的門電路的初始值都要被保存。在仿真結束的時候,檢查時序例外路徑的終點,把帶有X值的終點的位置信息保存到一個叫做X屏蔽表的數據結構中。如果全部終點都有X值,那么這條時序例外路徑叫做完全敏化;如果部分終點有X值,叫做部分敏化;如果所有終點都沒有X值,叫做不敏化。敏化檢查結束后,電路的原始狀態就被儲存起來。

3.4 確定未知狀態

在生成每一個全速測試向量的過程中,都要考慮時序例外路徑的影響。每一個給定的全速測試向量里都包含多個時間幀,由于時序例外路徑的敏化造成的未知狀態對于每個時間幀而言都需要被確定。如步驟3.3所述,對時序例外路徑做敏化檢查,對每個時間幀都生成X屏蔽表。在這個屏蔽表被生成之后,原始的電路狀態就被保存下來。X值被加到屏蔽表里所列到的電路節點,通過邏輯仿真,這些未知的狀態產生的結果就會被向前傳播。

3.5 維持過去的電平轉換結果

在一個給定的全速測試向量中,對每一個時間幀都要考慮在時序例外路徑的輸入端維持以往的電平轉換結果。假設當前的時間幀是t,有一條錯誤路徑P1,在它的輸入端有一個全速的電平轉換發生在小于t的時間幀里。那么即使當前(也就是在時間幀t)在P1的輸入端沒有全速電平轉換發生,也要對這條路徑做敏化檢查。因為沿著這條錯誤路徑的時間延遲是未知的。如果這條錯誤路徑P1的敏化條件得到了滿足,則受到影響的端點就會在當前的時間幀里被賦予未知的邏輯值,同時,通過傳統的邏輯仿真,這些未知值向前傳播。而清除以前的電平轉換的影響可以通過如下慢速事件:1)掃描鏈的串行輸入;2)掃描鏈的串行輸出;3)其他慢速時鐘事件。

對于傳播延遲是d的多周期路徑而言,假設當前的時間幀是t,則對于小于t,大于t-d的時間幀內發生的全速電平轉換,都要考慮做敏化檢查。對于敏化檢查之后的多周期路徑的處理方式與對錯誤路徑的處理方式相同。

4 一個具體的例子

這種有效的處理錯誤路徑和多周期路徑的新方法被廣泛應用到不同尺寸和類型的設計中,并取得了較好的結果。下面就是我們實際項目中的一個例子。

這個項目是AT6600D0芯片,它具有以下特點:1)支持AC掃描模式,支持電平轉換延遲掃描向量測試;2)AC掃描時鐘由內部PLL產生,通過JTAG接口配置成broadside形式的時鐘波形;3)33個內部時鐘域;4)最大時鐘速度624MHz;5)總共有950K個門單元;6)一共有68條掃描鏈,共計468K掃描單元;7)目標錯誤有1.4M;8)定義了86條錯誤路徑和多周期路徑,利用通配符,可以覆蓋的路徑大概有10k條。

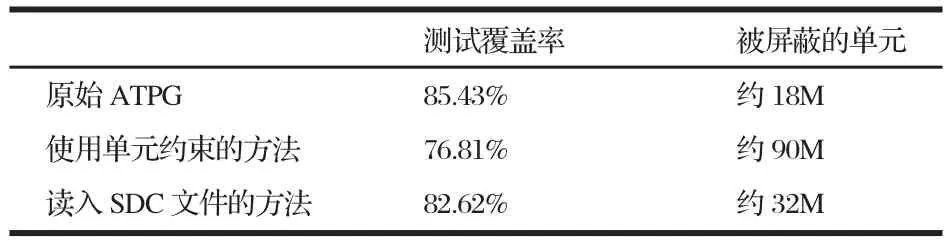

首先,運行全速ATPG一次,不加任何單元約束或者時序例外的定義。這個結果要保存成二進制形式的向量,以便做進一步的錯誤仿真(fault simulation)。本次向量集的測試覆蓋率是85.43%,同時總共有18M的屏蔽值。但是需要注意的是這個覆蓋率是無意義的,因為這些向量集沒有考慮設計中的時序例外,所以無法將它們應用到ATE上去。

為了處理已知的錯誤路徑和多周期路徑,首先像第三節描述的那樣,把必要的單元約束加上,然后做錯誤仿真,表1給出了這一流程的結果,可見,使用這種方法后測試覆蓋率降低了8.6%,被屏蔽的單元增加了5倍。

接下來,重新做錯誤仿真的流程,從讀入二進制向量集開始,這一次,使用ATPG工具的讀入SDC文件的功能來直接獲取時序例外定義,因此可以使用帶有時序例外的完整的路徑信息。本次流程的結果也列在表1里。

比較兩個流程的結果,很明顯,使用SDC文件提供的時序例外大大改善了所生成向量的測試質量。與舊的純粹加單元約束的方法相比最后的向量集減少了58M的屏蔽值,但是卻增加了5.8%的覆蓋率。

表1

5 結論

對于確保今天的納米級設計的測試質量,基于掃描的全速ATPG測試向量已經變得非常重要。為了得到盡可能好的全速測試向量,需要加入電路中時序例外路徑的影響。在設計的過程中,通常是用靜態時序分析找到并且指定這些路徑的。

過去,人們創建ATPG掃描向量時,受限于處理這些例外路徑的不成熟的方法,比如在生成測試向量的時候加入單元約束來屏蔽掉例外路徑的起點和終點。這種解決方法的處理方式過于保守,會導致很差的測試質量。

本文解釋了在生成全速測試掃描向量時,處理時序例外路徑的更好的方法,還提供了一個詳細的業界設計的例子。通過將SDC文件應用到電路設計中,ATPG工具能夠自動分析路徑和向量,并且只屏蔽必需的捕捉位置。這種方法更容易使用,更準確,提供了更好的測試質量。這種使用SDC文件的新方法為芯片的設計和測試之間架起了一座溝通的橋梁。

[1]Synopsys.TetraMAX ATPG User Guide[M].Synopsys ,2010.

[2]Michael L.Bushnell, Vishwani D.Agrawal .Essentials of electronic testing for digital, memory and mixedsignal VLSI circuits[M].KLUWER ACADEMIC PUBLISHERS,2002.

[3]M.Beck, O.Barondeau, F.Poehl, X.Lin, R.Press.Measures to improve Delay Fault Testing on Low-Cost Testers – A case Study[J].Proc.IEEE VLSI Test Symposium, May 2005:223-228.

[4]胡晉.基于掃描的SoC全速測試及應用[J].現代電子技術,2007(08):192-194.

[5]馬琪,焦鵬,周宇亮.基于掃描的VLSI全速測試方法[J].半導體技術,2007,32(12):1090-1093.

[6]蔡志匡,黃凱,黃丹丹,時龍興.Garfield系列SoC芯片可測性設計與測試[J].微電子學,2009,39(05):591-596.

[7]于明.CPLD測試方法研究[J].電子測試,2010(01):38-43.

[8]王巍.高速芯片設計中的全速度(At-Speed)測試[J].集成電路應用,2002(01).