基于FPGA的UART設計

謝謝

(陜西烽火電子股份有限公司 陜西 寶雞721006)

通 用 異 步 收 發 器 (Universal Asynchronous Receiver/Transmitter,UART)可以和各種標準串行接口,如RS232和RS485等進行全雙工異步通信,具有傳輸距離遠、成本低、可靠性高等優點。一般UART由專用芯片來實現,但專用芯片引腳都較多,內含許多輔助功能,在實際使用時往往只需要用到UART的基本功能,使用專用芯片會造成資源浪費和成本提高。當我們不需要用到完整的的UART功能和一些輔助功能時,就可以將需要的UART功能集成用FPGA來實現,然而,FPGA內部并不擁有CPU控制單元,無法處理由UART控制器產生的中斷,所以FPGA不能利用現成的UART控制器構成異步串行接口,必須將UART控制器的功能集成到FPGA內部。從而可以大大的減少了體積、簡化了電路,也提高了系統的靈活性。

1 UART的工作原理

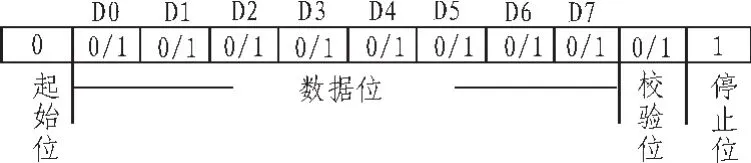

UART是一種串行數據總線,用于異步通信,并且雙向通信,可實現全雙工發送和接收。基本的UART只需要兩條信號線(TXD、RXD)和一條地線就可以完成數據的互相通信,接收和發送互不干擾,這樣就大大節省了傳輸費用。由于UART是異步通信,所以需要對數據進行同步。UART發送/接收數據的傳輸格式如圖1所示,一個字符單位由開始位、數據位、校驗位、停止位組成(其中校驗位可供選)。

圖1 異步串口傳輸格式Fig.1 Asynchronous serial transmission format

發送或接收一個完整的字節信息,首先是一個作為起始位的邏輯“0”位,接著是8個數據位,然后是停止位邏輯“1”位,數據線空閑時為高或“1”狀態。在字符的8位數據部分,先發送數據的最低位,最后發送最高位。每位持續時間是固定的,由發送器本地時鐘控制,每秒發送的數據位個數,即為“波特率”。起始位和停止位起著很重要的作用。顯然,它們標志每個字符的開始和結束,但更重要的是他們使接收器能把他的局部時鐘與每個新開始接收的字符再同步。異步通信沒有可參照的時鐘信號,發送器隨時都可能發送數據,任何時刻串行數據到來時,接收器必須準確地發現起始位下降沿的出現時間,從而正確地采樣緊接著的10或者11位(包括開始位、數據位和停止位),接收器的時鐘和發送器的時鐘不是同一個,因此,接收器所確定的采樣點的間隔和發送器所確定的位間隔時間不同,這點要特別注意。

2 UART功能設計

異步通信的一幀傳輸經歷以下步驟:1)空閑狀態。發送方連續發送信號,處于信息“1”狀態。2)開始傳輸。發送方在任何時刻將傳號變成空號,即“1”跳變到“0”,并持續 1位時間表明發送方開始傳輸數據。而同時,接收方收到空號后,開始與發送方同步,并期望收到隨后的數據。3)奇偶傳輸。數據傳輸之后是可供選擇的奇偶位發送或接收。4)停止傳輸。最后是發送或接收的停止位,其狀態恒為“1”。

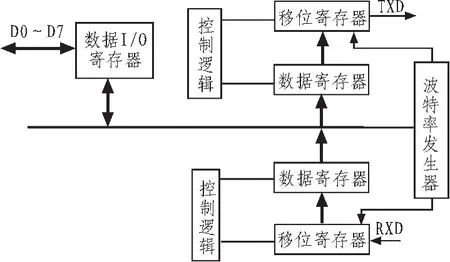

設計的基本原則是保留最主要的功能,基于FPGA的UART系統由波特率時鐘發生器、接收器和發送器3個子模塊組成,如圖2所示。

圖2 UART功能框圖Fig.2 UART functional block diagram

2.1 波特率發生器設計

波特率發生器實質是設計一個分頻器,用于產生和RS232通信同步的時鐘。在系統中用一個計數器來完成這個功能,分頻系數N決定了波特率的數值。該計數器一般工作在一個頻率較高的系統時鐘下,當計數到N/2時將輸出置為高電平,再計數到N/2的數值后將輸出置為低電平,如此反復即可得到占空比50%的波特率時鐘,具體的波特率依賴于所使用的系統時鐘頻率和N的大小。如系統時鐘頻率是6.4 MHz,要求波特率是9 600,則16倍波特率時鐘的周期約等于42個系統時鐘周期,則計數器取42/2=21時,當計數溢出時輸出電平取反就可以得到16倍約定波特率的時鐘。

使用VHDL來描述波特率發生器的完整代碼如下:Process(rst,clk6_4M)

if rst=‘0’then --0復位

count<=0;

bclkr<= ‘0’;

elsif rising_edge(clk6_4M) then

if(count=20)

count<=0;

bclkr<=not bclkr; ‘--生成16倍于波特率的clock,6.4 MHz晶振。

else

count<=count+1;

end if;

end if;

end process;

2.2 發送器設計

UART發送器的設計較容易,只要每隔一個發送周期按照數據幀格式及要求的速率輸出數據即可。沒有數據要發送時,發送數據寄存器為空,發送器處于空閑狀態;當檢測到發送數據寄存器滿信號后,發送器及發送起始位,同時8個數據位被并行裝入發送移位寄存器,停止位緊接著數據位指示一幀數據結束。只有發送數據寄存器為空時,RAM中的待發數據才能被裝入。程序中使用計數器要保證各位周期定時正確。

2.3 接收器設計

接收器的工作過程如下,串行數據幀和接收時鐘是異步的,發送來的數據由邏輯1變為邏輯0可以視為一個數據幀的開始。接收器先要捕捉起始位,然而,通信線上的噪音也極有可能使傳號“1”跳變到空號“0”。所以接收器以16倍的波特率對這種跳變進行檢測,確定rxd輸入由1到0,邏輯0要8個bclkr(16倍的波特率時鐘)周期,才是正常的起始位,而不是噪音引起的,其中若有一次采樣得到的為高電平則認為起始信號無效,返回初始狀態重新等待起始信號的到來。

采到正確的起始位后,就開始接收數據,最可靠的接收應該是接收時鐘的出現時刻正好對著數據位的中央。由于在起始位檢測時,已使時鐘對準了位中央,用16倍波特率的時鐘作為接收時鐘,就是為了確保在位寬的中心時間對接收的位序列進行可靠采樣,當采樣計數器計數結束后所有數據位都已經輸入完成。最后對停止位的高電平進行檢測,若正確檢測到高電平,說明本幀的各位正確接收完畢,否則出錯。最后將正確的數據轉存到數據寄存器中,輸出數據。還要輸出一個數據接收標志信號標志數據接收完。

利用有限狀態機實現,完整代碼如下:

process(bclkr,reset,rxd_sync)

variable count :std_logic_vector(3 downto 0); --定義中間變量

variable rcnt :integer:=0;

variable rbufs :std_logic_vector(7 downto 0);

begin

if reset='0'then --0復位

state<=r_start;

count:="0000";

elsif rising_edge(bclkr) then

case state is

when r_start=> --狀態1,等待起始位

if rxd_sync='0'then

state<=r_center; --檢測到起始位,進入下一個狀態(r_center狀態)

r_ready<=‘0’;

rcnt:=0;

else

state<=r_start; --沒 檢 測 到 起 始位,仍處于r_start狀態

r_ready<=‘0’;

end if;

when r_center=> --狀態2,求出每位的中點

if rxd_sync='0'then

if count>="0100"then--保持邏輯0超過1/4個位時間的信號一定是起始位

state<=r_wait;

count:="0000";

else

count:=count+1;

state<=r_center;

end if;

else

state<=r_start;

end if;

when r_wait=> --狀態3,等待狀態

if count>=“1110”then --等待 15個 clkb周期

count:=“0000”;

if rcnt=framlenr then--已經采集8 bit數據

state<=r_stop;

else

state<=r_sample;

end if;

else--等待,一直等到15個bclkr周期

count:=count+1;

state<=r_wait;

end if;

when r_sample=>

rbufs (rcnt):=rxd_sync; --數據時低位在前,高位在后,先轉換低位數據

rcnt:=rcnt+1;

state<=r_wait; --狀態 4,數據位采樣檢測,檢測是否已經收到8 bit數據

when r_stop=> --并沒有處理停止位。所以輸出數據不加停止位

r_ready<=‘1;; --輸出幀接收完畢信號

rbuf<=rbufs;

state<=r_start; --狀態4,輸出幀接收完畢信號

when others=>

state<=r_start;

end case;

end if;

end process;

3 仿 真

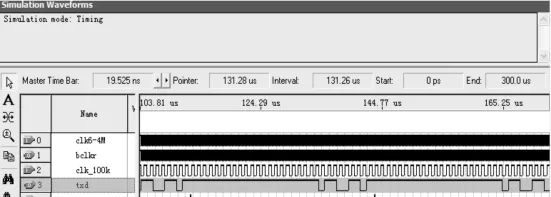

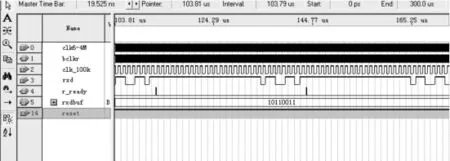

本設計在Altera Cyclone系列的EPlC3T100I7芯片上進行了驗證,對發送模塊和接收模塊的仿真結果分別如圖3、圖4所示。發送的數據能嚴格按照串行通信協議進行傳輸;接收的數據也完全正確。仿真無誤后,使用QuarltusⅡ軟件將編譯好的.pof格式文件載到配置芯片EPCS1中。結果通信數據完全正確,電路工作穩定、可靠。

用FPGA設計UART,可以用片上很少的邏輯單元實現UART的基本功能。與傳統設計相比,能有效減少系統的PCB面積,降低系統的功耗,提高設計的穩定性和可靠性,充分利用FPGA的剩余資源。并可方便地進行系統升級和移植。

圖3 發送模塊仿真Fig.3 Receiver simulation

圖4 接收模塊仿真Fig.4 Transmitter simulation

4 結 論

該設計具有很大的靈活性,通過調整波特率發生器的分頻參數,就可以使其工作在不同的頻率。采用16倍波特率的采樣時鐘,可以實時有效監測數據的起始位,并對數據位進行中央采樣,從而保證了所采樣數據的正確性。該模塊可以作為一個完整的IP核,靈活地移植進各種型號FPGA中,在實際應用時也可嵌入到其他系統中,有很好的借鑒和參考價值。

[1]黃智偉.FPGA系統設計與實踐[M].北京:電子工業出版社,2005.

[2]趙鑫,蔣亮.VHDL與數字電路設計[M].北京:機械工業出版社,2005.

[3]姜寧,范多旺.基于FPGA/CPLD的通用異步通信接口UART的設計[J].信息技術與信息化,2006(1):86-88.JIANG Ning,FAN Duo-wang.The design of UART based on FPGA/CPLD[J].Information Technology and Information,2006(1):86-88.

[4]于宏毅,王大鳴,顧雪琳.簡化UART功能的FPGA實現[J].現代電子技術,2004,4(171):64-66.YU Hong-yi,WANG Da-ming,GU Xue-lin.Implementation of UART on FPGA[J].Modern Electronic Technology,2004,4(171):64-66.

[5]聶濤,許世宏.基于FPGA的UART設計[J].現代電子技術,2006,2(217):127-129.NIE Tao,XU Shi-hong.Design of UART Based on FPGA[J].Modern Electronic Technology,2006,2(217):127-129.

[6]何勇.基于FPGA的UART設計與實現[J].現代電子技術,2010(11):95-99.HE Yong.Design and implementation of UART based on FPGA[J].Modern Electronic Technology,2010(11):95-99.