基于實時解調(diào)的AIS信號偵察

侯 聰

(中國西南電子技術(shù)研究所,成都 610036)

1 引 言

船舶自動識別系統(tǒng)(AIS)是由國際海事組織(IMO)、國際助航設(shè)備和航標(biāo)協(xié)會(IALA)以及國際電信聯(lián)盟(ITU-R)共同提出的技術(shù)標(biāo)準(zhǔn),可用于船舶避碰、水上智能交通管理及海域監(jiān)視等領(lǐng)域。對于AIS信號的偵察,有利于掌握一定范圍海域內(nèi)的船舶情況,對于海事態(tài)勢的掌握、海防安全、打擊走私、反海盜等都有重要意義[1]。

本文結(jié)合FPGA,對于AIS信號偵察的數(shù)字信號處理部分,提出了一種較通用的設(shè)計實現(xiàn)方案,主要手段包括對AIS信號的實時解調(diào),得到內(nèi)涵信息;以及在對采樣數(shù)據(jù)和解調(diào)數(shù)據(jù)加上精確時標(biāo)后,完成存儲傳輸,為后續(xù)的各種處理手段提供原始數(shù)據(jù)。

2 系統(tǒng)概述

2.1 系統(tǒng)的組成和工作原理

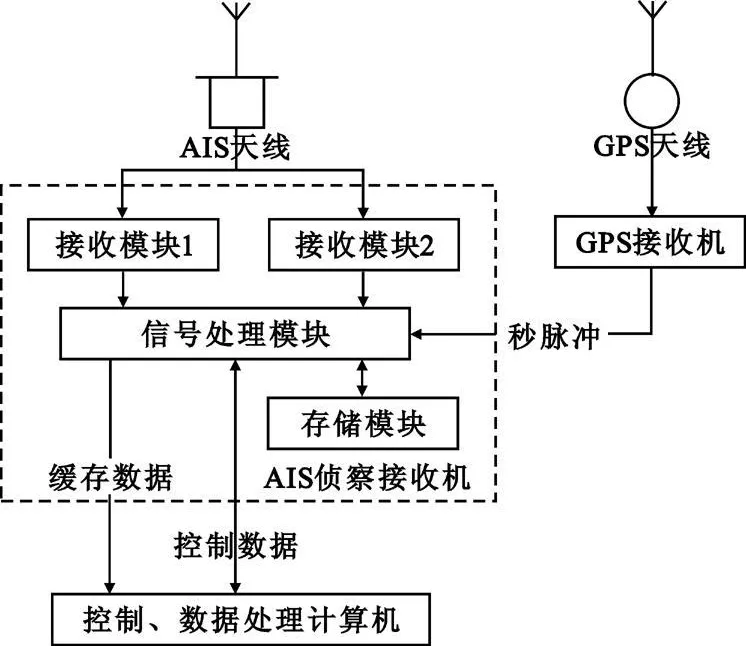

系統(tǒng)組成如圖1所示,主要由AIS接收天線、AIS偵察接收機(jī)、存儲器、GPS天線及GPS接收機(jī),以及后端的計算機(jī)組成。

系統(tǒng)中的兩個接收模塊,目的在于能夠同時完成兩路不同頻點AIS信號的接收;信號處理模塊對中頻信號進(jìn)行帶通采樣、數(shù)字下變頻[2],完成信號的解調(diào),并根據(jù)不同工作模式選擇將處理數(shù)據(jù)實時傳輸或存儲在固態(tài)存儲器中;后端計算機(jī)完成與AIS偵察接收機(jī)的通信控制功能,還可以根據(jù)實際需要,增加顯示、后續(xù)等功能。

圖1 AIS偵察系統(tǒng)的組成Fig.1 Composition of AIS reconnaissance system

2.2 AIS偵察數(shù)字信號處理的主要性能

AIS偵察數(shù)字信號處理部分的主要性能包括:

(1)能實時偵收兩路不同頻點的AIS信號,完成AIS內(nèi)涵信息的解析;解調(diào)方式GMSK 9.6 kbit/s,解調(diào)性能20%PER(誤包率);

(2)具有原始采樣數(shù)據(jù)和解調(diào)數(shù)據(jù)的存儲功能,存儲數(shù)據(jù)通過對外接口輸出;能對AIS解調(diào)結(jié)果和基帶存儲數(shù)據(jù)進(jìn)行時標(biāo)標(biāo)注。

3 AIS偵察信號處理的實現(xiàn)

3.1 AIS信號偵收解調(diào)相關(guān)算法

3.1.1 測頻算法

AIS信號調(diào)制方式為GMSK,載波分量在信號FFT頻譜上不明顯,如采用求頻譜重心的方法測頻則誤差較大,本設(shè)計中采用信號非線性變換再FFT測頻的方法。對輸入信號直接平方,對平方后的信號進(jìn)行FFT,根據(jù)譜峰最大值和次大值處對應(yīng)頻率的均值即信號的頻率。

3.1.2 AIS信號基帶解調(diào)算法

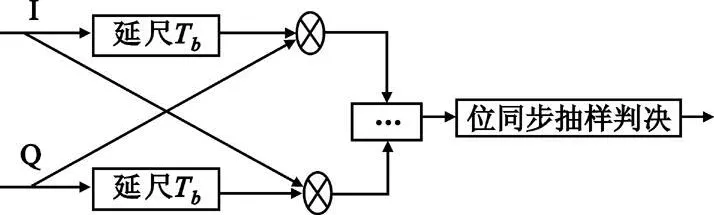

硬件實時解調(diào)采用的是1 bit差分非相干解調(diào)的算法。AIS采樣信號經(jīng)變換成基帶I、Q信號后,根據(jù)1 bit差分檢測算法找出在1 bit周期內(nèi)接收到的信號在相位方面的改變量,對改變量進(jìn)行抽樣判決后即得到AIS信息比特流[3]。

圖2 AIS基帶解調(diào)算法原理Fig.2 Principle of baseband AIS demodulation

3.1.3 匹配序列訓(xùn)練、位同步和信號結(jié)尾搜索

訓(xùn)練序列匹配是利用AIS信號幀頭的特點,將差分鑒頻判決為[-1+1]的序列與標(biāo)準(zhǔn)模板序列進(jìn)行相關(guān),當(dāng)閾值大于門限時認(rèn)為有AIS信號,此時還需要確定同步頭的起始位置,所以在大于閾值之后的一段時間內(nèi)還需要對相關(guān)計算最大值位置進(jìn)行搜索,搜索范圍為從大于閾值開始到隨后計算的若干個數(shù)據(jù)中找到最大值位置,此處即作為有效數(shù)據(jù)的起始位置。

通過訓(xùn)練序列匹配發(fā)現(xiàn)有AIS信號時,根據(jù)訓(xùn)練得到的匹配序列起始時刻、碼片長度和當(dāng)前采樣率,可以計算出每個碼片的最佳采樣時刻,并在最佳采樣時刻時取出AIS信息比特流中的數(shù)據(jù),得到解調(diào)數(shù)據(jù)。

最后,對解調(diào)數(shù)據(jù)進(jìn)行分析,當(dāng)連續(xù)出現(xiàn)7個碼片的“1”或者“0”時,表示發(fā)現(xiàn)AIS信號的結(jié)尾,完成一個完整的AIS信號解調(diào),單次解調(diào)結(jié)束。

3.2 硬件設(shè)計和實現(xiàn)結(jié)構(gòu)

信號處理模塊的硬件設(shè)計是以AD+FPGA+DSP為基礎(chǔ)構(gòu)建的平臺,基于多平臺應(yīng)用、低成本等因素,FPGA選擇Xilinx公司的Virtex2-3000系列芯片,DSP選擇TI公司的TMS320VC33系列。

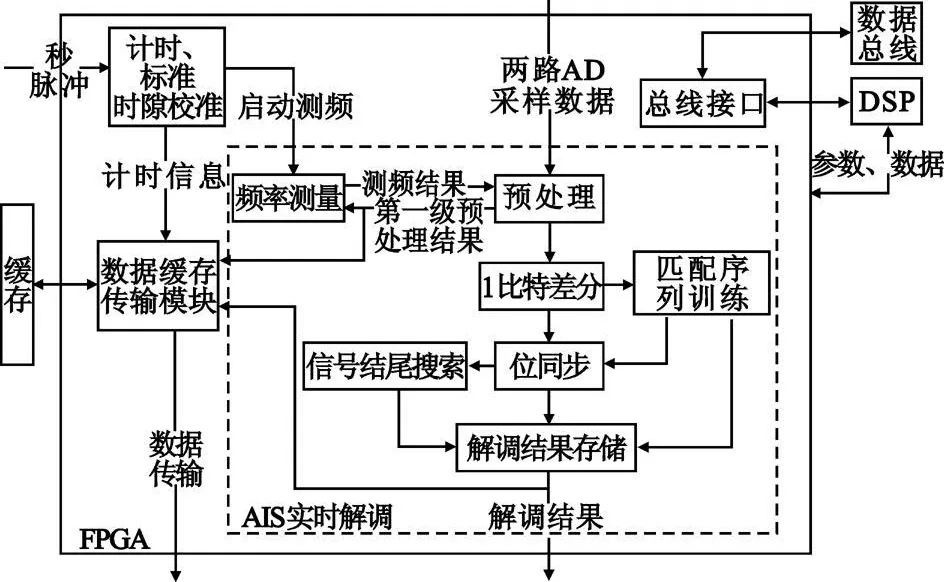

在前文的系統(tǒng)構(gòu)成中可見,AIS偵察接收機(jī)的功能集中在信號處理模塊實現(xiàn);而在信號處理模塊中,其主要功能基本在FPGA中完成,包括數(shù)字解調(diào)、數(shù)據(jù)存儲傳輸、總線接口等。FPGA的數(shù)字信號處理設(shè)計實現(xiàn)結(jié)構(gòu)如圖3所示。

圖3 FPGA數(shù)字信號處理實現(xiàn)結(jié)構(gòu)Fig.3 Architecture of digital signal processing in FPGA

信號處理對兩路AIS信號完成相同的數(shù)字信號處理功能。FPGA內(nèi)的設(shè)計按功能可以劃分為4部分,即AIS實時解調(diào)、計時和標(biāo)準(zhǔn)時隙校準(zhǔn)、數(shù)據(jù)緩存輸出、總線接口。

AIS實時解調(diào)完成對輸入信號的預(yù)處理、測頻、基帶解調(diào)、位同步等處理,最終可以實時得到兩路信號的解調(diào)結(jié)果,并提供預(yù)處理結(jié)果和解調(diào)結(jié)果兩種數(shù)據(jù)給緩存輸出模塊,是FPGA內(nèi)設(shè)計的核心部分。

計時和標(biāo)準(zhǔn)時隙校準(zhǔn)模塊通過秒脈沖和FPGA內(nèi)部時鐘激勵計時,利用AIS信號時間上的規(guī)律,在每個標(biāo)準(zhǔn)時隙開始時產(chǎn)生測頻啟動信號,是實時解調(diào)模塊的關(guān)鍵控制信號來源,并為各種數(shù)據(jù)的緩存提供高精度的時標(biāo)。

數(shù)據(jù)存儲輸出模塊設(shè)計時,考慮后續(xù)的數(shù)字信號處理,選擇AIS采樣信號或者解調(diào)結(jié)果作為數(shù)據(jù)源,同時利用FPGA內(nèi)的高精度計時,給數(shù)據(jù)打上時標(biāo);再考慮到實際應(yīng)用中,可能面對的平臺數(shù)據(jù)總線被占用,在本系統(tǒng)無法將實時數(shù)據(jù)輸出時,可以將數(shù)據(jù)先存儲在內(nèi)部緩存中,事后再通過平臺數(shù)據(jù)總線輸出。

總線接口的設(shè)計給系統(tǒng)內(nèi)的AIS偵察接收機(jī)提供了一個對外的接口。通過FPGA完成的DSP和數(shù)據(jù)總線之間數(shù)據(jù)交互,平臺或者后端的控制單元可以完成對AIS偵察接收機(jī)的控制和數(shù)據(jù)交互。

3.3 AIS信號實時解調(diào)的實現(xiàn)

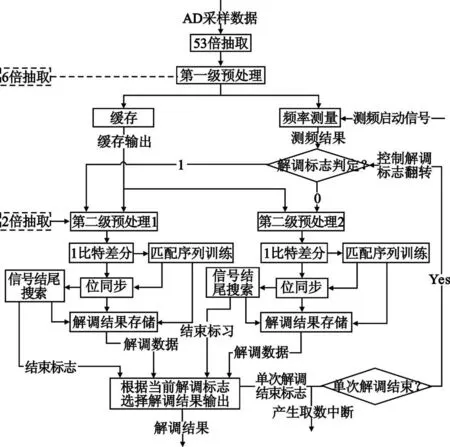

對AIS信號進(jìn)行偵收時,在FPGA內(nèi)實現(xiàn)的實時解調(diào)結(jié)構(gòu)和流程如圖4所示。

圖4 FPGA內(nèi)實時解調(diào)的實現(xiàn)結(jié)構(gòu)與流程Fig.4 Implementation of real-time demodulation in FPGA

測頻模塊中,先對該信號進(jìn)行2倍抽取,再完成FFT運算,測頻精度為10 Hz級,得到的測頻結(jié)果作為第二級預(yù)處理下變頻的參數(shù)。頻率測量中需要注意的是測頻時間選取原則,詳見下文計時、標(biāo)準(zhǔn)時隙校準(zhǔn)的實現(xiàn)。值得注意的是,由于FFT測頻有較大延時,為達(dá)到實時解調(diào)的目的,在第一級預(yù)處理后增加了緩存模塊,并且對后續(xù)的第二級預(yù)處理和數(shù)字解調(diào)都采用乒乓操作。利用FPGA工作時鐘頻率高、處理效率高的特點,以增加資源消耗為代價,提高設(shè)計的實時處理能力。乒乓操作的控制主要在測頻結(jié)果到第二級混頻的選擇輸入和解調(diào)結(jié)果的選擇輸出,設(shè)置解調(diào)標(biāo)志位作為判斷依據(jù),解調(diào)標(biāo)志位在完成單次的AIS信號解調(diào)后翻轉(zhuǎn)。

在精測頻的引導(dǎo)下,完成第二級預(yù)處理后得到基帶信號,按照3.1節(jié)中的相關(guān)算法完成對信號的基帶解調(diào)得到目標(biāo)信息比特流;再經(jīng)由匹配序列訓(xùn)練完成對目標(biāo)信號的幀頭以及最佳采樣點的搜索;根據(jù)前面搜索到的最佳采樣點信息,結(jié)合采樣率、碼片長度等信息,位同步模塊完成碼元的提取,得到解調(diào)數(shù)據(jù);再對得到的解調(diào)數(shù)據(jù)進(jìn)行信號結(jié)尾搜索,得到結(jié)束標(biāo)志;最后,利用搜索到的幀頭和結(jié)尾的時刻,控制對解調(diào)數(shù)據(jù)的存儲,將包括幀頭在內(nèi)的完整有效的AIS解調(diào)數(shù)據(jù)存儲下來,經(jīng)過乒乓控制模塊選擇輸出,得到最終的解調(diào)結(jié)果。

3.4 計時、標(biāo)準(zhǔn)時隙校準(zhǔn)的實現(xiàn)

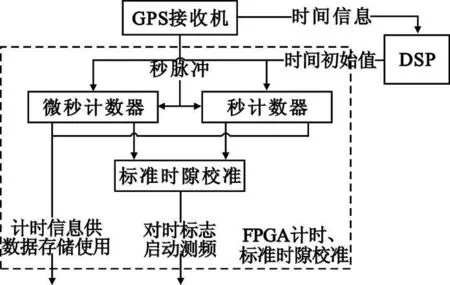

計時、標(biāo)準(zhǔn)時隙校準(zhǔn)模塊是設(shè)計中重要的控制部分,主要工作原理是利用AIS信號發(fā)射時間上的特點,根據(jù)GPS的標(biāo)準(zhǔn)時計時產(chǎn)生測頻啟動信號和精確的計時信息,提供給測頻模塊和數(shù)據(jù)存儲輸出模塊使用。其實現(xiàn)結(jié)構(gòu)如圖5所示。

圖5 FPGA內(nèi)計時、標(biāo)準(zhǔn)時隙校準(zhǔn)的實現(xiàn)Fig.5 Timer and calibration for standard slot in FPGA

其中秒計數(shù)器和微秒計數(shù)器設(shè)計均為32位,因為32位的秒計數(shù)器能夠以某年某月某日零時為起始時刻進(jìn)行累加,而在若干年內(nèi)不會溢出;微秒計數(shù)器工作時鐘為10MHz級,計時精度10 ns級,32位的寬度也保證了微秒計數(shù)器在1 s內(nèi)的計數(shù)不會溢出。

標(biāo)準(zhǔn)時隙校準(zhǔn)利用AIS信號在時間上的特點:1 min分為2250個標(biāo)準(zhǔn)時隙,以2 s為單位每2 s則有75個標(biāo)準(zhǔn)時隙,依此為基準(zhǔn)來判斷地面標(biāo)準(zhǔn)時隙時刻。每個時隙長度26.6666 ms,而計時精度為10 ns級,能夠精確地找到每個時隙的開始時刻(誤差小于等于100 ns,可以忽略),產(chǎn)生測頻啟動信號,并且利用前面提到的2 s 75個時隙的標(biāo)準(zhǔn),周期性地校準(zhǔn),避免長期計時可能產(chǎn)生的誤差。

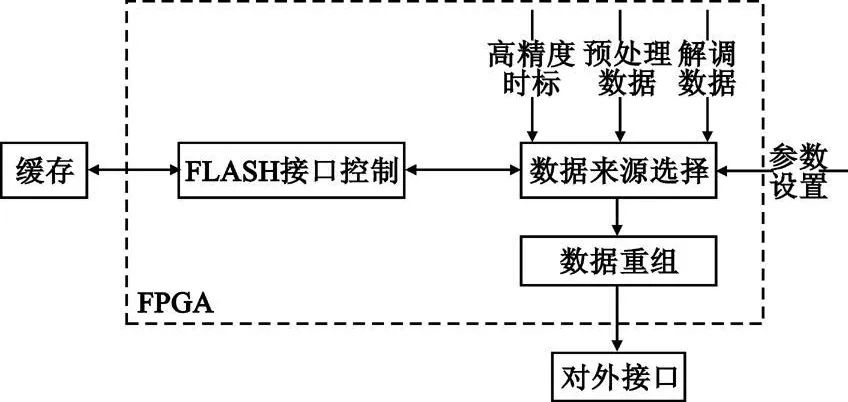

3.5 數(shù)據(jù)存儲和傳輸?shù)膶崿F(xiàn)

FPGA內(nèi)數(shù)據(jù)存儲和傳輸?shù)膶崿F(xiàn)如圖6所示。其主要功能是,根據(jù)外界設(shè)置的參數(shù),選擇性地將相關(guān)數(shù)據(jù)存儲或者通過對外接口輸出。輸入到本模塊的數(shù)據(jù)有兩種:第一級預(yù)處理的結(jié)果和解調(diào)結(jié)果。選用第一級預(yù)處理而不是采樣數(shù)據(jù)的原因是,信號本身帶寬較窄,可以使用采樣率較低的預(yù)處理數(shù)據(jù)提供給后端,作為AIS信號偵察的原始數(shù)據(jù);同時,使用較低采樣率的數(shù)據(jù),也有利于后續(xù)兩路信號數(shù)據(jù)實時輸出的實現(xiàn)。

數(shù)據(jù)存儲時,可以完成同時對兩路信號的第一級預(yù)處理結(jié)果的實時存儲,或者兩路信號最終解調(diào)結(jié)果的實時存儲;數(shù)據(jù)傳輸時,可以完成對兩路信號的第一級預(yù)處理結(jié)果的實時傳輸,或者對兩路信號最終解調(diào)結(jié)果的實時傳輸,或者將緩存內(nèi)數(shù)據(jù)輸出。傳輸過程中,完成數(shù)據(jù)選擇后,根據(jù)系統(tǒng)傳數(shù)組幀的定義,對數(shù)據(jù)進(jìn)行重組,再通過對外接口輸出。

圖6 FPGA內(nèi)數(shù)據(jù)存儲和傳輸?shù)膶崿F(xiàn)Fig.6 Data storage and transmission in FPGA

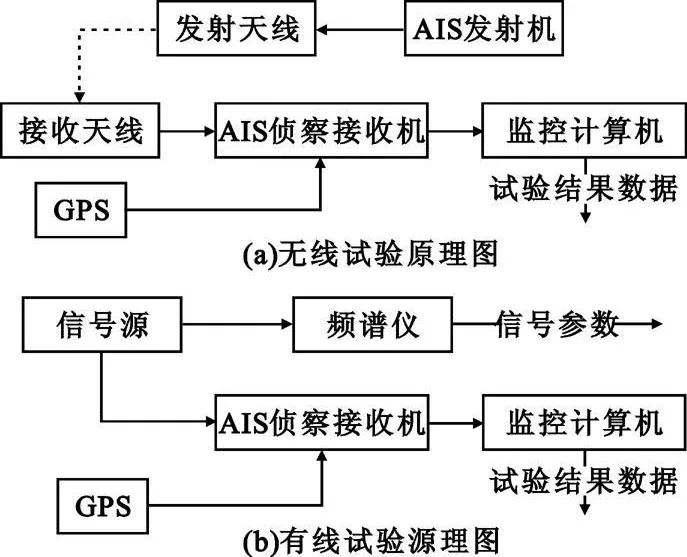

4 試驗與結(jié)果分析

為驗證上述方法實現(xiàn)的AIS偵察接收機(jī)效果,進(jìn)行了無線和有線兩種方式的實時偵收試驗。無線試驗主要驗證該系統(tǒng)在實際無線環(huán)境中的工作效果,有線試驗主要用于各種指標(biāo)的測試,其原理圖如圖7所示。兩種方式的試驗結(jié)果數(shù)據(jù)都在監(jiān)控計算機(jī)中讀取,監(jiān)控計算機(jī)通過CAN和LVDS與AIS偵察接收機(jī)完成交互數(shù)據(jù),并將試驗結(jié)果數(shù)據(jù)存儲在其中。試驗結(jié)果數(shù)據(jù)主要包括實時解調(diào)后輸出的數(shù)據(jù)和實時采樣后輸出的數(shù)據(jù),頻譜儀讀取的信號參數(shù)包括頻率、幅度等信息。

圖7 試驗原理Fig.7 Test principle

在有線和無線實驗測試環(huán)境下,改變信號強(qiáng)度和信噪比的AIS信號,通過對各種實驗數(shù)據(jù)的分析,得到以下實驗結(jié)論:

(1)本設(shè)計實現(xiàn)的AIS偵察數(shù)字信號處理能同時完成兩路信號的實時解調(diào),解調(diào)方式GMSK 9.6 kbit/s;在有線條件下,中頻輸入較小(不大于-30 dBm)時,解調(diào)性能達(dá)到誤包率不大于20%;

(2)本設(shè)計實現(xiàn)的AIS偵察數(shù)字信號處理能同時完成兩路信號的實時數(shù)據(jù)存儲傳輸功能,通過特殊數(shù)據(jù)序列和AIS解調(diào)結(jié)果數(shù)據(jù)測試,在較長時間內(nèi)(大于等于1 h)能保證數(shù)據(jù)實時、有效存儲傳輸。

5 結(jié)束語

根據(jù)設(shè)計方案實現(xiàn)的AIS偵察接收機(jī),處理能力較強(qiáng),能同時完成兩路AIS信號的實時解調(diào)、數(shù)據(jù)存儲傳輸;可擴(kuò)展性和通用性強(qiáng),能實時存儲輸出帶高精度時標(biāo)的采樣數(shù)據(jù)和解調(diào)數(shù)據(jù),為后續(xù)的各種處理手段提供了有效可靠的數(shù)據(jù),可以應(yīng)用于多種場合下的AIS信號偵察;并且,在實現(xiàn)的結(jié)構(gòu)流程和器件選擇方面,綜合考慮了成本控制,設(shè)計實用性高。

[1]CerveraM A,Ginesi A.Satellite-basedAIS SystemStudy[C]//Proceedings of the 26th International Communications Satellite SystemsConference.San Diego,CA:IEEE,2008:1-6.

[2]楊小牛,樓才義,徐建良.軟件無線電原理與應(yīng)用[M].北京:電子工業(yè)出版社,2001:21-56.YANG Xiao-niu,LOU Cai-yi,XU Jian-liang.Software radio principle and application[M].Beijing:Publishing House of Electronic Industry,2001:21-56.(in Chinese)

[3]曹志剛,錢亞生.現(xiàn)代通信原理[M].北京:清華大學(xué)出版社,1992:262-270.CAO Zhi-gang,QIAN Ya-sheng.Modern communication theory[M].Beijing:Tsinghua University Press,1992:262-270.(in Chinese)