被動模式的芯片IIC接口設計

一、IIC接口特點及應用

IIC(Inter-Integrated Circuit)總線是一種由荷蘭飛利浦(Philips)公司開發的兩線式串行總線,用于連接微控制器及其外圍設備。IIC總線產生于在80年代,最初為音頻和視頻設備開發,如今主要在服務器管理中使用,其中包括單個組件狀態的通信。IIC總線最主要的優點是其簡單性和有效性。由于接口直接在組件之上,因此IIC總線占用的空間非常小,減少了電路板的空間和芯片管腳的數量,降低了互聯成本。IIC總線的另一個優點是,它支持多主控,其中任何能夠進行發送和接收的設備都可以成為主總線。一個主控能夠控制信號的傳輸和時鐘頻率,在任何時間點上只能有一個主控。IIC總線是由數據線SDA和時鐘SCL構成的串行總線,可發送和接收數據。在CPU與被控IC之間、IC與IC之間進行雙向傳送。各種被控制電路均并聯在這條總線上,但就像電話機一樣只有撥通各自的號碼才能工作,所以每個電路和模塊都有唯一的地址,在信息的傳輸過程中,IIC總線上并接的每一模塊電路既是主控器(或被控器),又是發送器(或接收器),這取決于它所要完成的功能。CPU發出的控制信號分為地址碼和控制量兩部分,地址碼用來選址,即接通需要控制的電路,確定控制的種類;控制量決定該調整的類別(如對比度、亮度等)及需要調整的量。這樣,各控制電路雖然掛在同一條總線上,卻 彼此獨立,互不相關。

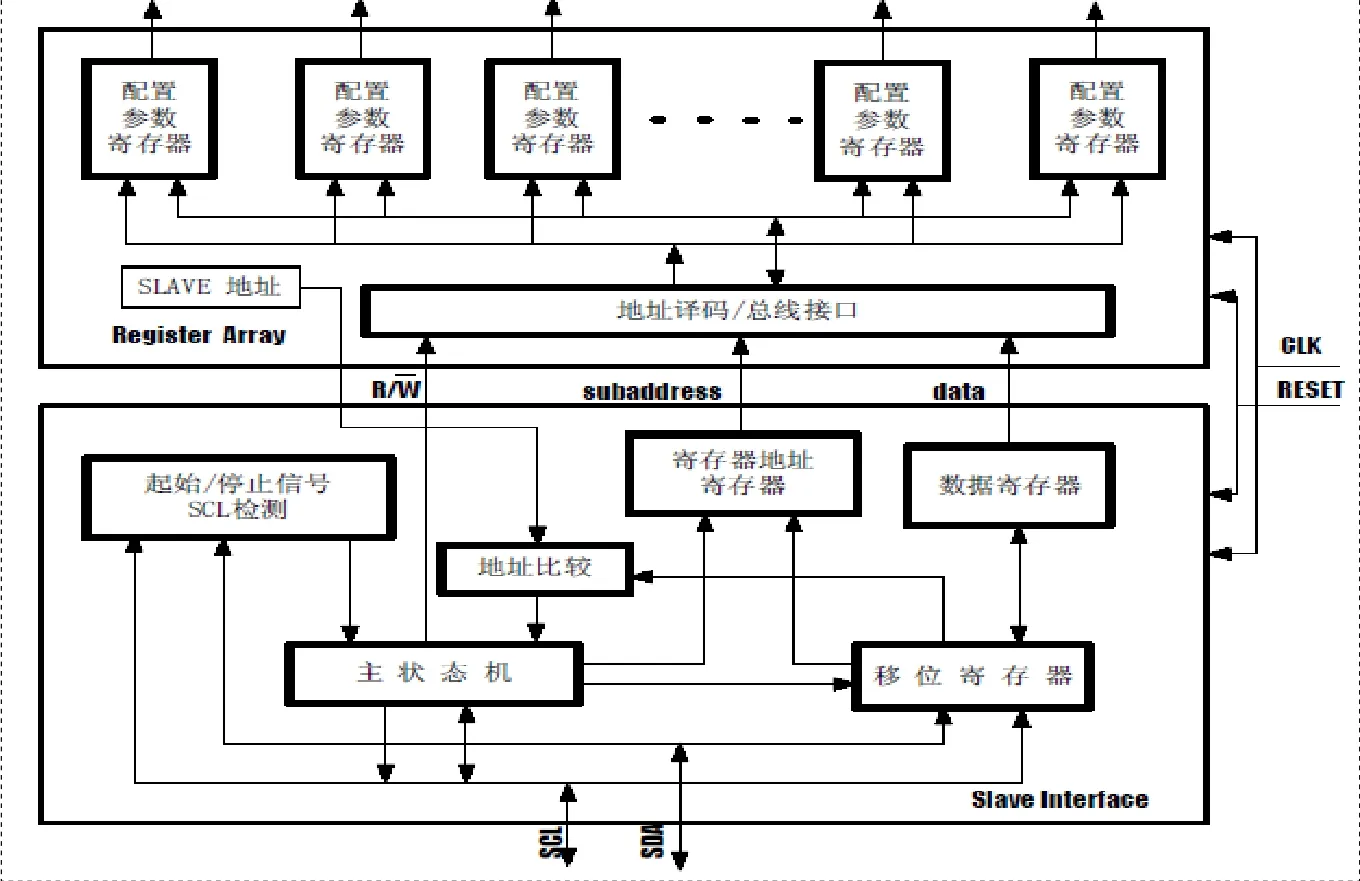

圖1 被動模式IIC接口電路框圖

二、被動模式的芯片IIC接口設計

在實際設計芯片與計算機接口電路時,通常只希望計算機能夠檢測、控制芯片的內部工作情況,因此可以簡化IIC接口電路,只需要實現處于被動模式的芯片IIC接口電路即可。該接口電路主要用于芯片內部寄存器的讀寫操作,這樣可以減小占用過多的芯片面積資源。

根據IIC總線上數據傳輸過程的特點,使用狀態機控制整個系統的運作,可以使設計思路清晰明確,程序模塊化。系統上電復位后即進入狀態機,并在狀態機控制下完成起始/停止信號的自動檢測,slave地址、子地址、配置數據的接收及響應,發送數據及檢測響應,對配置寄存器陣列的尋址和連續讀寫等功能。此外,系統最高數據傳輸速度應由時鐘CLK及寄存器的存取速度決定。根據電路的功能,整個IIC接口電路的系統框圖如圖1所示。

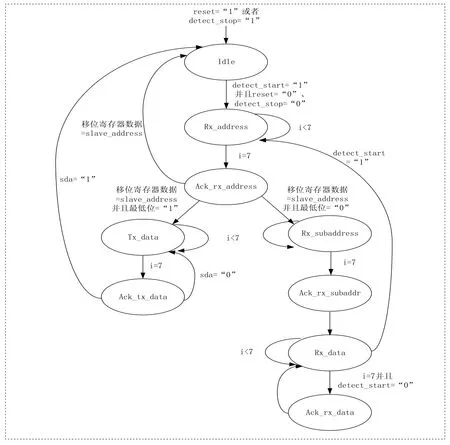

狀態機如圖2所示,其中Idle是空閑狀態,Rx_address狀態接收slave地址,Ack_rx_address狀態接收slave地址響應,Tx_data狀態發送數據,Ack_tx_data狀態發送數據響應,Rx_subaddress狀態接收子地址,Ack_rx_subaddr狀態接收子地址響應,Rx_data狀態接收數據,Ack_rx_data狀態接收數據響應。狀態機的狀態轉換在SCL下降沿后第5個時鐘周期進行,但是,停止信號出現后,總線被釋放,SCL/SDA均為高電平,除非再出現起始信號進行數據傳送,SCL不會再出現下降沿。如果停止信號出現后,就把空閑狀態賦給下一個狀態,將沒有SCL時鐘下降沿做時間基準完成狀態轉化(即狀態機進入到空閑狀態)。為了解決這個問題,需要將停止信號看作復位信號。一旦有停止信號出現,當前狀態在下一個CLK脈沖強制進入到空閑狀態,而不再等到SCL下降后第5個時鐘脈沖。

圖2 被動模式IIC接口電路狀態機

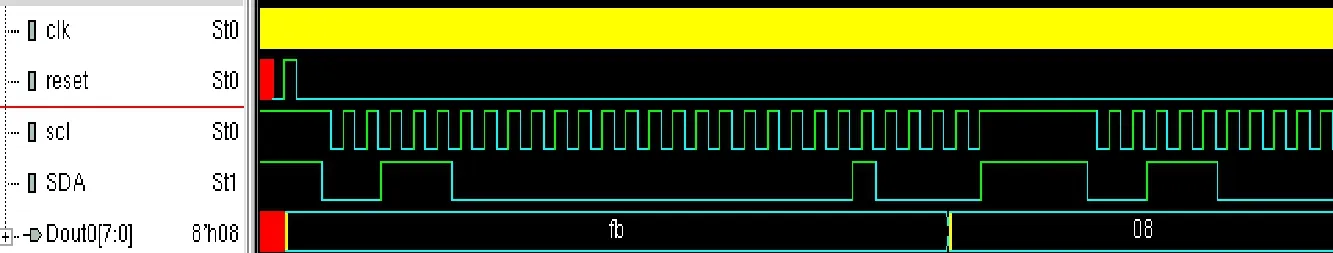

圖3 被動模式IIC接口電路仿真波形

Ack_rx_subaddr狀態之后,master既可能發送數據又可能發送重復停止信號或者停止信號,如何區分是哪種情況成為正確進入相應的狀態的關鍵。這里設定ack_rx_subaddr狀態之后無條件緊跟rx_data狀態。這樣,如果在rx_data狀態時檢測到重復起始信號,丟棄已經接收的數據,并在SCL時鐘下降沿后第5個時鐘周期進行狀態轉化進入rx_address狀態,否則繼續完成接收數據。若發現停止信號,處理如前所述。這樣做既滿足設計要求又不會增加多余的狀態。

master收到數據后沒有響應(SDA=1)表示master接收的是最后一個字節數據。在這種情況下,可以在SCL時鐘下降沿后第5個時鐘周期就直接進入到空閑狀態,處理接下來應該出現的重復起始信號或停止信號。

起始/停止信號、SCL檢測如下:

在高速時鐘CLK的上升沿采樣SDA、SCL,如果在前后兩個采樣點發現SDA從“1”變化到“0”而SCL保持“1”則認為master發出起始信號,將detect_start設置為有效。同理,若發現SDA從“0”變化到“1”而SCL保持“1”,則認為是停止信號,將detect_stop設置為有效。detect_start有效保持一個狀態周期,detect_stop有效保持一個時鐘周期,以避免誤操作。

依靠SCL時鐘下降沿進行狀態轉換以及在SCL時鐘上升沿將SDA的數據送入移位寄存器。移位寄存器在rx_address、rx_subaddress、rx_data狀態完成在數據采樣時刻(SDA數據有效時)對slave地址、寄存器子地址、數據的移位接收,接收完畢后在響應狀態將數據并行送往指定的寄存器,在ack_tx_data狀態和ack_rx_address狀態且讀寫控制位為高(r/w=1)時,并行輸入數據,在tx_data狀態發送時刻有效時輸出最高位,在數據采樣時刻有效時進行移位操作。

寄存器子地址寄存器實現完成對寄存器一次讀寫操作后地址自動增加的功能,這樣可以實現在對器件的配置時只輸入一次子地址就完成對所有的配置寄存器的配置。計數器寄存器記錄接收或發送的數據的位數,為狀態機提供控制信號。

三、被動模式的芯片IIC接口驗證

根據上面的狀態機,使用verilog編寫硬件描述代碼,為了減小競爭冒險、提高電路運行的可考性,所有電路均在同一時鐘控制下工作,例如,狀態轉化并沒有依靠SCL時鐘的下降沿觸發,而是利用高速時鐘的上升沿采樣SCL,檢測到SCL時鐘的下降沿后,在時鐘的上升沿觸發狀態轉化。這樣就避免了由于總線負載過重而導致SCL上升、下降時間太長所帶來的一系列問題。代碼編寫好后,運用modelsim進行仿真驗證,仿真驗證設計的IIC接口工作正確。圖3是計算機對IIC接口電路進行寫操作仿真得到的CLK、SCL、SDA波形,剛開始時,reset有個高電平脈沖,IIC模塊復位,IIC中第一個寄存器的數據Dout0[7∶0]被置為fb(16進制),之后開始對IIC的第一個寄存器寫入數據08,最終Dout0[7∶0]中的數據從fb為08,表明計算機成功完成了對芯片寄存器的控制。

四、結語

被動模式的IIC接口電路是IIC總線的一個簡化版本,通過被動模式的IIC接口電路,計算機可以檢測、控制芯片的狀況,本文分析了被動模式的芯片IIC接口設計,并通過modelsim驗證設計的正確性。

[1]徐偉,劉建成.基于模擬IIC總線的電壓測量系統[J].南京信息工程大學學報,2011,1.

[2]王鈺,潘仕彬,王卉.IIC在數據采集中的應用[J].科技廣場,2008,8.

[3]張文甲.IIC總線通信中主機控制器的設計與應用[J].電腦知識與技術,2007,1.

[4]徐廣振,張茂青,王力,黃穎.基于IIC總線的鍵盤讀取[J].江蘇電器,2007,4.

[5]夏宇聞.verilog數字系統設計教程[M].北京航空航天大學出版社,2008.