一種基于FPGA的可變模計數器的VHDL實現

開封大學機電工程學院 侯 靜

1.引言

EDA是將數字系統以某一種特定的表達方式輸入計算機開發平臺進行處理,經由綜合,仿真,下載到目標芯片,最終實現設計的智能化設計技術。其中輸入文件的種類眾多,有原理圖輸入法、硬件描述語言輸入法、狀態圖輸入法、波形輸入法等。

硬件描述語言(HDL)是EDA技術的重要組成部分,是設計數字系統的重要表達手段,和原理圖輸入法,波形輸入法相比,具有靈活度高,易于修改、升級,方便調用,庫資源豐富等優點。常見的HDL主要有VHDL、Verilog HDL、ABEL、AHDL等,其中標準化語言VHDL、Verilog使用最廣泛,可以被幾乎所有的EDA工具支持。

可變模計數器是數字系統中廣泛應用的一種電路模塊,本文討論了一種基于VHDL語言實現的可變模計數器的EDA設計方案,采用FPGA芯片作為設計載體,FPGA具有在線可重構的優點,如需對計數器的技術指標進行修改,只需修改源程序中的相應參數,重新進行編譯、仿真、配置即可,使得系統本身靈活性好,便于升級和維護。

2.可變模計數器的功能指標

本文設計的計數器為5位輸出可變模計數器,采用兩位控制信號選擇計數的模值,因此可進行四種模值的切換。計數器在工作時,可以通過控制信號m[1∶0]的值選擇相應的模值m,計數時,在每個時鐘的上升沿進行加法計數,從0計到m-1,然后自動歸零循環計數。在本設計中,輸出端口為5位,可以實現模小于等于32的計數應用。如果需要增可選擇模值的數量,只需要增加選擇控制信號位數即可。隨著模值的增大,還可以相應增加輸出端口信號的位數來對應。

3.可變模計數器的實現方案

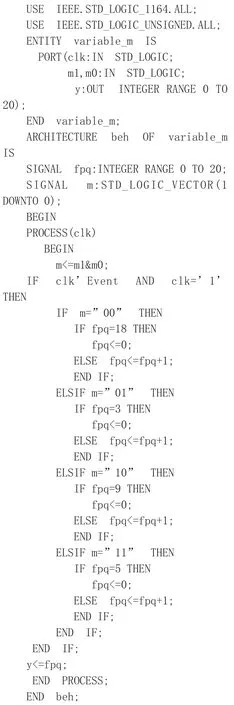

在本設計中,采用VHDL語言進行源程序的設計,源程序由實體和結構體兩個部分組成,在實體中定義了系統的輸入輸出端口,在結構體中行描述了計數器的邏輯功能。令兩位控制信號分別為m1、m0,計數脈沖為clk輸入時鐘信號,計數值輸出為5位二進制信號y。假設當控制信號m[1∶0]=0時,進行模19計數;m[1∶0]=1時,進行模4計數;m[1∶0]=2時,進行模10計數;m[1∶0]=3時,進行模6計數.該程序通過信號傳遞參數,如果想修改計數器的功能指標,只需要修改源程序中相應的端口參數和信號參數即可,修改設計非常方便、靈活。采用VHDL描述的源程序如下:

以上源程序在集成開發環境下通過綜合和適配,將行為和功能的高層次表達轉換為門電路的低層次表達,最終在硬件上實現系統功能。

4.可變模計數器的編譯與仿真結果

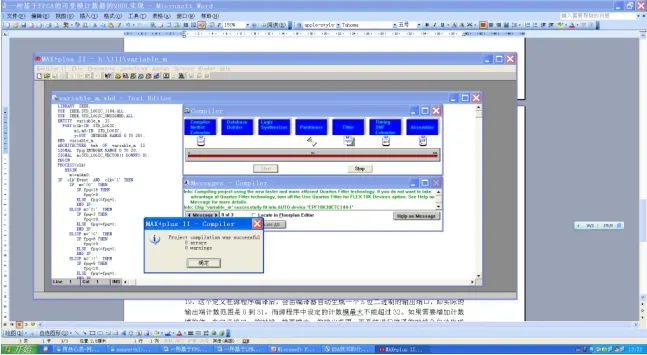

將編寫好的源程序與實體名variable_m同名保存在工程項目路徑下,文件名后綴為.vhd。本設計采用的芯片是Altera公司的Flex10k系列FPGA芯片EPF10K30ETC144-1,源文件通過編譯后系統的提示編譯成功,如圖1所示。

建立波形仿真文件,設置控制信號m[1∶0]的值分別為0和,2,在仿真窗口觀察仿真波形,仿真結果正確。仿真波形見圖2、圖3。

圖1

圖2

圖3

5.結束語

在本文編寫的源程序中,輸出端口y的范圍定義為0到20,是由于計數的模最大設置為19的緣故,這個定義在源程序編譯后,會由編譯器自動生成一個5位二進制的輸出端口,即實際的輸出端計數范圍是0到31,而源程序中設定的計數模最大不能超過32。如果需要增加計數模的值,在定義端口y的時候,就要增大y的輸出范圍,而系統進行編譯的時候會自動生成相應位數的輸出端口,從這點來看,VHDL語言設計的靈活性要遠遠好于原理圖輸入法、狀態圖輸入法、波形輸入法。

[1]潘松,黃繼業.EDA技術實用教程[M].北京:科學出版社,2002.

[2]楊曉慧,楊永健.基于FPGA的EDA/SOPC技術與VHDL[M].北京:國防工業出版社,2007.

[3]譚會生,瞿遂春.EDA技術綜合應用實例與分析[M].西安:西安電子科技大學出版社,2004.

[4]吳繼華,王誠.Altera FPGA/CPLD設計(高級篇)[M].北京:人民郵電出版社,2005.