基于NiosⅡ的UART設(shè)計(jì)與實(shí)現(xiàn)

王一平 , 王代強(qiáng) ,2

(1.貴州大學(xué) 貴州 貴陽(yáng) 550025;2.貴州大學(xué) 人民武裝學(xué)院,貴州 貴陽(yáng) 550025)

SOPC技術(shù)自2000年提出以來(lái),以其靈活性、可裁剪和擴(kuò)展、系統(tǒng)可編程等優(yōu)點(diǎn)被廣泛應(yīng)用于通信、軍事等嵌入式領(lǐng)域。SOPC技術(shù)以NiosⅡ處理器為核心采用軟硬件協(xié)同設(shè)計(jì)方案以及IP核復(fù)用等技術(shù)使得它在可靠性、體積、功耗、設(shè)計(jì)周期等方面實(shí)現(xiàn)了最優(yōu)化,是未來(lái)的SOC和嵌入式發(fā)展的方向。

傳統(tǒng)的UART專用芯片引腳多、內(nèi)部還有許多其他的功能模塊、占用面積大使得電路設(shè)計(jì)復(fù)雜,PCB面積增加。相對(duì)于集成度越來(lái)越高的SOC系統(tǒng)來(lái)說(shuō)越來(lái)越不符合要求。而基于SOPC技術(shù)的UART設(shè)計(jì)可以合理應(yīng)用在含有FPGA器件的系統(tǒng)中,將UART集成其中起到節(jié)約PCB面積的作用[1]。

文中設(shè)計(jì)了一種基于NiosⅡ的UART,并在EP2C8Q208C芯片上通過(guò)串口調(diào)試工具加以驗(yàn)證。

1 UART原理及協(xié)議介紹

串行異步接口即通用的異步收發(fā)器(UART,Universal Asynchronous Receiver Transmitter)成本低、傳輸線少、可靠性高因而應(yīng)用廣泛于。根據(jù)通信接口的傳輸速率、電氣特性、連接特性等的不同, 有 RS-232、RS-423、RS-499、RS-485等不同的通信協(xié)議。其中RS-232是目前廣泛采用的一個(gè)標(biāo)準(zhǔn),常用于短距離、低速、低成本的通信[1-2]。

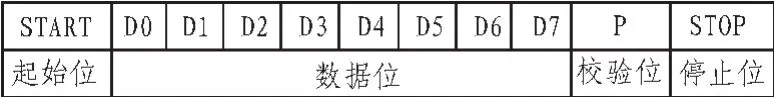

RS-232的基本通信只需要兩條信號(hào)線(RXD、TXD)就可以完成數(shù)據(jù)的相互通信,接受和發(fā)生采用全雙工形式,RXD是接受輸入端,TXD是發(fā)送輸入端。其基本的通信協(xié)議十分簡(jiǎn)單:以低電平為起始位,高電平為停止位,中間可傳輸5~8比特?cái)?shù)據(jù)和1比特奇偶校驗(yàn)位,奇偶校驗(yàn)位的有無(wú)和數(shù)據(jù)比特的長(zhǎng)度由通信雙方約定,一幀數(shù)據(jù)傳輸完畢后可以繼續(xù)傳輸下一幀數(shù)據(jù),也可以繼續(xù)保持為高電平,兩幀之間保持高電平,持續(xù)時(shí)間可以任意長(zhǎng)。圖1為UART的數(shù)據(jù)幀的格式。

圖1 UART的數(shù)據(jù)幀格式Fig.1 UART data frame form

2 SOPC中硬件構(gòu)造實(shí)現(xiàn)

1)系統(tǒng)的整體硬件結(jié)構(gòu)

SOPC系統(tǒng)一般Nios軟核cpu、存儲(chǔ)器、I/O等構(gòu)成。用戶的根據(jù)需求選擇Nios軟核、存儲(chǔ)器、IP核或自定義IP核,分配好內(nèi)存地址和中斷優(yōu)先級(jí)別,就構(gòu)成了所需要的系統(tǒng)。Nios軟核與UART核、其他IP核、SDRAM等通過(guò)Avalon總線僑聯(lián)并與外設(shè)相連[3]。

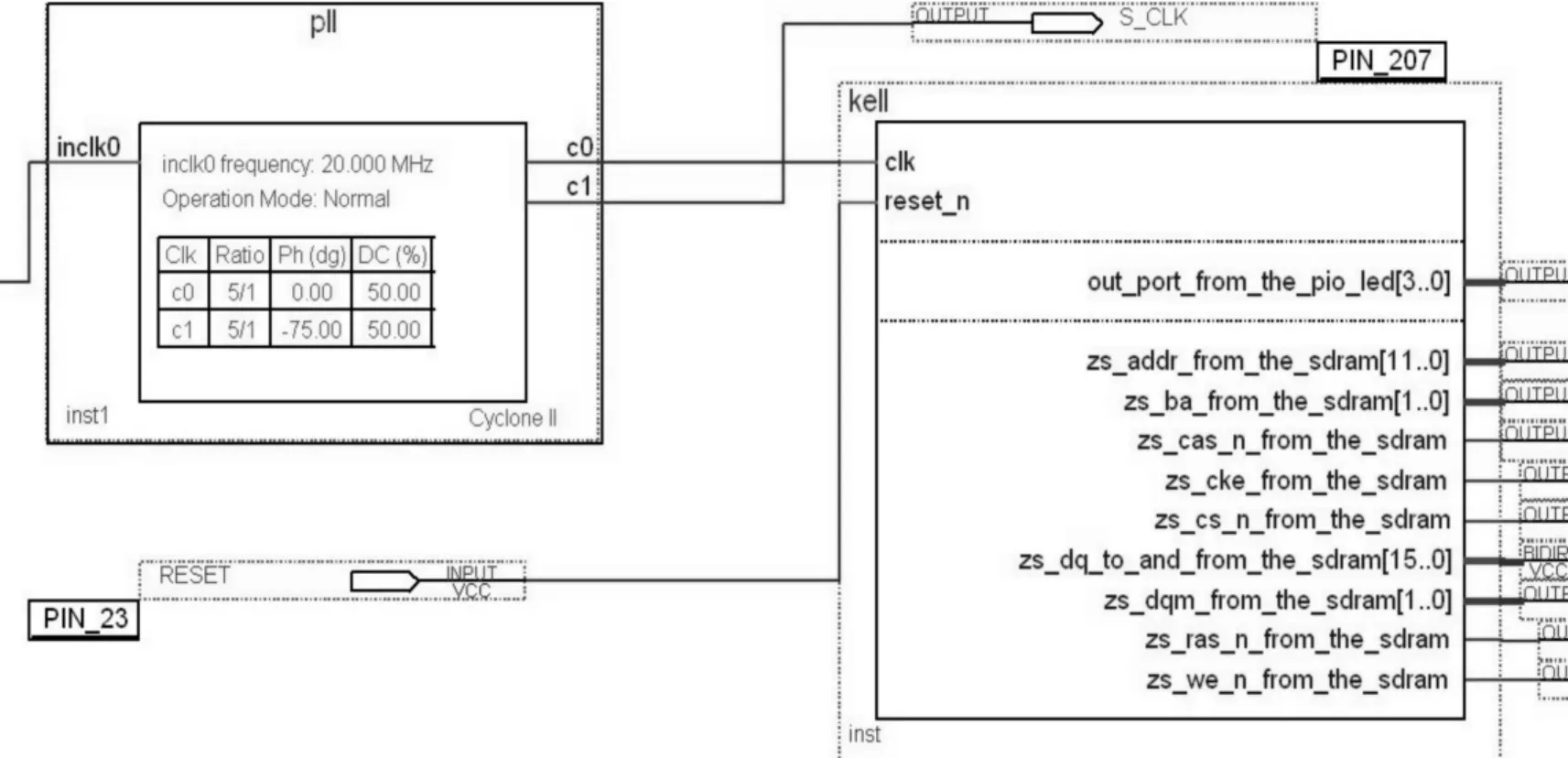

NiosⅡ提供3種供用戶選擇的軟核,在本文設(shè)計(jì)中我們選擇NiosⅡ/e(經(jīng)濟(jì)型)軟核,并調(diào)用系統(tǒng)自帶的UART核(RS232)、epcs、sdram等構(gòu)成系統(tǒng),并設(shè)置好中斷級(jí)別和內(nèi)存地址,就生成了SOPC系統(tǒng)[4]。由于用到了SDRAM需要調(diào)用控制外部的sdram器件,由FPGA引入時(shí)鐘信號(hào)后需要加上一個(gè)鎖相環(huán)(PLL)模塊倍頻生成Nios系統(tǒng)和sdram的控制信號(hào),并設(shè)置兩個(gè)控制信號(hào)間的相位差。整體系統(tǒng)的電路原理圖如圖2所示。

圖2 SOPC系統(tǒng)的組件Fig.2 SOPC system’smodule

2)UART 核的設(shè)置

作為整個(gè)系統(tǒng)的核心的UART核,是一款quartus軟件自帶的IP核。它內(nèi)部是包括波特率除數(shù)寄存器、接收寄存器、發(fā)送寄存器、移位寄存器等。它提供目標(biāo)系統(tǒng)與開(kāi)發(fā)系統(tǒng)的連接。從功能設(shè)計(jì)上看:它與Nios軟核通過(guò)avalonz總線結(jié)構(gòu)連接,并提供外部的電平轉(zhuǎn)換模塊的接口。

UART核中初始的波特率設(shè)置為115200,Baud rate can be changed by software選項(xiàng)設(shè)置成允許軟件設(shè)置波特率;檢驗(yàn)方式、數(shù)據(jù)位、停止位等設(shè)置為none、8和1。

3)電平轉(zhuǎn)換電路模塊

本文中采用的RS-232標(biāo)準(zhǔn)規(guī)定邏輯1的電平為-15~-3 V,邏輯0的電平為+3~+15 V。COMS電路的電平范圍一般是從0 V到電源電壓,F(xiàn)PGA的I/O輸入輸出電壓通常為0~3.3 V,為了保證 FPGA設(shè)計(jì)的 UART接口與 RS-232電平保持一致,必須加電平轉(zhuǎn)換芯片,進(jìn)行UART的TTL/COMS電平與RS-232電平的轉(zhuǎn)換[5]。本設(shè)計(jì)采用MAX232電平轉(zhuǎn)換芯片,支持兩個(gè)串口的電平轉(zhuǎn)換。

3 軟件設(shè)計(jì)分析

1)UART核的寄存器結(jié)構(gòu)及C語(yǔ)言描述

根據(jù)表1中UART核的寄存器結(jié)構(gòu)[6-7],筆者在 sopc.h文件中定義一個(gè)UART_ST的結(jié)構(gòu)體。它包含在硬件中用到的接收數(shù)據(jù)位、發(fā)送數(shù)據(jù)位、狀態(tài)、控制及除數(shù)五個(gè)共用體。其中的每個(gè)共用體根據(jù)偏移量決定順序,并包括一個(gè)結(jié)構(gòu)體和用于整體清零WORD的變量。在sopc.h中還用宏定義聲明了UART的基地址。然后需要編寫(xiě)一個(gè)uart.h文件用于以結(jié)構(gòu)體形式聲明UART核工作所用到的receive_flag、receive_count、*init等Nios開(kāi)發(fā)包自帶的需要用到的UART函數(shù)。編寫(xiě)sopc.h及uart.h文件是為了在后面編寫(xiě)UART核的驅(qū)動(dòng)時(shí)候方便調(diào)用。

表1 UART核寄存器映射Tab.1 UART nuclear register map

2)UART核的驅(qū)動(dòng)描述

在編寫(xiě)成功前面 sopc.h及 uart.h文件后, 需要根據(jù)UART的工作原理編寫(xiě)RS232工作的驅(qū)動(dòng)文件uart.c。

在uart.c文件中我們要聲明定義以下函數(shù):

①intuart_send_byte(unsigned char data)用于發(fā)送一個(gè)字節(jié)

②void uart_send_string (unsigned int len, unsigned char*str)發(fā)送字符串?dāng)?shù)據(jù)

③intset_baudrate(unsigned intbaudrate)軟件設(shè)置波特率

④void uart_ISR(void)聲明 uart所用到的中斷

⑤int uart_init(void)初始化 uart等等。

版面關(guān)系僅列舉uart_send_byte函數(shù)的代碼:

4 系統(tǒng)的實(shí)現(xiàn)驗(yàn)證

整個(gè)系統(tǒng)的軟件硬件部分都編輯完成后首先通過(guò)quartus和Nios IDE軟件編譯并將硬件仿真無(wú)錯(cuò)誤后下載到目標(biāo)芯片EP2C8Q208C中通過(guò)串口調(diào)試工具實(shí)現(xiàn)PC機(jī)和UART的通信。

圖3 串口的調(diào)試Fig.3 Serial port debugging

5 結(jié)束語(yǔ)

基于NiosⅡ設(shè)計(jì)的UART在以FPGA為核心控制芯片的嵌入式系統(tǒng)中有著一定的優(yōu)勢(shì),可以節(jié)約PCB面積并且具有成本低、易于升級(jí)等優(yōu)點(diǎn)。該系統(tǒng)實(shí)現(xiàn)了基本的UART功能,并且后續(xù)的可以通過(guò)添加FIFO模塊提升傳輸容量等。

[1]Ahera Corporation.NiosⅡ proce,~sor reference handbook[S].[S.1.]Ahera Corporation,2003.

[2]任愛(ài)鋒,初秀琴.基于FPGA的嵌入式系統(tǒng)設(shè)計(jì)[M].西安:西安電子科技大學(xué)出版社,2004.

[3]Ahera Corporation.Quartus 11 version 6.0 handbook[S].[S.1.]Ahera Corporation,2006.

[4]鄭啞民,董曉舟.可編程邏輯器件開(kāi)發(fā)軟件Quartus II[M].北京:國(guó)防工業(yè)出版社,2006.

[5]夏宇聞.Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程[M].北京:北京航空航天出版社,2003.

[6]王建校,危建國(guó).SOPC設(shè)計(jì)基礎(chǔ)與實(shí)踐[M].西安:西安電子科技大學(xué)出版社,2006.

[7]張志剛.FPGA與SOPC設(shè)計(jì)教程——DE2實(shí)踐[M].西安:西安電子科技大學(xué)出版社,2007.