位填充導致USB數據傳輸紊亂的一種解決方案

董 劍,李同合

(西安交通大學 電子與信息工程學院微電子學系,陜西 西安 710049)

在USB數據傳輸中,為了保證數據的可靠性,需要對所傳輸的數據進行NRZI編解碼、添加/去除位填充和串并/并串轉換[1-3]。NRZI編碼可以保證有足夠的跳變沿在接收端進行時鐘恢復;位填充是為了保證信號具有足夠的變化量;串并轉換可以降低后端數據處理模塊的工作頻率。

以USB 2.0設備控制器為例。在向主機發送數據時,其收發器模塊先要將協議層傳來的8位(或16位)并行數據轉換成串行數據,然后添加位填充(每6個連續的1后要加入一個0),最后進行NRZI編碼。反之,在接收主機發來的數據時,收發器模塊要先對數據進行NRZI解碼,再去除位填充,最后轉換成8位(或16位)并行數據傳給協議層[4-6]。

USB 2.0設備控制器的收發器和后端協議層的工作時鐘頻率不同。對于具有高速(480 Mb/s)和全速(12 Mb/s)兩種傳輸速度的USB 2.0設備控制器來說,收發器在高速、全速模式下的工作時鐘頻率分別為480 MHz和12 MHz;而協議層在高速、全速模式下的工作時鐘頻率統一為60 MHz(8位并行數據時,對于16位并行數據為30 MHz)[1-3]。

由于添加/去除位填充導致了每字節數據傳輸所需的時間的增加或減少,再加上收發器和協議層工作時鐘頻率的差別,可能會導致數據的紊亂。

1 數據紊亂的原因分析

假設USB 2.0設備控制器的收發器工作時鐘為clk,協議層使用8位并行數據,工作時鐘為60 MHz的phy_clk,分析數據紊亂產生的原因。

1.1 高速接收模式

USB 2.0協議中定義了信號RxValid表示接收數據有效,在phy_clk上升沿,若RxValid=1,協議層可以從收發器提取8位并行數據使用[1-3]。RxValid信號變化后至少需要保持1個phy_clk周期,才能保證其被協議層的phy_clk時鐘采樣。

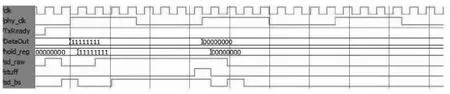

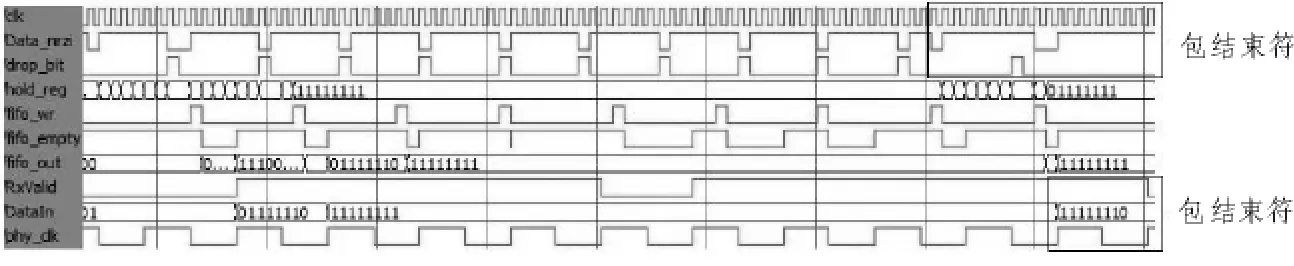

圖1中Data_nrzi為已經過NRZI解碼的串行輸入數據;drop_bit為去位填充提示,當drop_bit=1時說明出現了連續6個數據1,其后的數據0為位填充位應該除去,不放入hold_reg中;Data_nrzi經過去位填充后放入 hold_reg中,hold_reg收集了8個Data_nrzi數據后,將這8個數據以并行數據DataIn的形式傳給協議層。

從圖1中可以看出,在處理第二組8位數據時,由于其中有一個位填充需要去除,故處理這組數據用了9個clk周期,導致第一組8位并行數據在DataIn中的持續時間為9個clk周期,比正常多了1個clk周期。這樣有兩個缺點:

1)1個phy_clk周期為8個clk周期,第1組8位數據持續9個clk周期有可能會被協議層采樣兩次。如圖1中所示,第1組數跨越了兩個phy_clk的上升沿,被采樣兩次。雖然出現這種情況的概率較小,但并不是不存在,且隨著位填充數量的增多,這種多次采樣的可能性會增大。

2)每當位填充的個數達到8個,輸出的DataIn被協議層采樣到的并行數據總量會比正確的情況多1個,從而導致數據接收錯誤。

為了避免上述錯誤,通常的做法是每當去除了8個位填充數據時,就令RxValid=0并持續1個phy_clk周期,使協議層暫停采樣一次,從而避免第2)類錯誤的發生[7-8]。但這種做法不能完全避免第1)類錯誤的發生。

1.2 高速發送模式

USB 2.0協議中同樣定義了信號TxReady表示收發器準備好發送數據,在phy_clk上升沿,若TxReady=1,協議層便傳輸過來1個8位并行數據讓收發器發送出去[1-3]。同理TxReady信號變化后也至少要保持1個phy_clk周期。

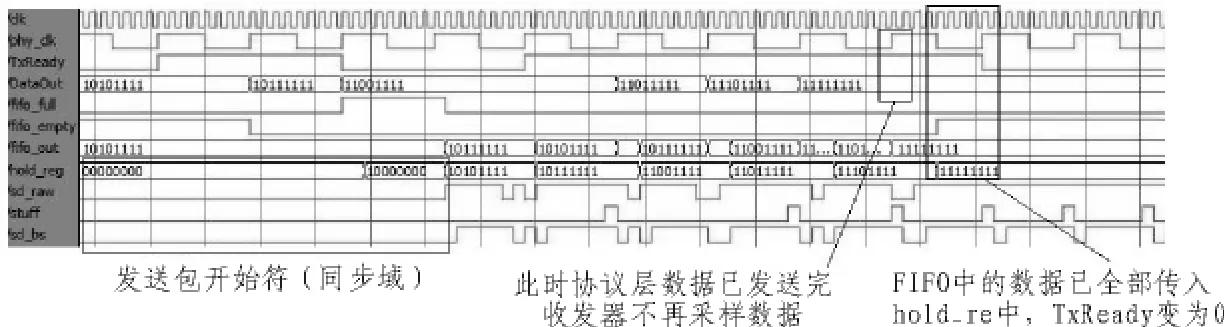

圖2中,TxReady由0變為1代表收發器已將包的同步域發送完畢,開始發送早已從協議層傳來的第1組8位并行數據;DataOut為協議層傳來的8位并行數據;在clk上升沿,將DataOut數據讀取到暫存器hold_reg中;sd_raw為并串轉換后的串行數據;stuff為添加位填充信號,當連續出現6個1時,stuff=1在串行數據中添加1位位填充數據0;sd_bs為添加位填充后的數據,對sd_bs進行NRZI編碼后即可發送給主機。

從圖2中可以看出,高速發送模式出現了兩類錯誤:

1)TxReady由 0變為1后開始發送第1組 8位并行數據,而當phy_clk上升沿來臨后 DataOut和hold_reg先后變為了第2組8位并行數據,此時第1組數據并不一定恰好剛剛發完,于是會造成數據缺失或重復發送,同時使后面的數據發送混亂。圖2中Txready變為1后sd_raw發送的第1個數據1為同步域的最后一位,接著發送的數據00為第1組數據中的2位,其余6位還未發送hold_reg中的數據已變成了第2組并行數據。

圖2 高速發送數據模式Fig.2 High-speed send datamode

2)處理第2組并行數據時,由于需要添加位填充,故第2組數據的處理時間需要9個clk周期。由于phy_clk的周期為8個clk周期,故第2組并行數據的持續時間為8個clk周期。于是第2組并行數據的最后一位還未發送,第3組數據已取代了第2組數據。

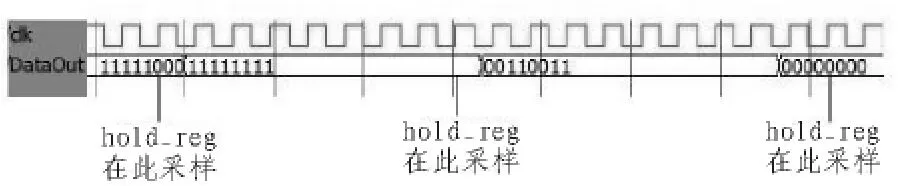

避免上述錯誤的常用方法是令hold_reg在其暫存的8位數都轉換成串行數據sd_raw后再讀取DataOut中的數,而不是在每個clk上升沿都讀取。同時,每當添加了8個位填充數據,就令TxReady=0并持續1個phy_clk周期,從而令DataOut暫停變化一次[7-8]。這樣做雖然解決了上述問題,但卻帶來了一個新的錯誤,如圖3所示。

圖3 添加位填充造成的數據丟失Fig.3 Data loss caused by bit stuffing

圖3中,共要發送4組并行數據。假設發送完同步域后,hold_reg恰好在第一組數據的最后進行采樣,則處理第2組數據時需要添加2個位填充位,處理時間為10個clk周期。同時由于位填充沒有達到8個,TxReady持續為1,DataOut每過8個clk就變換一次。結果導致第3組數據被錯過,沒有被hold_reg采樣到。這種錯誤的發生概率雖然很小,但不能完全避免。

1.3 全速收發模式

全速模式下clk的頻率為12 MHz,即1個clk周期為5個phy_clk周期[1-3]。在接收數據時,當hold_reg集齊8位數據后,將其傳輸到DataIn中

并令RxValid=1且持續1個phy_clk,其余時刻令RxValid=0;在發送數據時,當hold_reg中的8位數據全部轉換成串行數據后,令 TxReady=1并持續1個phy_clk,其余時刻令TxReady=0[7-8]。因而RxValid和TxReady信號為離散脈沖形式,且脈沖寬度為1個phy_clk周期,不會出現上述錯誤。

綜上所述,USB 2.0傳輸中位填充造成數據總量的增減會影響數據傳輸的準確性,需加以解決。

2 解決方案

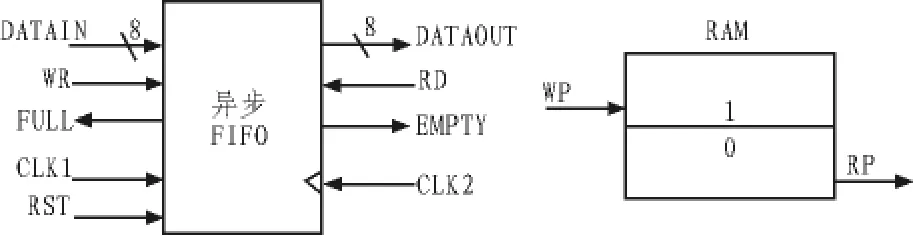

通過在收發器和協議層之間添加一個2×8位的異步FIFO[9]作為緩存區,可以解決上述問題。如圖4所示,異步FIFO的讀操作與寫操作分別由兩個異步時鐘clk1和clk2控制,異步復位信號rst同USB設備控制器的復位信號相同。

圖4 讀寫異步FIFO示意圖Fig.4 Read and write asynchronous FIFO schematic

接收數據時,當hold_reg集齊8位數據,可在clk時鐘控制下將其中的數據寫入FIFO中;而在phy_clk上升沿,若FIFO中有數據,則令RxValid=1并讀出1組并行數據傳給協議層,否則令RxValid=0且不讀數據。經分析,此處使用1×8位的FIFO足以滿足要求,不會出現FIFO中有數據未讀出新數據又寫入的情況,但為了保證不出現特殊情況,這里使用2×8位的FIFO,以保證可靠性。

發送數據時,在phy_clk上升沿,若FIFO有空間,則令TxReady=1并將DataOut中的數據寫入FIFO,否則令TxReady=0且不寫入數據,當協議層數據全部發送完畢令TxReady=0;在FIFO寫滿的同時也令 TxReady=0;當 hold_reg中的數據全部轉換為串行數據后,在clk時鐘控制下從FIFO中取出一組數據放入hold_reg中;當FIFO中沒有數據時,說明數據發送完畢,可以發包結束符。

3 仿真驗證及實驗結果分析

3.1 高速接收模式

當位填充較多致使數據處理時間過長,導致FIFO中沒有數據時,RxValid變為了0且持續了1個phy_clk周期。從圖中可看出輸出數據DataIn在RxValid=1時的寬度都為1個phy_clk周期,沒有出現多于1個phy_clk周期的情況。

3.2 高速發送模式

圖6為高速發送模式的仿真結果。從圖中可以看出,收發器工作正常,避免了上述錯誤的發生。在收發器還在發送同步域時,協議層就已經開始向FIFO中寫數據,當寫滿FIFO后,TxReady變為0,協議層暫停向FIFO傳輸數據,直到FIFO有空間后才繼續傳輸數據。同步域發送完畢后,hold_reg從FIFO中取出數據并依次發送,沒有出現數據缺失或重復發送。從圖中可看出從協議層輸入的數據DataOut在TxReady=1時的寬度都為1個phy_clk周期,沒有出現多于1個phy_clk周期的情況,從而不會被FIFO重復采樣。

圖5 使用異步FIFO的高速接收模式Fig.5 High-speed receivemode using asynchronous FIFO

圖6 使用異步FIFO的高速發送模式Fig.6 High-speed send mode using asynchronous FIFO

3.3 全速收發模式

據1.3中所述,全速收發模式不會出現類似錯誤,但若是全速高速模式使用不同的收發方式,會增加系統的復雜度和設計難度。異步FIFO同樣可以用于全速收發模式,只需要將clk的頻率變為12MHz即可,其余與高速收發模式相同,在此不再贅述。

4 結束語

文中通過在收發器與協議層之間增加一個2×8位的異步FIFO作為緩存區,解決了USB 2.0設備控制器在數據傳輸過程中因位填充而造成的數據紊亂問題,使數據不會出現缺失或重復,類似方法和思想可以用于其他數據傳輸處理過程。

[1]Compaq, Intel, et al.Universal Serial Bus Specification Revision 2.0[S].Compaq Computer Corp,2000.

[2]Intel Corporation.USB 2.0 Transceiver Macrocell Interface(UTMI) Specification[S].Intel Corporation,2001.

[3]周立功.USB 2.0與OTG規范及開發指南[M].北京:北京航空航天大學出版社,2004:130-162.

[4]Babulu K,Rajan K S.FPGA Implemtation of USB Transceiver Macrocell[C]//First Interfanation Conference on Emerging Trends in Enginerring and Technology,IEEE,2008:966-970.

[5]Lin H Q, Chen Y.Design and implementation of USB 2.0 device controller IP soft core[J].Ship Electronic Engineering,2008,28(3):151-153.

[6]Jolfaei F A, Mohammadizadeh N.High Speed USB 2.0 Interface for FPGA Based Embedded Systems[C]//The 4th International Conference on Embedded and Multimedia Computing,2009:1-6.

[7]Elio A A,D M,Edgardo G,et al.A Low Cost FPGA based USB Device Core [C]//2008 4th Southern Conference on Programmable Logic, Proceedings,2008:149-154.

[8]田群朝.專用雙緩沖端點USB 2.0設備控制器的研究與設計[D].西安:西安交通大學,2011.

[9]Lou T L.Using FIFOs to Realize the High Rates Data Communication between USB and DSP [C]//First International Workshop on Education Technology and Computer Science,2009:989-992.