基于FPGA的數控系統脈沖式速度控制模塊實現技術

朱興華,左健民,2,汪木蘭,蘇 薇

ZHU Xing-hua1,ZUO Jian-min1,2,WANG Mu-lan3,SU Wei4

(1. 常州數控技術研究所,常州 213164;2. 江蘇技術師范學院,常州 213001;3. 南京工程學院 先進數控技術江蘇省高校重點建設實驗室,南京 211167;4. 江蘇大學 機械工程學院,鎮江 212013)

0 引言

速度控制功能在計算機數控(Computer Numerical Control,CNC)系統中發揮著重要作用,它接受插補運算結果(命令值),并控制伺服電動機,其性能直接影響和決定了CNC系統的快速性、精確性和穩定性。

由于技術的發展,脈沖式速度控制方式應用越來越廣泛,不僅步進電動機工作于脈沖控制方式,而且交流伺服單元也可工作于脈沖控制方式。為了易于敘述實現思路和說明實現技術,本文以步進電動機伺服裝置實現過程為例。步進電動機是一種將電脈沖信號轉換成相應角位移和線位移的執行元件,其轉速與電機繞組相電流的切換頻率成正比。因其結構簡單和運行穩定可靠,可以和其他元器件組成簡單實用的全數字化伺服系統,且不需要反饋環節,故在數控系統脈沖式速度控制場合獲得了成功應用[1]。步進電動機的起動頻率特性使其啟動時不能直接加載到運行頻率,需要經歷“啟動—加速—恒速—減速—停止”的升降速過程[2]。對步進電動機速度控制實現方式的研究文獻很多,如使用單片機與PC機、定時器和寄存器等實現速度控制[3~5],并且大多數是由軟件實現,在控制的快速性和穩定性等方面不如早期的硬件電路。由于早期硬件電路較復雜,調整不便,后期的CNC系統中軟件實現比較廣泛。隨著電子技術快速發展,FPGA(Field Programmable Gate Array,現場可編程門陣列)的綜合性能和集成度等方面得到很大提高,可以滿足軟件硬化實現速度控制模塊功能的需要[6]。本文介紹使用FPGA軟件硬化技術實現數控系統中脈沖式速度控制模塊功能,并采用定時法原理予以實現。

1 脈沖式速度控制

1.1 定時法脈沖式速度控制

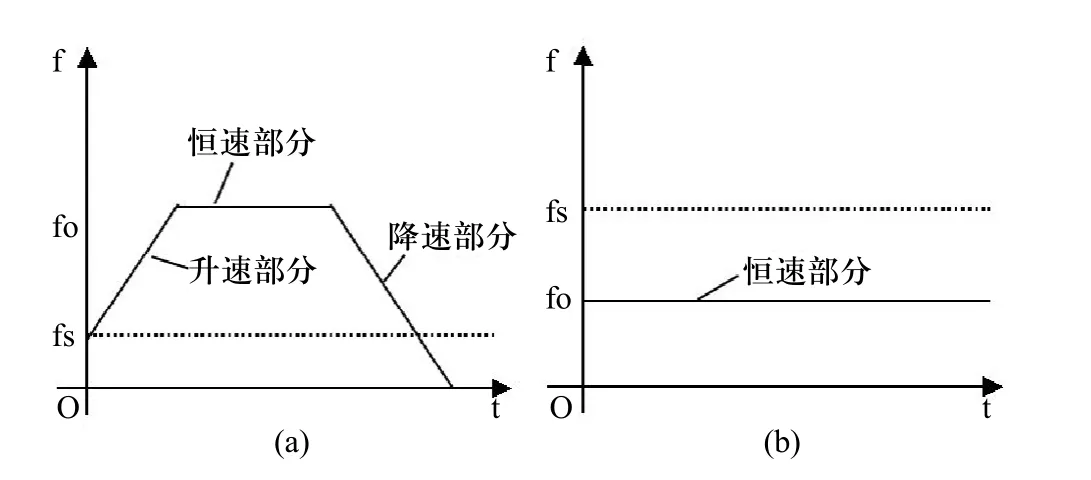

步進電動機的速度控制規律一般有直線型、指數型和拋物線型速度控制[7]。由于步進電機的轉速正比于控制脈沖的頻率,故調節控制脈沖頻率就可以達到調節電動機轉速的效果。本文采用了直線型控制速度方案,相應的步進電動機速度控制過程如圖1所示。

圖1 步進電動機速度控制過程

實現直線型速度控制方案的方法有定時法和定步法。本文采用定時法實現升降速控制,即按一定的時間間隔(Dt)改變步進電動機的運行頻率,從而實現升降速控制。為了確保步進電動機運行穩定且不發生失步或過沖現象,每改變一次運行頻率,步進電機運行一段時間(一定步長)。在選擇Dt時要注意每次的頻率變化量不得大于步進電動機所允許的突跳頻率值,否則會引起步進電動機發生失步或堵轉現象,從而導致定位誤差增大或無法正常運轉,甚而會損壞電機。

1.2 脈沖式速度控制實現流程

如果進給的行程比較長,則脈沖式伺服單元的速度控制過程不但有恒速段,還包含升速段和降速段,且降速段是升速段的逆過程,相應速度(脈沖頻率)變化曲線如圖1(a)所示。如果進給的行程很短,不足以完成一個定時時間間隔的升速和降速過程時,就不必進行升降速控制,而是以較低的適當設定速度走完整個行程,則速度控制過程只有恒速段,相應的速度(脈沖頻率)變化曲線如圖1(b)所示。

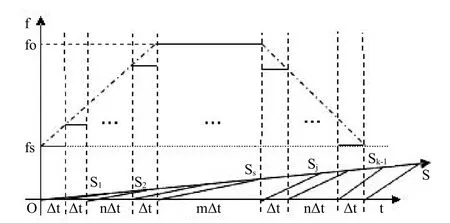

根據最佳升降頻控制規律[8],可推出步進電機的“頻率—步長—時間”關系曲線如圖2所示。

圖2 步進電機的“頻率—步長—時間”關系曲線

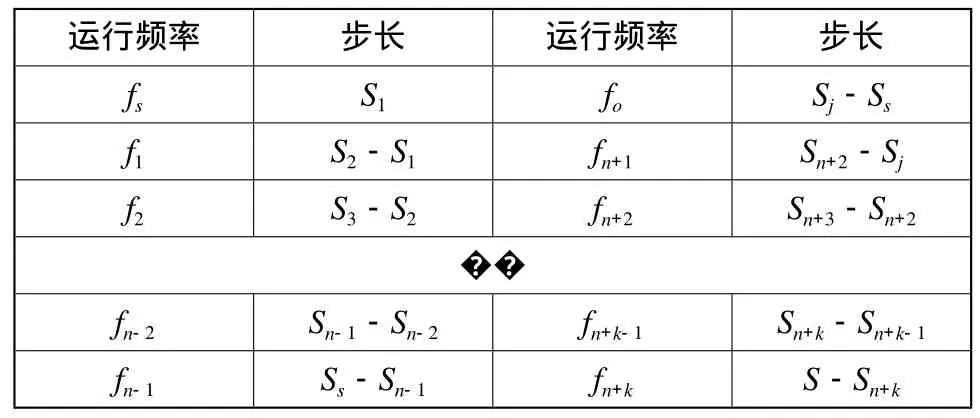

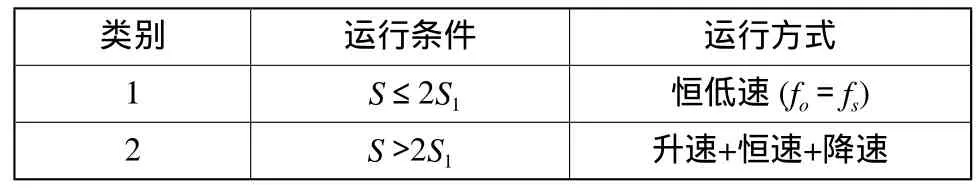

圖2中,步進電動機以起始頻率fs開始作升速運動,經過Dt時間,運動S1步長后,再以頻率f1作升速運動,同樣經過Dt時間,運動S2步長,如此經過若干Dt時間,到達頻率fo,以fo作恒速運動,經過mDt 時間后作與升速過程相反的降速運動。Ss為升速段的總步長,Sj為升速段和恒速段的總步長,S為整個過程的總步長。頻率與步長之間對應關系如表1所示,進一步根據圖2和表1可以總結出脈沖式速度控制運動方式和相應的滿足條件如表2所示。

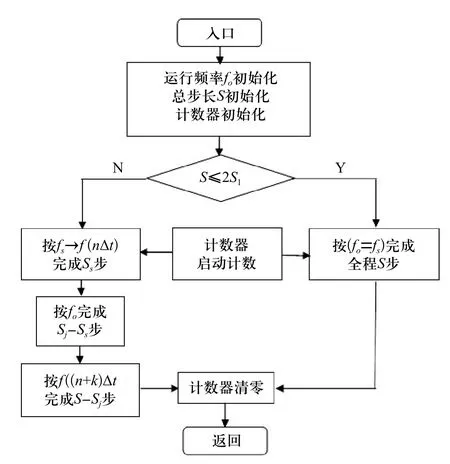

當模塊初始化以后,首先根據S、S1、Ss和Sj等變量之間的關系,選擇相應的運行方式,然后根據如圖3所示的脈沖式速度控制流程走完整個行程。

表1 運行頻率變化與步長之間對應關系

表2 脈沖式速度控制運行方式及滿足條件

圖3 脈沖式速度控制流程

2 脈沖式速度控制模塊設計與實現

2.1 FPGA和Quartus II

CYCLONE II 系列FPGA器件是美國Altera公司的中端產品,本文選用器件型號為EP2C8芯片,它具有8256個邏輯單元(LE),26塊M4K存儲器,165888 bits存儲器容量,13個乘法器,2個鎖相環(PLL),182個用戶可用引腳數。

Quartus II設計軟件是Altera提供的FPGA軟件開發環境,由原先的MAX+PLUS II演變而來,繼承了MAX+PLUS II工具的優點,能夠直接滿足各種設計需要,可為單芯片可編程系統(SOPC)提供全面的設計環境,已成為Altera公司新一代的EDA設計工具。

2.2 脈沖式速度控制模塊的硬化實現

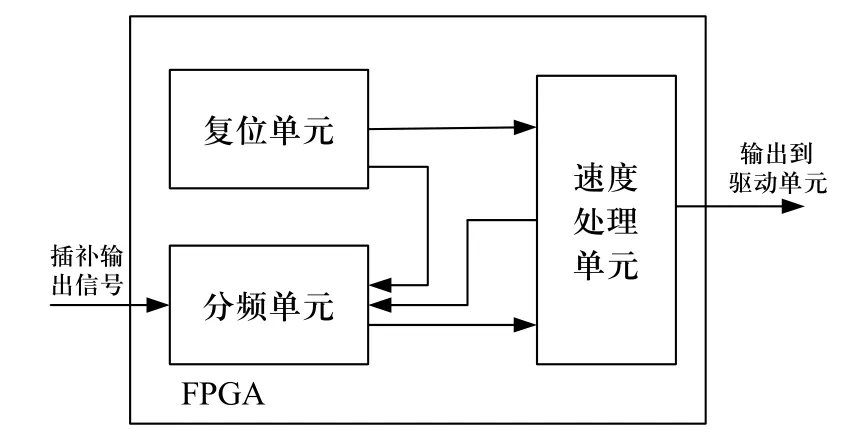

脈沖式速度控制模塊由復位單元、分頻單元和速度處理單元組成。使用軟件硬化技術把步進電動機升降速軟件實現過程采用FPGA硬件電路實現,并將整個脈沖式速度控制模塊功能固化到單芯片,也相當于定制一個專用控制芯片,其內部原理結構如圖4所示。

圖4 脈沖式速度控制模塊內部結構簡圖

圖4中復位單元的作用是負責整個速度控制模塊的復位、清零和置位等工作。分頻單元的作用是生成升速、恒速和降速段控制信號的脈沖頻率。速度處理單元的作用是當分頻單元傳來脈沖頻率(時鐘)時,根據計數器的數值反饋分頻控制信號至分頻單元和最終輸出信號至脈沖式伺服驅動單元。

頻選信號計數器i的數值把分頻控制信號f_ctr數值發送到分頻單元,分頻單元把與f_ctr數值對應的分頻信號發送到速度處理單元作為時鐘輸入,速度處理單元在時鐘的控制下,根據定時碼計數器的數值輸出速度控制信號。

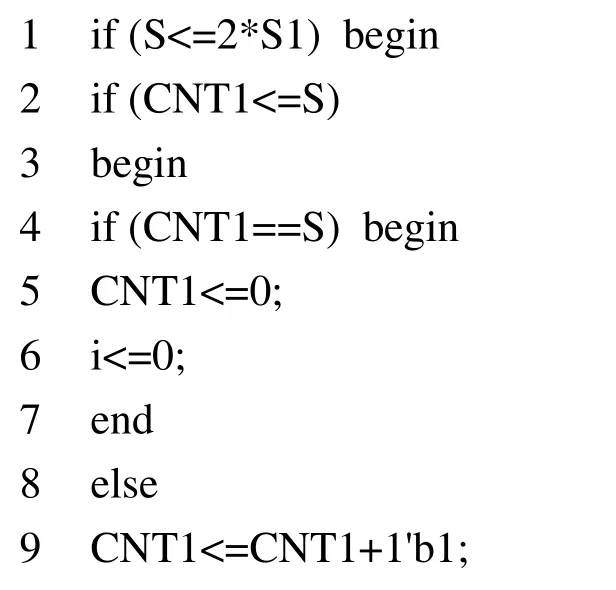

運動方式為第1類別情況下,即“恒低速”運行時,計數器初始化并根據判斷條件確定是否計數,在條件滿足時計數器累加到總步長S,表示到達目的地。相應的部分硬件描述語言程序如下:

其中fo為運行頻率,fs為有載起始頻率,CNT1為計數器,S為總步長。第1行表述“恒低速”運行條件判斷,條件滿足后,第2行表述計數器值是否小于等于總步長,若計數器值等于總步長,則計數器清零,頻選信號計數器值清零,如第5行、第6行所述,否則計數器值累加,如第9行表述。

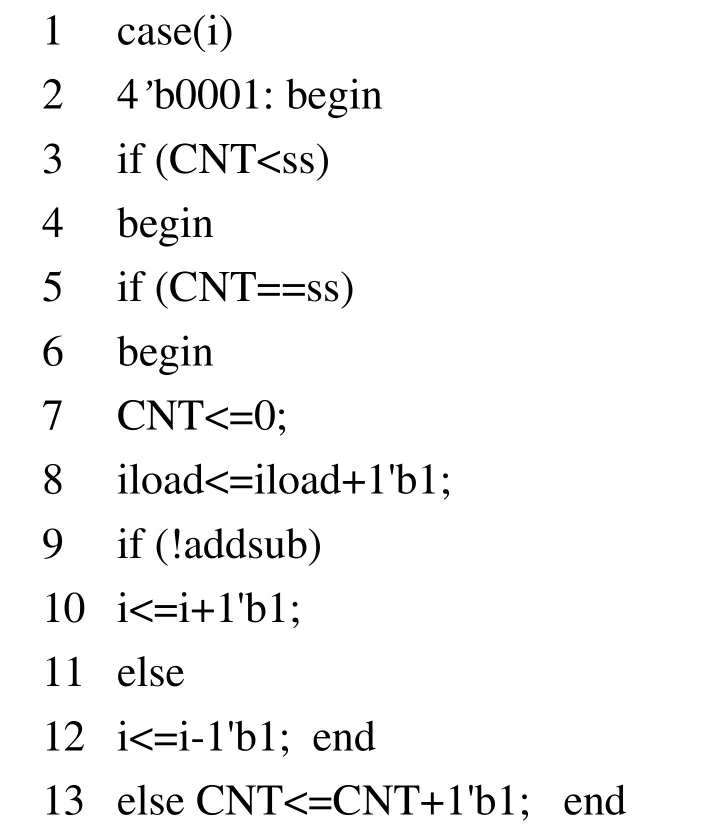

運動方式為第2類別情況時,速度處理單元在分頻時鐘的控制下,加減計數器對輸入脈沖個數進行計數,計數值達到定時數值時,計數器i加1,f_ctr數值改變,速度處理單元分頻時鐘更新,加減計數器再次對輸入脈沖個數進行計數,如此循環。當i計數到與Ss所對應的定時數值時,執行恒速階段。恒速階段完成以后,i進行累減運算進入降速階段,處理過程與加速過程相反,直到i=1停止。使用case語句來處理頻率選擇后的過程,部分硬件描述語言程序如下:

其中CNT為計數器,ss為在Dt時間內頻率對應的步長,addsub為計數器i值的增減信號,iload為計數器i值的增減控制信號,此段處理方法與第1類別運動方式相似。

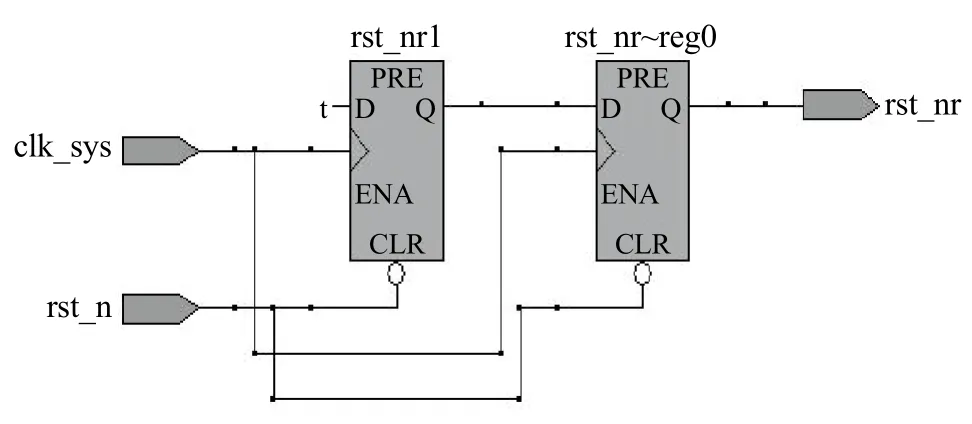

所設計的復位單元采用了異步復位、同步釋放的雙緩沖電路,可以較好地解決同步復位資源消耗過多和異步復位的亞穩態問題,相應的復位單元內部電路原理結構如圖5所示。

3 仿真驗證與波形分析

本設計在Quartus II 9.0環境中采用Verilog HDL語言編寫,應用于CYCLONE II 系列EP2C8Q208C8芯片。經過編譯和綜合,通過ModelSim SE軟件仿真驗證了設計的正確性。速度控制模塊共消耗了457個LE(邏輯單元),71個寄存器,51個可用管腳。

圖5 異步復位和同步釋放電路

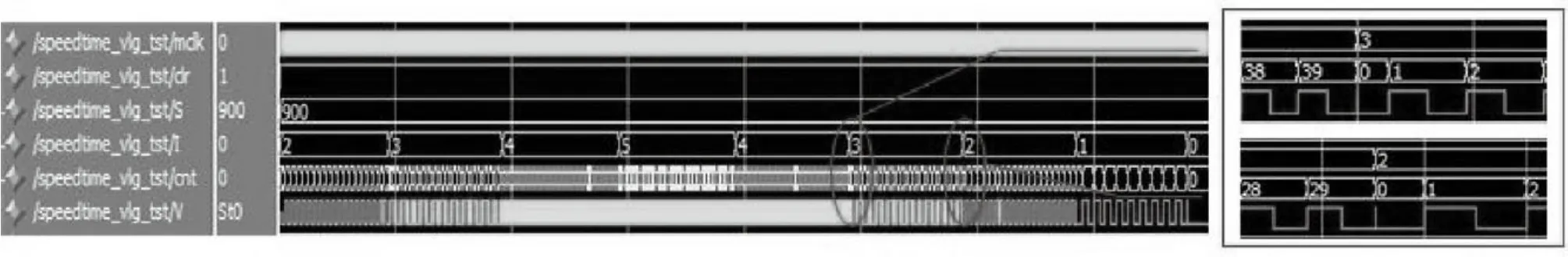

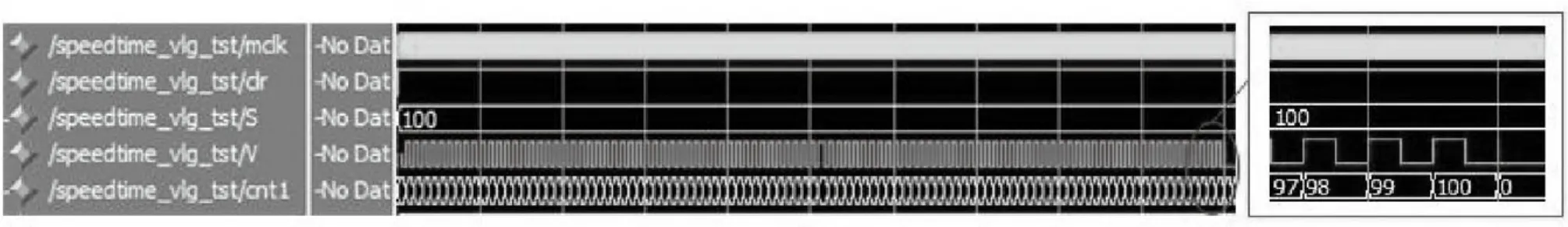

為了仿真時便于觀察,模塊時鐘使用50MHz,分頻單元將50MHz分頻為100Hz、200Hz……900Hz、1kHz,設置 fs為 400Hz,Dt為 100ms。

在第1類別運行方式下,fs設置為200Hz,S1置為200,S置為100,其仿真結果波形如圖6所示。

在第2類別運行方式下,fs設置為200Hz,S1置為200,S置為900,其仿真結果波形如圖7所示。

在仿真結果波形圖中,mclk為主時鐘50MHz;clr為復位、清零和置位等信號,低電平有效;V為速度信號輸出。

4 結束語

圖6 第1類別運動方式仿真圖

圖7 第2類別運動方式仿真圖

根據數控機床脈沖式速度控制的功能需求,利用Verilog HDL語言設計了基于FPGA的步進電動機升降速控制模塊,并進行了仿真,驗證了設計的正確性。本文的主要工作體現在根據步進電動機升降速軟件實現流程提出了FPGA硬化實現的具體方法,提高了系統的運行速度,相對于早期硬件實現電路,減少了元器件數量,提高了系統的可靠性,增強了模塊的可移植性和適用性。在仿真中出現的毛刺現象和定時間隔可調實現是以后進一步研究的內容。

[1] 汪木蘭. 數控原理與系統[M]. 北京:機械工業出版社,2007.

[2] 龐淑娟,倪受東. 基于FPGA的步進電機速度控制器的設計[J]. 數字技術與機械加工工藝裝備,2008(4):32-33.

[3] 黃勇,廖宇,高林. 基于單片機的步進電機運動控制系統設計[J]. 電子測量技術,2008(5):150-154.

[4] 楊國良,高瑞斌. 步進電機的加減速控制設計[C]. 第十四屆中國小電機技術研討會,2009.

[5] 李翠敏,高有行. 用寄存器實現步進電機速度控制[J].驅動控制,2005(5):14-16.

[6] 姚遠,李辰. FPGA應用開發入門與典型實例[M]. 北京:人民郵電出版社,2010.

[7] 徐煜明. 步進電機速度控制的研究與實現[J]. 工礦自動化,2007(2):82-84.

[8] 王玉琳,王強. 步進電機的速度調節方法[J]. 電機與控制應用,2006(33):53-56.