基于PC104和FPGA的數據采集系統的研究和實現

程 艷 ,孫樹敏 ,張海濤 ,李廣磊 ,袁 帥 ,趙 鵬 ,毛慶波

(1.山東電力集團公司電力科學研究院,山東 濟南 250021;2.山東彼岸電力科技有限公司,山東 濟南 250101)

0 引言

電力系統的無功補償和無功平衡,是保證電網電源質量的基本條件,對保證電力系統的安全穩定與經濟運行起著重要作用。尤其是對于并網的風電場來說,所安裝的動態無功補償裝置,是作為調節本風電場無功的電壓平衡的最主要的電氣設備,它的運行狀態和運行效果的優化與否[1],對于風電場的穩定運行有著重要作用,因此有效、準確地監控和測量動態無功補償裝置的運行狀態則顯得尤為重要。

數據采集系統可以檢測風電場并網點、主變低壓側和動態無功補償裝置的三相基波電壓、電流,從而分析并網點的電能質量和無功補償裝置的運行狀態,并且可以對電壓的驟升、驟降進行監測和記錄,具有較強的實用性。

數據采集系統采用PC104+FPGA方案[2],數據采集用FPGA和調整同步A/D來實現,經接口芯片 PCI9054[3]通過 PCI總線與 PC104 實現雙向數據通信,從而在PC104上進行高速數據處理。

1 采集卡總體硬件設計

數據采集系統采集卡選用了具有低系統占用率、高傳輸速率特性的PCI總線,以保證采集卡與主機間海量數據高速傳輸的可靠性[4]。 由于PCI總線復雜的總線邏輯和電氣規范,采集卡使用專用PCI總線控制芯片負責與PCI總線連接。根據傳輸速率的要求以及采集卡需使用DMA傳輸方式的特點,選用了由PLX公司開發研制的PCI9054芯片。采集卡的核心處理器件是FPGA,數據的實時采集由它控制完成。FPGA選用美國ALTERA公司Cyclone系列芯片,型號為EPlC6Q240C8。由于數據采集要求高度同步,模數轉換選取TI的ADS8364芯片。數據采集卡的總體硬件設計結構如圖1所示。

圖1 數據采集卡的硬件結構框圖

1.1 PCI9054的功能設置及硬件連接

PCI9054作為PLX公司研制的32位33 MHz的PCI總線主控I/O加速器接口芯片,實現PCI總線和LOCAL總線之間數據傳輸,通過外圍控制電路實現PC104和外圍設備的橋接,該芯片符合PCI規范2.2版本,同時兼容PCI規范2.1,本地端突發傳輸速率可達峰值132 MB/s,支持復用或非復用的32位局部總線操作。該芯片支持VPD的PCI擴展,支持PCI雙地址周期,地址空間高達4 GB。同時具有可選的串行EEPROM接口,8個32 Bit Mailbox寄存器和2個32位Doorbell寄存器。芯片核心采用3.3 VCMOS技術,兼容5 V信號環境,符合低功耗的要求。

PCI9054支持三種數據傳輸模式:PCI主控方式——允許本地的CPU訪問PCI總線上的存儲器和I/O接口;PCI從方式——允許PCI總線上的主設備訪問本地總線上的存儲器和I/O接口;DMA方式——由DMA控制器讀PCI存儲器內容到本地存儲器或將本地存儲器的內容寫到PCI存儲器。根據本裝置的要求可以采用PCI從方式與PCI總線數據傳輸。PCI9054需要1片EEPROM對其內部配置寄存器初始化。在EEPROM中需事先燒入對應寄存器的初始值,在PC啟動時,PCI9054很快地自動將EEPROM中值讀入對應寄存器,然后PC根據寄存器中的值為PCI9054分配中斷號、內存空間、I/0空間等系統資源。FPGA、PCI9054及PCI總線連接框圖如2。

圖2 PCI信號連接示意圖

1.2 FPGA電路的設計與實現

FPGA是整個系統的核心,控制數據采集、A/D轉換以及數據的傳輸[5]。

FPGA基本由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內嵌專用硬核等。FPGA繼承了ASIC的大規模、高精度、高可靠性的優點,而且可以反復的編程、擦除,開發工具智能化,功能強大,支持軟硬件協同設計,可以完成某些告訴復雜設計,提高系統的工作頻率與效能,同時克服了普通ASIC設計周期長、投資大、靈活性差的缺點,逐步成為復雜數字硬件電路設計的理想首選。

采集卡中FPGA功能:擁有內嵌鎖相環,利于FPGA內部的時鐘管理,提高系統的穩定性;擁有充足的RAM單元,使開辟較大的FIFO空間成為可能,從而延長FIFO間切換存儲過程中產生中斷的間隔時問。

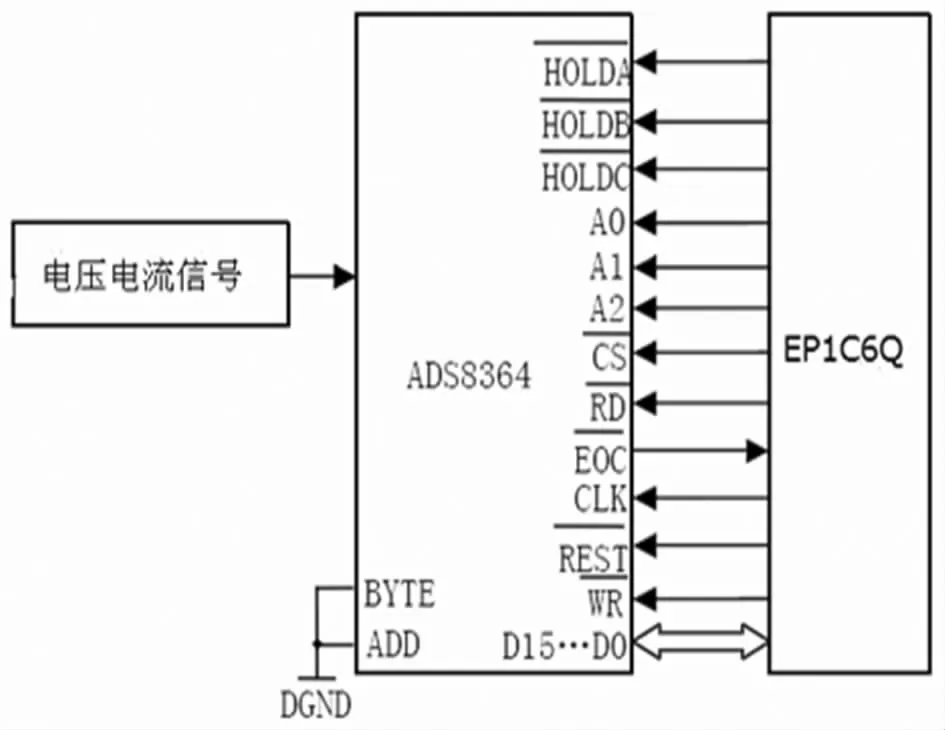

ADS8364是高速、低功耗、六通道同時采樣和轉換的十六位模數轉換器并行輸出。采用+5 V工作電壓,50 kHz時擁有80 dB共模抑制的全差分輸入通道,使其在噪聲較大的環境中明顯優于其他A/D芯片。ADS8364最大時鐘頻率可達5 MHz,可在20個時鐘周期內完成采樣/轉換。芯片還包括6個4 μs連續近似的模數轉換器,6個差分采樣放大器,帶REFIN和REFOUT引腳的內部+2.5 V參考電壓。以及高速并行接口,又有高達200 kbps的通道吞吐率。ADS8364擁有A、B、C三組6個模擬輸入,每個輸入端有1個ADCs可以成對同步工作,3個保持信號用來指定通道進行采樣、轉換或者保證幾個通道能同時進行采樣、轉換。

ADS8364與FPGA的接口連接如圖3所示。

圖3 ADS8364與FPGA連接示意圖

3 個保持信號(HOLDA,HOLDB,HOLDC)啟動指定通道的轉換。 當3個保持信號同時被選通時,啟動轉換,轉換完成后,把轉換結果將保存在6個寄存器中并產生EOC信號。A/D轉換精度為16位,最高位為符號位,數據輸出方式可以由BYTE,ADD與地址線A2、Al、A0的組合控制。

圖4 ADS8364的工作時序圖

ADS8364的工作時序圖見圖4,在ADS8364的開始轉化信號HOLDX保持至少20 ns的低電平時才能保證有效。當轉換結果被存人輸出寄存器后,引腳EOC的輸出將保持半個時鐘周期的低電平。FPGA為ADS8364提供CLK和HOLDX信號,當轉換完成后接收EOC信號,通過置RD和CS為低電平可使數據讀出到并行輸出總線。FPGA—EPlC6Q240C8內部邏輯電路的設計采用Altera 公司提供的 QuartusⅡ[6]軟件完成,采用嵌入IP核可以方便對ADS8364進行控制,用內部RAM組建一個FIFO存儲區,把采集的數據存儲在FIFO內,可以減少系統中斷,當FIFO內的數據達到一定數量后,把向系統申請中斷。

1.3 采集卡驅動開發

PCI數據采集卡設計的另一關鍵問題就是驅動程序的開發[7]。 Windows操作系統為了保證系統的安全性、穩定性和可移植性,對應用程序訪問硬件資源加以限制。因此,需要通過設備驅動程序實現應用程序對PCI硬件設備的訪問。在Windows 9x/NT中,設備驅動程序必須根據Windows驅動程序模型設計。設備驅動程序的關鍵是如何完成硬件操作,基本功能是完成設備的初始化、端口的讀寫操作、中斷的設置和響應及中斷的調用、以及對內存的直接讀寫。為簡化設備驅動程序的開發,選用了Jungo公司的WinDrive編寫工具。用WinDriver實現PCI設備驅動程序的步驟如下。

1)把制作完成的板卡插入PCI插槽,開機用WinDriver的Drive Wizard工具查找并選擇所要編寫驅動程序 PCI板卡。

2)用Drive Wizard的Generate.INF File產生INF文件,然后添加新硬件。

3)Drive Wizard會自動檢測計算機硬件資源,對PCI板卡上的配置寄存器、I/O空間、內存范圍、中斷、片內寄存器等進行設置。

4)在 Build菜單中選擇自動生成源代碼,Drive Wizard自動生成文件。

5)在Visual C++6.0中對上面生成的源代碼進行編譯、鏈接和運行。

6)編寫驅動的動態鏈接庫DLL文件。根據本系統的一些具體的功能要求,在Visual C++6.0中對源代碼進行功能添加和代碼調整,使得修改和重組后的驅動程序高效、安全地執行,生成動態鏈接庫DLL文件。手續開發的軟件通過DLL文件實現與數據采集卡的通信。

2 裝置系統軟件開發

系統軟件開發基于PC104計算機,采用PCM-3362,該PC104的 CPU采用 Intel Atom N450,頻率為1.66 GHz,支持DDR內存,最大內存2 GB,基本輸入輸出系統為AMI 16Mbit Flash bios,支持VGA1和8-bit LVDS,支持嵌入式軟件APIS和Utilities,擁有4個 USB2.0、2個RS-232和1個RS-422/485,采用5 V、12 V供電。

在該裝置中,采用Visual C++6.0作為軟件開發環境,通過調用驅動所提供的DLL文件對數據采集卡進行操作。 讀取采集卡采用中斷方式,當采集卡FPGA的FIFO中的數據達到一定數量后,會向PCI申請中斷,PC104接收到中斷信號后,響就中斷,把數據讀取到PC104的內存,并把數據做FFT變換,計算出電壓,電流的頻率,大小,相位等信息,利用這些信息做進一步處理,可計算無功功率,有功功率等。所計算的結果可以通過數據庫在本地系統存儲管理,方便歷史數據查詢,生成數據報表。在Visual C++可以方便利用socket把數據傳送至遠端服務器。

3 樣機實驗

試驗樣機采用圖1所示數據采集系統主電路。交流輸入電壓為110 kV,輸入電流為50 A。

系統采樣頻率為64kHz,使用快速傅里葉變換,計算出得到相電壓為63 522.20 V,電流為49.99 A,功率因數為0.99,得出有功功率為9430.64137kW,無功功率為1 339.692 38 kvar,數據采集系統顯示結果如圖5所示。

上述實驗結果證明了基于PC104和FPGA的數據采集系統的研究的可行性和可操作性,顯示結果精度比較高,計算比較精確。

4 結語

提出的基于PC104工控機和FPGA的數據采集系統的實現方法,實現了對風電場動態無功補償裝置的運行狀態的檢測,完成了電壓、電流信號的同步采樣和數據傳輸,能有效的對電能質量進行分析和無功補償裝置的運行狀態進行檢測,系統的網絡通信實現了對系統實時監控,同時試驗驗證了該數據采集系統算法和操作系統的穩定性和實用性,表明了該系統的研究和實現對電網電能質量的保證、電力系統的安全穩定和經濟運行具有重要作用和意義,項目研究的推廣具有重要的實用價值。

圖5 數據采集系統顯示結果