基于MPC8536的雷達嵌入式數據處理平臺設計*

張利平

(中國西南電子技術研究所,成都 610036)

0 引言

近年來,隨著大規模集成電路技術的成熟和發展,涌現出了許多功能強大的CPU處理器,POWERPC 即是其中的佼佼者,其產品線廣、性價比高、溫度范圍廣、集成度高以及功耗低等優點,正好滿足現代高性能嵌入式設備的要求。POWERPC 搭載LINUX 內核,也可以滿足絕大多數環境條件下的實時性要求。這里就以MPC8536為核心,構建了一個高性能的雷達通用數據處理平臺,在不改變系統硬件的條件下,僅對軟件進行更新,即可實現多功能性。基于通用處理平臺的設計還可以擴展到后續任務如SAR 數據傳輸、雷達組網、雷達信號處理、大型數據鏈等多種用途,具有廣闊的應用前景。

1 MPC8536 芯片介紹

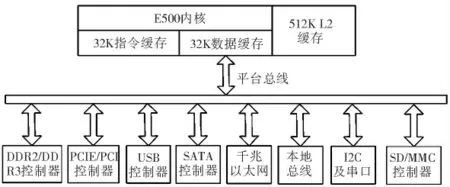

MPC8536 是Motorola 公司的高性能嵌入式微處理器芯片。該芯片內部集成了控制領域常用的外圍組件,特別適合通信和網絡設備的開發。MPC8536 采用E500 核結構,連同極高的網絡、USB、PCIE和SATA 設備集成度,為用戶提供了便捷的設計方案來建立高性能通用平臺。其內部結構如圖1所示。

由圖1 可知,MPC8536 已經跨越了純粹處理器的范疇,是一個高度集成的主控處理模塊,并且還具有以下特點:

(1)具有高性能E500 內核,CPU 頻率最高達1.5 GHz(2400MIPs);

(2)高度集成的內部控制器,如內存、PCIE、USB、SATA、以太網等,外圍電路設計簡單;

圖1 MPC8536的內部結構

(3)低功耗,10W的典型功耗遠優于X86 系列產品,且可以通過動態電源管理,控制靜態和動態功率模式下的功耗;

(4)可運行嵌入式操作系統(LINUX、VXWORKS),便于多任務管理和調度,實時性強。

2 平臺的硬件設計

系統的硬件部分主要包括MPC8536 微處理器模塊、DDR2 控制模塊、電源復位和時鐘模塊、存儲器模塊、千兆以太網模塊、PCI/PCIE 控制模塊、串行口控制模塊、CPLD 控制邏輯、USB 控制模塊、SATA 控制模塊。系統硬件設計框圖如圖2所示。

2.1 電源、時鐘和復位模塊

考慮到功耗太大不利于散熱進而影響系統穩定性,所以在芯片的選擇上全部采用低功耗芯片。平臺總共需要4 種電源,分別為1.1 V、1.2 V、2.5 V和3.3 V。其中MPC8536所需的電壓由TI的開關電源TPS54910和LT1963AEST-2.5 提供,VSC8224所需的1.2 V 由TPS54312 提供。所選的芯片均能滿足最大電流要求,且電源輸出效率較高。在實際應用中,編程人員還可以利用軟件啟動MPC8536的各種節能模式,平均系統功耗測試值小于15W。

系統時鐘電路分為3 部分,一是由33.33 MHz 晶振作為參考時鐘,通過一個時鐘分頻芯片,分別送給CPU、CPLD和PCI 設備;另外選取一個14.31818 MHz的晶振,輸入給ICS9FG108,分頻輸出PCIE 差分時鐘;最后采用一個24 MHz的時鐘,作為USB3300的輸入,控制USB 設備。

系統復位模塊采用的是MAXIM的電源監控芯片MAX16006。該芯片體積小、功耗低,可以通過配置同時監控8 種等級的電壓,完全滿足電壓監控要求。

2.2 以太網和USB 模塊

MPC8536 含有2個千兆以太網控制器,均可用作高速以太網接口。本系統采用VITESSE 公司的VSC8224芯片,加上脈沖變壓器,就可以構造1000M/100M 自適應以太網。由于VSC8224 帶一路光纖輸出,所以本系統提供了兩種網絡模式選擇。在某些對電磁干擾要求嚴格的環境條件下(如機載環境),采用光纖網絡通信,可以減少電磁干擾,保證整機電磁兼容。

MPC8536 自帶了2個USB 控制器,采用SMSC 公司的USB3300 加上LM3526M 電源管理芯片即可支持USB2.0 協議,實現外接鼠標、鍵盤、U 盤等接口。

圖2 嵌入式通用處理平臺系統框圖

2.3 存儲器模塊

MPC8536 內部含有7個存儲器控制單元,可以對各種存儲外設進行管理。通過對每個存儲器體的獨立寄存器BRx和ORx 進行編程控制,可以實現對NORFLASH、NANDFLASH 等外設的讀寫操作。本系統的存儲器模塊劃分為2個部分,即系統映像(NORFLASH)和應用程序(NANDFLASH)。由于嵌入式LINUX 操作系統一般體積較小,一片16M的NORFLASH 即可完成存儲功能,故選用SPANSION的16 位總線存儲芯片S29GL128N90TFIR1,用于完成U-BOOT和系統映像的存儲。分配片選信號CS0,通過編程BR0和OR0 設置地址映射為0xAF000000~0xB0000000。

NANDFLASH 用于存放應用程序以及其他需要存儲的大量數據。本系統采用三星的1G 容量芯片K9NBG08U5A,該芯片可以通過8 位的IO 口傳輸地址和數據,并且管腳兼容性好,可擴展存儲容量。分配片選信號CS1,通過編程BR1和OR1 設置地址映射為0xBFFFFFFF~0xFFFFFFFF。另外,通過MPC8536 自帶的MMC/SD 控制器和SATA 控制器,實現對SD 卡和SATA 接口的連接,作為大量實時數據的存儲(如雷達SAR 圖像)。

2.4 PCI/PCIE 模塊

作為通用處理平臺,必須要有高速總線和外部相連,MPC8536 自帶的PCI/PCIE 控制器正好滿足使用需求。方案設計時考慮將PCI 總線引到PMC 結構的接插件上,PCIE 總線引到XMC 結構的接插件上,方便進行功能擴展(如顯卡、數據處理等)。

2.5 CPLD和串口模塊

系統上電時,MPC8536 需要采樣復位配置字,以決定其啟動和工作方式。本系統通過CPLD 邏輯來完成上電復位配置字的采樣,可以方便地對CPU 進行配置,如設置工作頻率、配置總線和智能電源管理等。其自帶的串口模塊可以通過外接MAX3233E來實現RS232 接口,標準的I2C 總線也可以和低速外部設備互聯。

3 軟件設計

3.1 U-BOOT的移植

U-BOOT 是操作系統運行前執行的第一段程序,其作用是初始化硬件設備,建立內存空間映射表,為內核調用建立環境。系統采用最新的U-BOOT1.3.4,其中就包含了MPC8536的啟動代碼。根據硬件情況對源代碼作如下修改:

(1)Include/configs/MPC8536DS.h

#define CONFIG_BOARD_SYS_CLK 33330000//設置系統輸入時鐘為33MHz;

#define CONFIG_SYS_FLASH_BASE 0xAF000000//設置FLASH 起始地址;

#define CONFIG_MAX_FLASH_BANKS 1//設置FLASH 只劃分一個bank;

#undef CONFIG_EEPROM //無EEPROM 配置;

#define TSEC1_PHY_ADDR 1//分配第一個千兆網絡地址;

#define TSEC2_PHY_ADDR 0//分配第二個千兆網絡地址;

(2)Board/freescale/mpc8536ds/sdram.c

根據自身內存情況,在sdram_setup()函數中,添加對DDR2 控制寄存器時序的配置。

ddr->timing_cfg_3=0x00020000;

ddr->timing_cfg_1=0x4c47d432;

ddr->timing_cfg_2=0x331848ce;

將以上代碼修改完畢后,編譯生成U-BOOT.bin文件,通過BDI2000 寫入NORFLASH,重新加電后串口即可輸出啟動信息。啟動畫面如圖3所示。

3.2 操作系統的選擇

操作系統選用LINUX 搭載最新2.6 內核,完全可以滿足各種條件的應用要求。由于LINUX 系統具有安全性高、開放源代碼、實時性高等優點,已經在軍事和民用設備中得到廣泛應用。使用標準C/C++編程語言就可以便捷的開發雷達信息處理應用軟件,在ELDK4.2 環境下完成代碼的編寫、編譯和調試。采用C/C++語言編寫的代碼具有易讀、重用性高等優點,降低了開發難度,極大提升了開發效率。

3.3 操作系統的移植

2.6 內核已經支持MPC8536處理器和大部分外設,只需要根據平臺實際情況,將LINUX 源代碼中發布的MPC8536DS 開發板代碼進行修改與裁剪即可。內核移植的步驟如下:

(1)修改頂層Makefile 增加編譯選項

ARCH:=powerpc//選擇POWERPC 架構;

(2)源代碼的修改

由于系統硬件配置和FREESCALE的開發板有較大差異,所以需要對部分代碼進行修改。如關鍵的網絡地址的配置、時鐘頻率的配置等;

(3)內核的裁減

# make menuconfig //裁減掉內核中所有與本系統無關的模塊;

圖3 U-BOOT 啟動畫面

# make //編譯完成后生成內核映像uImage;

(4)文件系統的實現

系統在調試階段采用的是NFS 文件系統,通過tftp 進行網絡加載,實現階段是將RAMDISK 根文件系統寫入NORFLASH 進行自動加載。NFS的實現較為簡單,在ELDK4.2 交叉開發環境中,PPC_85XX 目錄下即提供了一個NFS 根文件系統。只要主機提供了NFS服務,目標機即可通過tftp 進行引導。RAMDISK根文件系統的制作流程如下:

*創建根文件系統文件夾;

*創建各種必要的系統文件;

*創建設備節點;

*建立與啟動相關的配置文件;

*安裝庫文件glibc;

*編譯busybox,安裝系統和應用軟件。

4 結果與分析

在調試過程中,發現U-BOOT的移植過程非常關鍵,應該根據硬件配置對源代碼進行修改。DDR2 寄存器需要根據實際PCB 布線來對時序進行微調,否則會導致系統不穩定或者根本無法啟動。PCB 布板時要注意電源與信號的分層隔離。PCIE 高速差分信號線均需要進行等長設計,盡量從頂層或底層走線并保證地層的包裹。

在實際應用中,本平臺主要完成的是雷達目標數據的解析工作。首先通過PCIE 總線接收多塊雷達信號處理板送出的目標信息,然后通過優化算法對數據進行分類解析,最后將需要的目標信息通過光纖網絡送到綜顯進行顯示。在本系統中,要求數據處理平臺能夠以較短的時間響應多塊信號處理板的中斷請求,并從大量目標數據中提取需要的目標信息,實時地傳送給綜顯進行顯示。

這里對系統中關鍵的中斷響應和內存拷貝兩項指標進行了測試,測試結果如表1。

表1 中斷響應和內存拷貝耗時

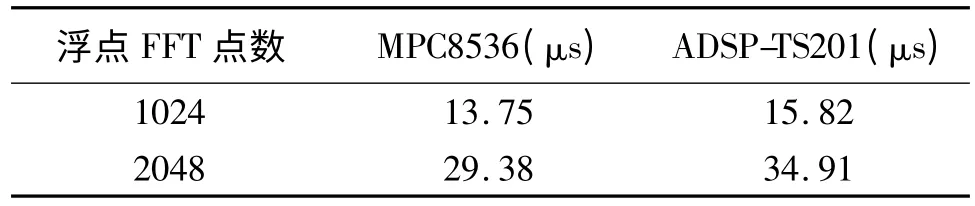

筆者將本平臺和曾使用的ADSP-TS201信號處理芯片進行對比測試時發現,當采用雷達信號處理常用的浮點復數FFT 運算作為測試算法時,MPC8536的運算性能還優于ADSP-TS201。運算速度對比見表2。

表2 MPC8536與ADSP-TS201 性能對比

可見,雖然功耗略高于ADSP-TS201,但是MPC8536搭載LINUX 操作系統,已經可以勝任專業DSP的信號處理工作。LINUX 操作系統下的中斷響應時間和內存讀寫速度也滿足絕大多數環境條件的應用。雷達通用數據處理平臺采用了LINUX 操作系統作任務管理的設計,應用靈活,開發調試方便,更能滿足現代雷達對多任務、多功能的實際需求。

5 結束語

隨著高性能通用處理器技術的飛速發展,基于POWERPC+LINUX 實時操作系統的雷達通用數據處理平臺將成為發展趨勢。本文介紹的即是其中一種應用于雷達設備中的通用數據處理平臺的設計方法。該平臺以Motorola 公司的高性能通信處理器MPC8536為核心,具有低成本、高性能、通用性好等優點。平臺支持的多種通用數據接口加上LINUX 系統的穩定性,將可以適應不同的應用環境。在測試中發現,MPC8536 已具備較高的信號處理能力,可以在以后的應用中嘗試進行簡單信號處理算法設計,通過操作系統這種多任務的管理方式對信號處理流程進行優化,達到提升整體系統性能的目的。此通用數據處理平臺已經成功應用于某型號雷達設備中。本平臺的研制成功,也為下一代的雷達系統設計提供了借鑒,具有較大參考價值。

[1]MPC8536E PowerQUICC III.Integrated Processor Reference Manual Rev.0 10/2008.

[2]MPC8536E PowerQUICC.III Bring-Up Guide Rev.0,02/2009.

[3]韋東山.嵌入式Linux 應用開發完全手冊[M].北京:人民郵電出版社,2009.

[4]Alessamdro Rubini.linux 設備驅動程序[M](第4 版).北京:中國電力出版社,2000.

[5]于明儉,陳向陽,方漢.Linux 程序設計權威指南[M].北京:機械工業出版社,2001.