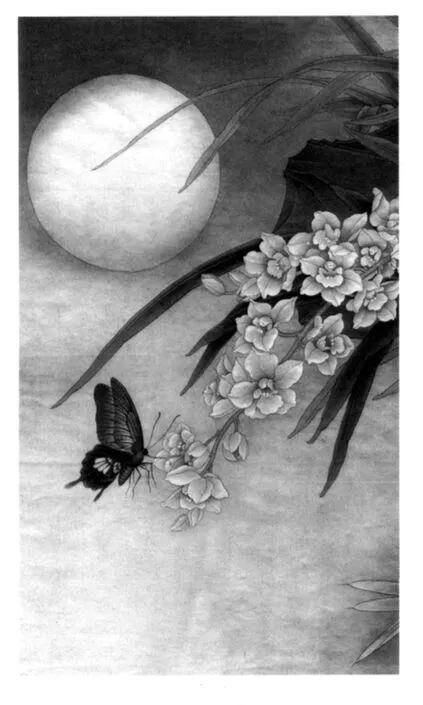

月光

2012-09-18 03:13:38侯志濤

當代礦工 2012年9期

□侯志濤

月光是母親的手

柔和的溫暖

滿足了我四季的山水

月光是父親的胸懷

我目光所觸及的地方

都是他的巍峨 偉岸 挺拔

月光是妻子的軟語

芬芳纏綿的呢喃

撫平我夜晚熟睡的安詳

月光是我的行走

舒緩生命之江河的碧浪

不放過任何一個矯情的細節

掛滿燦爛 孝敬爹娘

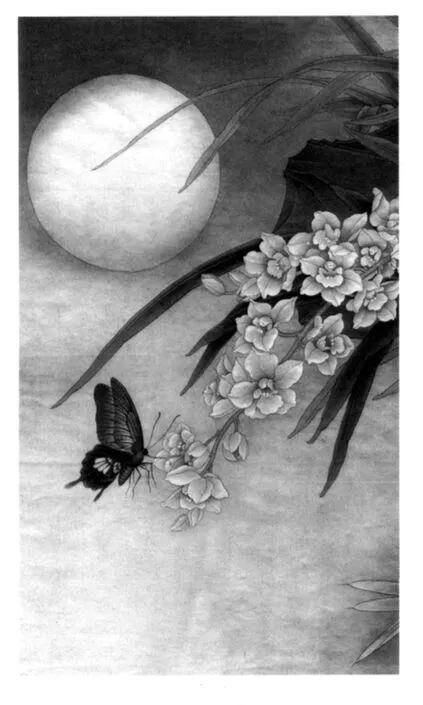

□侯志濤

月光是母親的手

柔和的溫暖

滿足了我四季的山水

月光是父親的胸懷

我目光所觸及的地方

都是他的巍峨 偉岸 挺拔

月光是妻子的軟語

芬芳纏綿的呢喃

撫平我夜晚熟睡的安詳

月光是我的行走

舒緩生命之江河的碧浪

不放過任何一個矯情的細節

掛滿燦爛 孝敬爹娘