高速信號完整性分析及設計在繼電保護裝置中的應用

甘云華,周華良,夏 雨,汪世平,鄒志楊

(國網電力科學研究院/南京南瑞集團公司,江蘇 南京 210003)

特高壓輸電技術以及智能電網技術的發展必然要求有先進的智能保護裝置來支撐[1-3]。近年來,在國家電網公司特高壓輸電項目的帶動下,繼電保護技術的發展不斷加速,繼電保護與現代控制理論、電力電子技術和遠程通信技術的結合日益密切[4-6],這些新的應用使得繼電保護設備的主CPU工作時鐘頻率不斷提高,外設接口不斷豐富,系統集成度和布線密度不斷加大。對硬件設計工程師來說,在繼電保護裝置研發過程中,傳統的電路設計方法不再適用,而僅僅依靠經驗來完成設計已不足以保證產品的合格率和可靠性,信號線的信號質量將成為產品硬件設計能否成功的關鍵。因此,要提高裝置研發的效率和產品的可靠性,進而提高系統硬件研發的一次成功率,必須在板級設計階段對系統關鍵信號進行詳細的分析與設計。文中所述的高速信號完整性分析及設計方法已在ARP-300系列高壓繼電保護裝置研發過程中實際使用,并在項目的高效快速研發中發揮了重要的作用。

1 裝置的系統組成

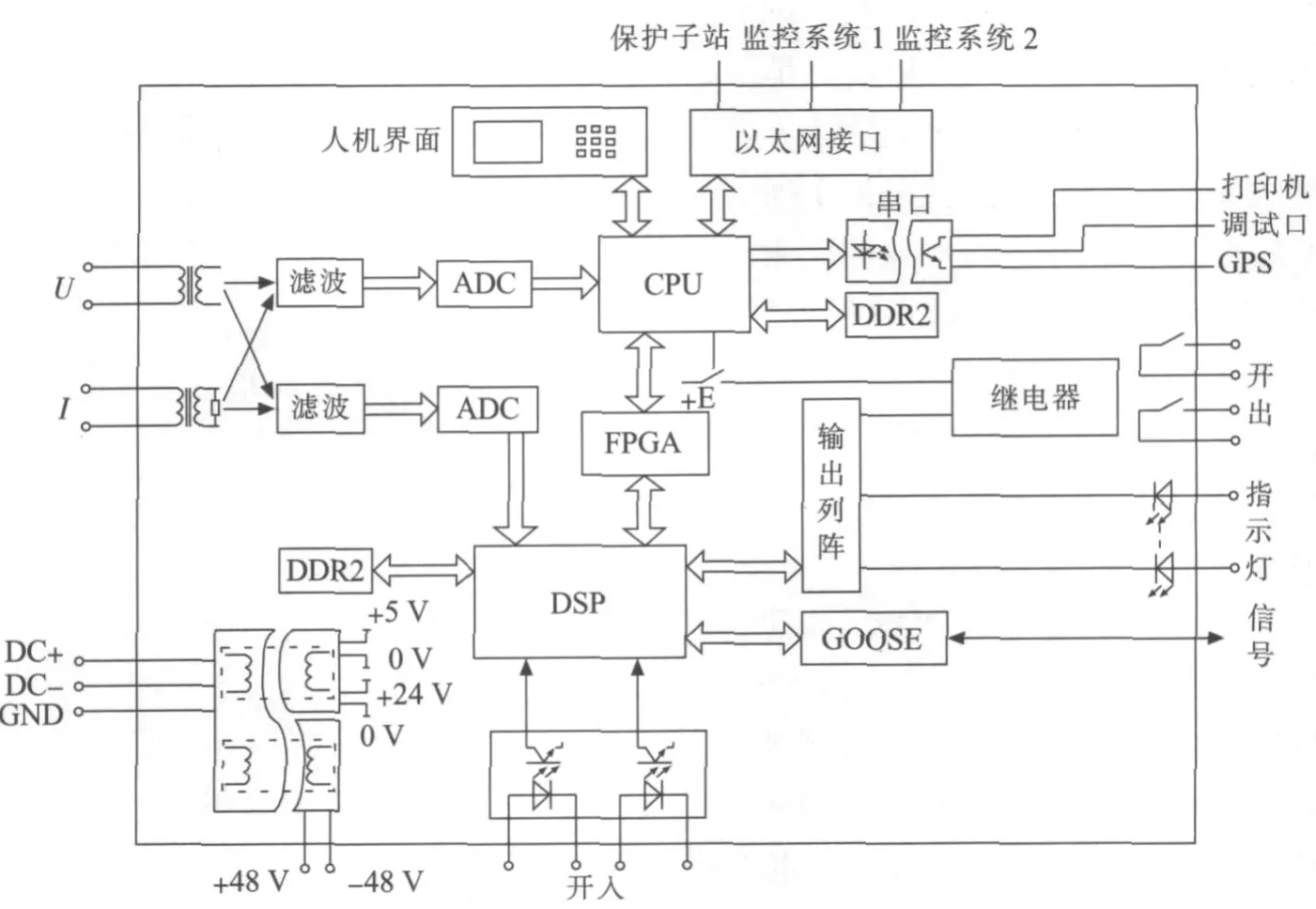

ARP-300系列高壓繼電保護裝置核心CPU板由高性能的CPU和數字信號處理器 (DSP)組成,CPU實現保護裝置的總啟動元件和人機界面及后臺通信功能,DSP完成所有的保護算法和邏輯功能。保護裝置采樣率為每周波24點,在每個采樣點對所有保護算法和邏輯進行并行實時計算,使得裝置具有很高的固有可靠性及安全性。系統采用的關鍵芯片及資源有:

(1)CPU芯片采用Freescale公司的帶協處理器功能的高性能PowerPC 【MPC8321】,系統主頻333 MHz,片外RAM使用 DDR2內存【DDR2時鐘為266 MHz】,同時支持3個獨立MAC的100 Mbps以太網接口;

(2)DSP芯片采用 ADI公司的高性能浮點DSP 【ADSP21469】,系統主頻 400 MHz,內置 5 MbitsSRAM,片外RAM使用DDR2內存【DDR2時鐘為 200 MHz】。

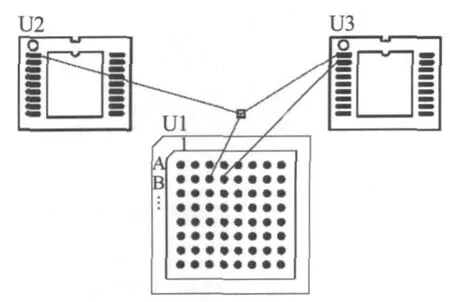

系統結構如圖1所,系統以CPU和DSP芯片為核心,兩處理器均有擴展外部DDR2高速存儲器,數據線和地址線的布線密度大,時鐘信號速率高;CPU擴展的3路以太網接口信號采用差分對走線,對線路阻抗控制有特殊要求。如果在硬件設計初期對這些問題處理不當,就會引發信號失真,導致多種錯誤的發生,造成系統達不到預期的設計效果甚至部分模塊無法正常工作。解決這一問題比較有效的方法就是對系統進行信號完整性設計。

2 信號完整性設計

2.1 信號完整性

信號完整性是指信號線上的信號質量。通常,數字邏輯電路的頻率達到或者超過50 MHz,而且工作在這個頻率之上的電路占整個系統的1/3以上,就可以稱其為高速電路[7]。在高速電路設計中,信號完整性對系統的影響主要體現在:時序裕量是系統在高低溫下穩定運行的保障之一;電平裕量對于電路的電磁干擾的抗擾度有保障;減小信號回路面積大大削弱了信號環路的天線效應,一方面提高了電路對高頻電磁場的抗擾度,同時也降低了電路對外發射的強度。影響信號完整性的因素主要包括反射、串擾、延時等。在高速電路設計中,隨著時鐘頻率提高,信號邊沿變陡,信號在器件之間的同步時間就會縮短,要滿足所有門延時必須在越來越短的時間預算中實現,稍有不慎都可能導致器件時序或模塊功能的混亂。

圖1 系統結構

產生上述信號完整性問題的主要原因包括信號走線過長、總線結構走線之間不等長、信號走線安全間距不夠以及信號傳輸路徑上的阻抗不匹配等。通過對系統進行信號完整性分析與仿真,可以對相鄰平行信號線進行耦合分析,確定信號線之間的安全預期間距或平行布線長度,減小串擾對信號造成的危害。另外通過對不同匹配電阻的掃描分析對比,可以尋求信號傳輸路徑上阻抗端接匹配的最優化,抑制反射現象的發生。阻抗匹配是解決大部分信號完整性問題的重要手段,所以有必要介紹一下傳輸線的特征阻抗。

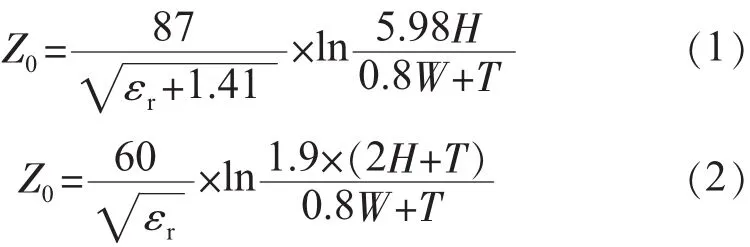

2.2 特征阻抗

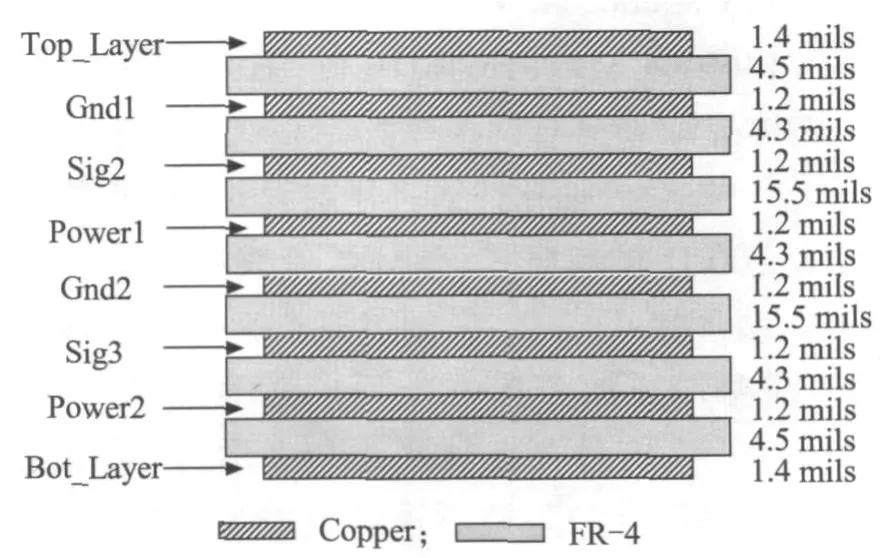

高速電路設計中,信號走線的分布參數效應使其寄生電感和寄生電容不能被忽略,必須將信號走線當作傳輸線來處理。特征阻抗是傳輸線的一個重要特性[8]。傳輸線主要有2種形式:微帶線和帶狀線,其中微帶線分為表面微帶線和嵌入式微帶線,帶狀線分為對稱帶狀線和不對稱帶狀線。典型的表面微帶線和對稱帶狀線的特征阻抗Z0的近似計算公式分別如式(1)和(2)所示[9]:

式中:εr為絕緣介質介電常數;H為導線至參考平面之間的介質厚度;W為導線寬度;T為導線厚度。在選定基材后,εr變化很小,板厚和層壓工藝決定H變化,T由銅箔厚度和加工工藝確定。由此可見,控制調整線寬是設計人員控制Z0最直接和最有效的方法。

傳輸線的Z0與印制板層疊設計密切相關。本文設計的CPU板對特征阻抗參數進行了理論計算,同時結合PCB加工廠家的工藝加工能力,確定采用8層結構板,并采用了如圖2所示的疊層設計。

圖2 PCB疊層結構

該系統中CPU主頻為333 MHz,DSP芯片主頻為400 MHz,片外RAM使用DDR2內存,DDR2時鐘頻率達到200 MHz及以上,時鐘信號的質量直接影響整個系統的性能,因此時鐘信號走線長度的控制、與相鄰信號之間的干擾以及信號傳輸路徑上的阻抗匹配是系統分析設計的重點;同時DDR2的地址線和數據線由于時序要求嚴格,需要控制網絡之間的安全間距和數據組間等長,但由于系統布線密度較大,需綜合考慮空間和信號完整性問題。另外系統擴展有3個獨立MAC的100 Mbps以太網接口,采用差分對走線方式,對其進行阻抗控制以及等長匹配也是系統設計的關鍵。如對上述問題處理不當,容易造成信號傳輸路徑上阻抗失配,引起反射、不同網絡之間相互干擾和電路誤觸發或時序混亂,降低信號傳輸的質量,影響系統性能,導致系統無法正常工作。該系統中最為關鍵的信號處理點就是以上所述CPU和DSP的外部存儲器DDR2以及高速以太網差分對的處理,下面就針對這2個關鍵點做具體的分析和設計。

3 關鍵信號分析

3.1 DDR2時鐘信號線

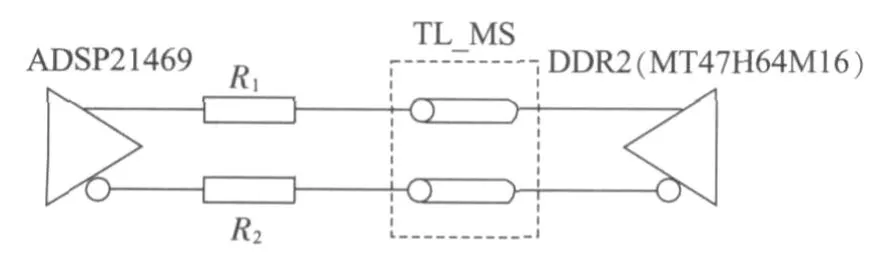

系統中CPU和DSP均有擴展外部DDR2高速存儲器,由于兩者具有一定的共性,文中僅以DSP(ADSP21469)和 DDR2(MT47H64M16)連接為例進行分析。MT47H64M16芯片時鐘信號由ADSP21469提供,由于信號速率較高,考慮表層布線,并采用抗干擾能力較強的差分對形式走線,信號拓撲結構如圖3所示,TL_MS表示差分傳輸線,微帶線結構,R1和R2為源端匹配電阻。

圖3 時鐘信號拓撲圖

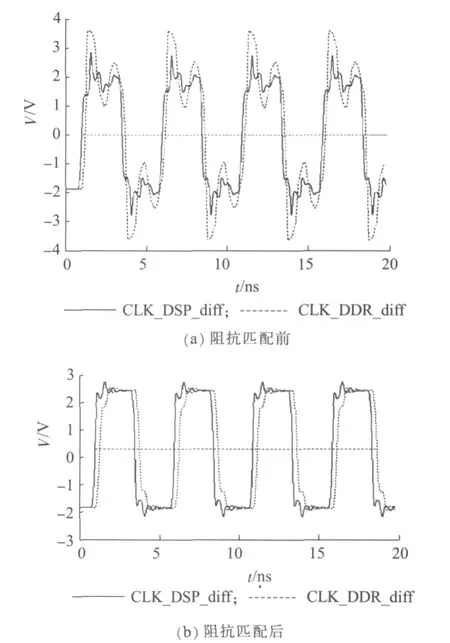

采用Cadence軟件信號完整性分析模塊,調入ADSP21469和MT47H64M16的IBIS行為級模型后,整體提取差分對網絡拓撲結構在SigXplorer環境下進行仿真。采用圖2的疊層設計,參考差分線阻抗為100 Ω控制要求,差分微帶線結構中線寬為5.5 mil,線間距11 mil。采用點對點無匹配連接的情況下,在源端施加200 MHz周期激勵,仿真波形如圖4(a)所示,信號存在較嚴重的變形,這是由于信號在傳輸路徑上的阻抗不連續點發生反射造成的,因此必須考慮在電路設計過程中加入匹配電阻。設計中采用在源端串接電阻的匹配方式,施加相同的激勵源后仿真波形如圖4(b)所示,信號傳輸延時227 ps,傳輸速度約為0.56倍光速。由仿真結果可知串接匹配電阻后,信號得到明顯改善。通過使用軟件sweep功能對不同匹配電阻進行掃描優化,可以確定電路中的較優匹配阻值,該仿真案例中匹配電阻在40 Ω左右,信號波形達到設計要求,實際電路中考慮電阻標稱值,采用33 Ω匹配電阻。

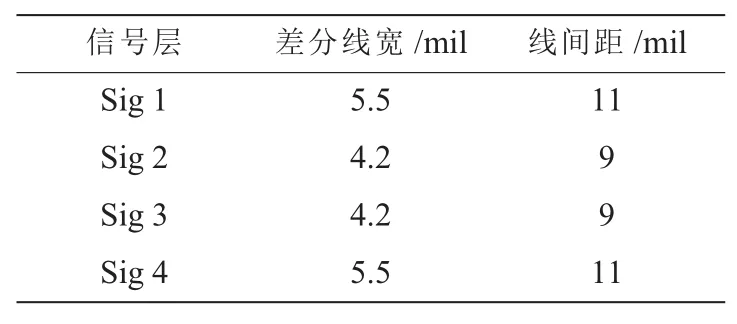

3.2 以太網差分信號線

系統主要采用以太網接口與外部實現通信,以太網接口芯片為Broadcom公司的BCM5241,信號主要以差分對形式進行傳輸。差分線作為傳輸高速信號的有效載體,對其進行阻抗控制和匹配非常關鍵。根據系統差分線阻抗為100 Ω的控制要求,參照文中2.2節的疊層設計,計算得各信號層差分信號布線要求,如表1所示。

圖4 時鐘信號波形

表1 差分信號布線規則

差分線阻抗控制的一致性可以保證信號在傳輸過程中不易發生失真變形,但僅通過設置合適的布線寬度和線間距還不足以保證阻抗的連續性,從3.1節的分析中得知,必須在傳輸路徑上對信號進行正確的端接匹配,以達到抑制或消除信號反射的目的。此外差分對的正負兩端應盡量做到等長以抑制共模干擾。綜合器件指導手冊、阻抗設計要求及經驗規則,對以太網接口差分的確認采用如下布線規則:(1)線寬/線間距為5.5 mil/11 mil(PCB板外層);(2)差分對兩根走線等長誤差為<25 mil。

按上述規則指導完成布線后,還可能存在一些信號完整性問題,如端接電阻阻值匹配不夠理想,信號之間的串擾等。通過布線后仿真可對設計進行優化,做到使整個設計的信號完整性問題減到最少。

3.3 DDR2數據與地址總線

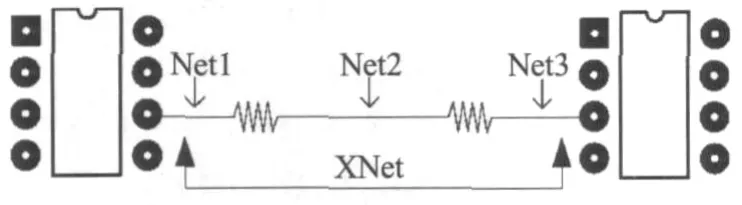

由以上分析可知,DDR2的數據和地址總線布線同樣需要進行阻抗控制和匹配,除此以外,由于CPU和DSP對DDR2進行讀寫操作時,對各信號的時序要求比較嚴格,因此在設計中對不同信號的走線長度要進行控制。通常總線各位數據線需進行等長匹配設置,而為了避免信號反射等問題進行的端接匹配會使高速總線被電阻等無源器件分成好幾段Net,這時等長控制最原始的做法就是對每段進行控制,比較繁瑣。Cadence公司Allegro軟件中解決這個問題的辦法就是借助Xnet這一概念,即把連續的幾段由無源器件連接的Net合稱為一段Xnet,如圖5所示。

圖5 Xnet示意圖

通過賦予無源器件ESpice模型,Net1、Net2和Net3會自動合成為1個Xnet,這樣在軟件的規則約束管理器中設置等長規則時只需對整個Xnet設置規則,無需對每一小段進行等長匹配處理。

總線的等長匹配有2種,分別為全局等長和局部等長。如圖6所示。

圖6 等長示意圖

圖中U1.B3到U3.1和U1.B4到U3.2的走線設置等長屬于全局等長,一般數據總線或地址總線的不同位之間的走線等長屬于這種形式。另外圖6中T型連接點到U2.1和U3.1的走線設置等長屬于局部等長,對于多片存儲器共享數據和地址總線時屬于這種形式,這種等長的設置和網絡的拓撲結構有關。為避免傳輸線效應,減小信號組之間的串擾,走線應盡可能短,同時還要兼顧各信號之間的時序要求。綜合考慮布線空間和信號質量,該系統中數據和地址總線布線要求如下:

(1)數據和地址線單線總長度控制在2000 mil以內;

(2)內層線寬 4.6 mil,外層線寬 6.8 mil,總線組內部間距>6 mil,總線組與其他走線之間的間距為>20 mil;

(3)總線之間等長誤差<20 mil。

規則設置以后,對于等長的控制可以使用Allegro軟件的蛇形走線工具,根據實時顯示的走線長度確保總線等長匹配的精確性。布線完成后同樣需要進行后仿真,通過分析仿真結果對一些規則進行優化,以使系統滿足設計要求。

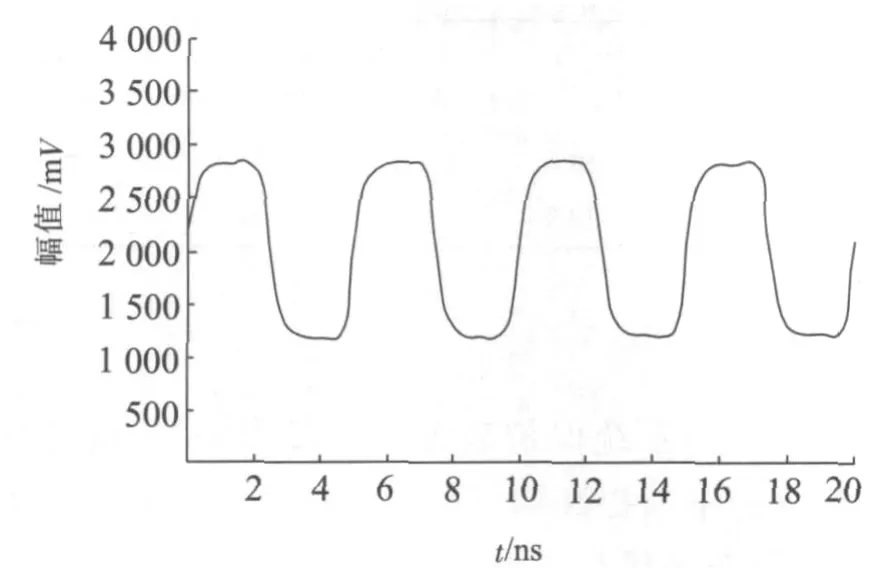

4 實際電路測試

根據上述的設計規則制作了CPU板的印制電路板和樣機,并進行了實際測試。對單板通過Agilent Technologies公司的MSO7104A混合信號示波器進行測試,測得與ADSP21469相連的MT47H64M16時鐘信號波形如圖7所示。信號波形無振蕩,上升時間為0.66 ns左右,滿足CPU及DDR2的系統工作要求,CPU和DSP的DDR2內存均能正常穩定工作,進一步驗證了設計前信號完整性分析與仿真的正確性和有效性。

圖7 時鐘信號波形

同時,基于此CPU板的保護整裝置在國網電力科學研究院進行了多項試驗,均按照最高級指標要求進行,主要針對性的測試項目包括:

(1)高溫試驗, 按 GB/T 2423.2—2001(IEC 60068-2-2:1974)標準,+55 ℃下 16 h;

(2)低溫試驗, 按 GB/T 2423.1—2001(IEC 60068-2-1:1990)標準,-25 ℃下 16 h;

(3)快速瞬變干擾試驗,按GB/T 14598.10—2007(IEC 60255-22-4)標準 IV 級,電源、開入開出、交流:4kV,2.5 kHz,5/50 ns;通信端子:2kV,5 kHz,5/50 ns;

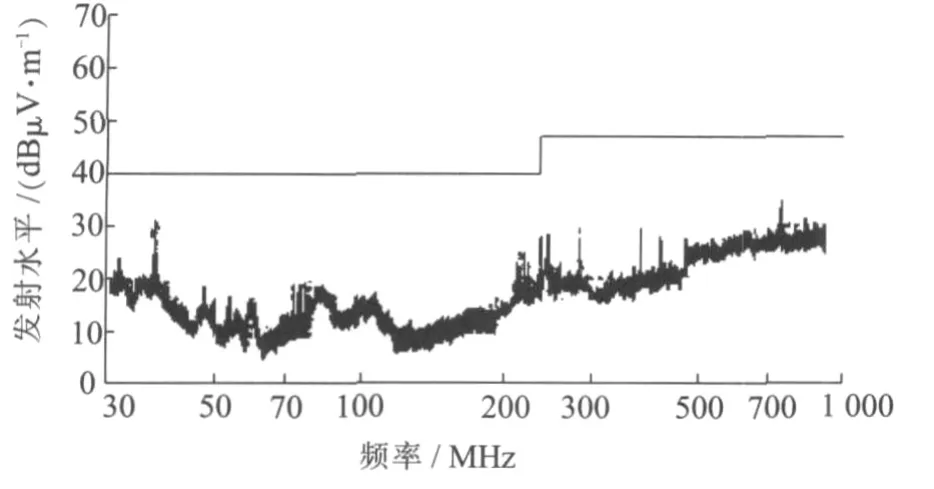

(4)電磁發射試驗,按GB/T 14598.16—2002(GB 9254-2008、CISPR 22:2006)標準,B 級輻射騷擾限值,30~230 MHz準峰值 30dB(μV/m),230~1000 MHz準峰值 37dB(μV/m);

(5)靜電放電試驗,按GB/T14598.14—1998(IEC60255-22-2)標準 IV 級,接觸放電:8kV,空氣放電:15kV。

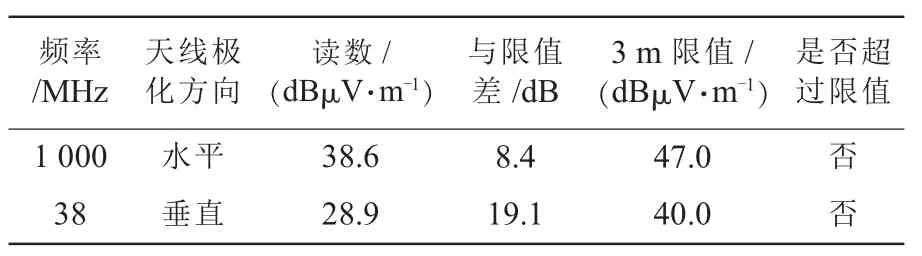

在整個試驗測試過程中,CPU和DSP的DDR2內存均可靠工作,以太網口可靠通信,裝置運行穩定。此外,裝置完成的電磁發射試驗,按GB/T 14598.16—2002 (GB 9254—2008、CISPR 22:2006)B級輻射騷擾限值進行,測試曲線如圖8所示,結果如表2所示。該指標滿足國外工程需求,進一步證明了在系統硬件設計階段進行信號完整性分析與設計的正確性和可行性。

圖8 電磁發射測試曲線

表2 電磁發射測試結果

5 結束語

針對電力系統保護裝置發展過程中,系統芯片工作頻率的不斷提高和信號邊沿的不斷縮短等帶來的問題,以新一代高壓繼電保護ARP-300系列裝置硬件設計為平臺,提出在硬件板級設計階段引入高速信號完整性分析與設計方法,通過信號完整性分析指導器件布局、布線規則設置和阻抗匹配等。實際板卡的信號完整性測試結果表明,系統反射、串擾等信號完整性問題得到了有效控制,證明文中應用的高速信號完整性分析與設計方法正確,設計規則合理有效;同時對含有該CPU板的整裝置進行了電磁兼容實驗,系統可靠工作,進一步驗證了該設計方法的正確性和可靠性。最后需要說明的是,高速信號完整性分析內容較深,本文僅對繼電保護裝置硬件研發過程中的信號完整性問題做了初步的探討,對信號完整性分析與設計還有很多新方法及技巧有待今后進一步深入研究。

[1]陳德樹,唐 萃,尹項根,等.特高壓交流輸電繼電保護及相關問題[J].繼電器,2007,35(5):1-3.

[2]劉成君,張愷凱.數字化變電站及其對繼電保護的影響[J].電工電氣,2010(4):4-7.

[3]邵寶珠,王優胤,宋 丹.智能電網對繼電保護發展的影響[J].東北電力技術,2010(2):11-13.

[4]徐 政,盧 強.電力電子技術在電力系統中的應用[J].電工技術學報,2004,19(8):23-27.

[5]李崢峰,楊曙年,喻道遠,等.繼電保護中光纖通信技術應用[J].電力自動化設備,2007,27(2):75-79.

[6]劉 青,王增平,鄭振華.基于MAS的含FACTS元件輸電線路自適應協調配合方案的研究[J].華北電力大學學報,2009,36(1):15-19.

[7]周潤景,袁偉亭.Cadence高速電路板設計與仿真[M].北京:電子工業出版社,2006.

[8]BOGATIN E.信號完整性分析[M].李玉山,李麗平,等譯.北京:電子工業出版社,2005.

[9]IPC-2251,Design Guide for the Packaging of High Speed Electronic Circuits[S].2003.