基于FPGA的多通道直流電機控制器設計

易龍龍,張復春,王美玲,郝雁中

(中國人民解放軍空軍航空大學 航空理論系,吉林 長春 130022)

機電一體化系統中常需要產生多通道PWM信號以完成對多臺電機進行協調控制,而傳統控制系統仍然采用單片機內部的定時/計數器來產生所需要的PWM信號,但由于定時/計數器及IO端口數量的限制,單個單片機控制器常不能滿足多通道電機并行控制的要求[1-3]。而FPGA內部程序并行運行,不同邏輯任務可同時執行,使其工作更有效率,且其具有豐富的邏輯資源和I/O引腳資源。文中采用Altera公司Cyclone II系列的EP2C8Q208芯片,采用模塊化的設計方法,以四臺無刷直流電機為控制對象,完成了多通道的直流電機控制器的設計,有效地縮小了設計規模,節約了設計成本。

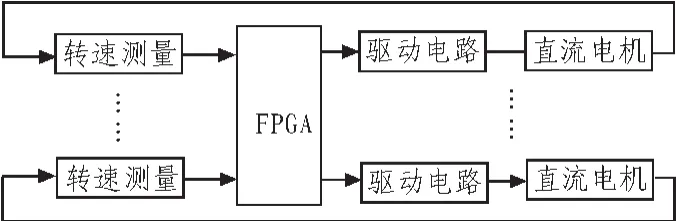

1 系統整體設計

本系統采用自頂向下的設計思路,將系統主要分為以下模塊:FPGA控制模塊、電機驅動模塊,轉速檢測模塊[4]。如圖1所示。本系統以FPGA為控制核心,通過程序設定控制電機速度的PWM信號的占空比,由FPGA的I/O口輸出給直流電機驅動電路以完成對直流電機的驅動。電機轉速測量由霍爾傳感器完成,反饋給FPGA計數模塊,通過計數結果以決策電機控制狀態。文中將著重介紹FPGA控制模塊及各部分的功能設計與實現方法。

圖1 系統結構框圖Fig.1 Structure of the system

設計中將FPGA控制模塊又分為分頻模塊,計數模塊,并行控制模塊,PWM生成模塊4部分。分頻模塊把外部高頻時鐘信號降低為系統所需的標準頻率。計數模塊對霍爾傳感器輸入脈沖進行計數以完成對電機轉速的測量。并行控制模塊通過計數模塊的計數結果決策PWM信號的占空比。PWM生成模塊通過并行控制模塊輸出的占空比信號生成PWM波形。如圖2所示。

圖2 FPGA內部模塊框圖Fig.2 Module chart in FPGA

2 各功能模塊設計

2.1 電機驅動模塊

本設計中直流電機驅動模中采用ST公司生產的一種高電壓、大電流電機驅動芯片L298P,內含兩個H橋的高電壓大電流全橋式驅動器,采用標準TTL邏輯電平信號控制。由L298P構成的脈寬調速電路如圖3所示。在圖中,L298P可驅動兩個直流電機,可以分別控制它們的轉速、轉向、運轉與停止。圖中ENA、ENB分別控制兩個電機的運轉與停止,當端口為高電平時電機旋轉,加低電平時電機停止旋轉;由In1,In2端送入脈寬調制信號,通過改變信號的脈寬達到調速和換向的目的。M1_+,M1_-和M2_+,M2_-分別是兩個直流電機的電壓輸入端[5]。

圖3 LMD18200電機驅動電路Fig.3 Motor drive circuit based on LMD18200

2.2 分頻模塊

盡管可以設計中采用鎖相環來完成分頻器的設計,但為了節省邏輯資源,降低芯片功耗,在對于時鐘要求不太嚴格的設計中,可自主設計進行時鐘分頻。本設計中采用常用的計數分頻,只改變分頻系數就可實現隨意分頻。其設計過程簡單,且消耗系統資源少。在本設計中輸入時鐘CLK_25M為25 MHz,為了設計方便,選擇分頻系數設為16。通過對模塊輸出進行仿真,測量時鐘輸出頻率為1.562 5 MHz,周期為640 ns滿足設計要求。

2.3 計數模塊

本設計中采用霍爾傳感器對直流電機進行轉速測量,電機每轉一圈,霍爾傳感器就輸出一個高脈沖。測速模塊其功能主要是計數,并且將所得到的數字應予鎖存輸出。根據單位周期內霍爾傳感器輸出的高脈沖數就可以估算出電機的轉速。在本設計中設定每500 ms的周期內對計數結果進行一次輸出并清零。根據其具體邏輯功能將利用Verilog HDL語言實現,其邏輯框圖如圖4所示[6]。

圖4 測速模塊邏輯圖Fig.4 Logic chart of speed measure module

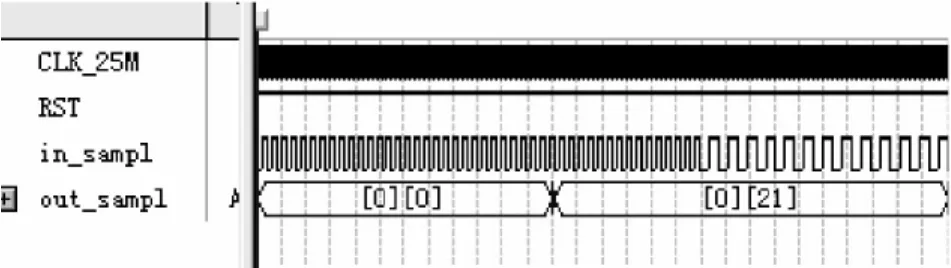

測速模塊的邏輯仿真結果如圖5所示,分頻后系統時鐘頻率為1.562 5 MHz,系統復位后,開始對被測霍爾傳感器輸入進行計數測量,其結果為20。已經被測輸入信號周期為50 ms,則頻率為20,表明設計完全正確。

2.4 并行控制模塊

圖5 測速模塊仿真圖Fig.5 Simulation chart of speed measure module

并行控制模塊部分是電機控制的核心部分,主要負責根據預定設置和計數模塊的計數結果,按照設計目的,完成對PWM占空比的控制。由于要實現各通道電機之間互不干擾,則要求各并行控制模塊與測速模塊和PWM生成模塊一一對應,以實現各通道并行獨立控制。

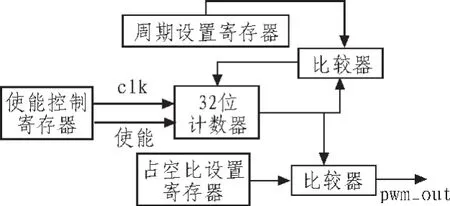

2.5PWM生成模塊

產生PWM原理:FPGA中的基準計數器用來產生類似模擬電路的三角波基準,是一個最小計數值為0,最大計數值為周期寄存器中保存的數值。PWM的任務邏輯由輸入時鐘CLK,輸出信號pwm_out,使能位,32位計數器以及一個32位比較器組成。輸入時鐘作為32位計數器的時鐘信號,32位計數器的當前值與占空比設定寄存器中的值經過比較器后來決定pwm_out的輸出為高或為低。當前計數器中的值小于或等于占空比寄存器中的值時,pwm_out輸出低電平,否則輸出高電平。PWM的周期設定寄存器來設置pwm_out的信號周期,當前計數器的值等于周期設定寄存器中設定的值時產生一個復位信號來清除計數器中的值。使能控制寄存器能使時鐘信號有效或無效,從而控制計數器是否工作,進而控制pwm_out是否保持當前狀態不變。PWM生成模塊邏輯圖如圖6所示。

圖6 PWM生成邏輯圖Fig.6 Logic chart of generate PWM

本系統共設計了4條PWM信號輸出通道,每條通道的仿真波形如圖8所示。通過仿真發現,當改變占空比寄存器data中的數據時,模塊輸出信號波形的占空比也隨之發現變化,符合脈寬調制的要求。在本設計中采用時鐘同步信號,只有當一個完整的PWM波輸出時,才能接收data下一個數據,有效避免輸出信號發生混亂,使輸出信號具有良好的可預見性。

3 實驗結果與分析

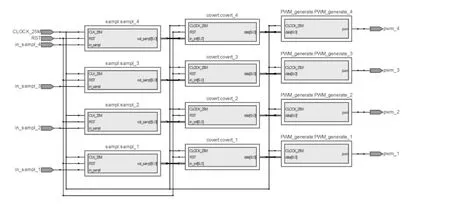

本實驗中設計了四通道PWM以完成對4個直流電機控制。利用Quartus II自帶的仿真工具對系統進行時序仿真,如圖7所示。由圖可以看出各個通道的PWM波的占空比與每個通道的霍爾傳感器輸入信號有關,各通道之間互不影響。

圖7 多通道PWM時序波形圖Fig.7 Timing wave of multi-channel PWM

對系統綜合之后,通過觀察RTL邏輯視圖,如圖8所示,可以看出,各個通道是并行的,互不影響,符合設計要求。同時,也不難看出,系統結構較為簡單,具有較強的拓展能力,能夠方便地實現多通道電機的并行控制。

圖8 系統RTL邏輯視圖Fig.8 RTL logic view of the system

隨著PWM設計通道數量的增多,所需要的片內邏輯資源也就越多,即設計PWM通道數目在一定程度上取決于FPGA片機邏輯資源的大小。

4 結束語

本設計充分利用了FPGA豐富的I/O引腳資源及程序并行運行的特點,代替了普通的單片機實現了多通道電機的控制,克服了傳統PWM控制器通道少的不足,同時有效地減少了電路規模。本系統采用Quartus II自帶的仿真工具進行仿真,驗證了設計的可行性。雖然本設計在功能上還比較單一,在由于其具有良好拓展性,可根據實現設計要求,能夠方便的對系統進行升級和維護。

[1]劉小威,翟超,顏芳.基于FPGA的LAMOST多電機控制驅動系統[J].機械與電子,2008(6):17-19.

LIU Xiao-wei,ZHAI Chao,YAN Fang.The controlling and driving system of multiple motors based on FPGA in LAMOST[J].Machinery&Electronics,2008(6):17-19.

[2]韋鯤,任軍軍,張仲超.應用于無刷直流電機的新PWM調制方式[J].電氣傳動,2005,35(2):37-40.

WEI Kun,REN Jun-jun,ZHANG Zhong-chao.The research on novel PWM method in BLDC motor[J].Electric Drive,2005,35(2):37-40.

[3]孫偉,黃大慶,閆亞輝.基于FPGA的多通道PWM控制器設計[J].江蘇科技學院學報,2009,22(4):72-76.

SUN Wei,HUANG Da-qing,YAN Ya-hui.Design of multichannel PWM controller based on FPGA[J].Journal of Suzhou University of Science and Technology,2009,22(4):72-76.

[4]劉衛國,李榕,楊浩東,等.基于單DSP的多電機控制系統[J].電氣傳動,2005,35(8):25-28.

LIU Wei-guo,LIRong,YANG Hao-dong,etal.Control system of multiple motors based on a single DSP controller[J].Electric Drive,2005,35(8):25-28.

[5]宋健.基于L298的直流電動機PWM調速器[J].濰坊學院學報,2004,2(2):87-89.

SONG Jian.PWM speed regulator for DC motor based on FPGA[J].Journal of Weifang University,2004,2(2):87-89.

[6]常曉明,李媛媛.Verilog-HDL工程實踐入門[M].北京:北京航空航天大學出版社,2005.