防御差分功耗分析攻擊技術研究

汪鵬君 張躍軍 張學龍

(寧波大學電路與系統研究所 寧波 315211)

1 引言

隨著超大規模集成電路(Very Large Scale Integration, VLSI)和計算機技術的發展,信息安全已從傳統的政治、軍事、外交、情報等重要領域全面推廣到社會日常生活中。由于信息安全技術確保了各種關鍵信息的安全保存和傳輸,因此高性能智能卡在我國已經非常普及,如銀行卡、身份證、交通卡、手機卡等,為人們生活帶來了便利。現代電子設備由集成電路構成,信息安全技術也依賴于相應的集成電路(如密碼芯片)作為硬件載體。密碼芯片是信息安全的保障,它有效地實現用戶的身份驗證、密鑰存儲等關鍵信息的保護。隨著集成電路各種性能要求的提高,其單片集成度按摩爾規律不斷增長,高性能密碼芯片的 VLSI設計技術已經成為信息化社會的迫切需求。信息安全的攻擊和防御始終是一對“矛”和“盾”,一方為了推廣智能卡的使用,必須確保信息的安全,有效防御外界的攻擊,筑起堅固的“盾”以防信息的泄漏,可稱之為信息安全的“防御”;而另一方則不擇手段,磨礪鋒利的“矛”以攻克對方的“盾”,盜取其重要信息,可稱之為信息安全的“攻擊”,就好像計算機病毒軟件和殺病毒軟件一樣,這對“矛盾”在不斷進化、升級。因此對信息安全的攻擊和防御方法的研究越來越受到學者們的關注。

傳統攻擊使用數學分析的方法尋找加密算法的漏洞,要求攻擊者必須在密碼分析和加密算法方面有相當高的造詣,而新型攻擊技術除此之外還可通過其他途徑盜取信息。眾所周知,目前普遍采用將保密信息通過在加密器件上執行密碼算法的策略,達到保護信息安全的目的,然而,在執行密碼算法過程中物理器件總是要泄漏各種與密碼系統本身相關的信息,譬如運行時間、能量消耗、電磁輻射等等。攻擊者利用這些邊際信息攻擊加密器件就可獲得密鑰,這一過程稱為旁道攻擊[1](Side Channel Attack, SCA)。旁道攻擊方法分為時間分析[2]、功耗分析[3]和電磁輻射分析[4]3類。在旁道信息中,由于功耗的可測試性最強、測試功耗的工具最簡單、功耗曲線也最適合分析,使得功耗分析攻擊在實際攻擊中應用最多。功耗分析就是依賴于加密硬件在加密過程中電路功耗與其處理的數據及進行的操作關聯,通過監測硬件在加密過程中的功耗曲線,利用統計方法和攻擊者的經驗對收集到的信息進行分析,從而獲得與加密信息相關的數據。在諸多功耗分析旁道攻擊方案中,差分功耗分析[3](Differential Power Analysis, DPA)攻擊技術被證明是最有效率并且是最容易實現的一種,由于其易于操作且非常有效,對密碼模塊的安全構成重大威脅。

國際發卡組織VISA非常重視DPA攻擊對密碼芯片的危害,以至于該組織將芯片信用卡的安全需求提升為3個技術等級,而在安全性級別最高的技術等級中明確提出至少包含 1個以上對策來防止DPA等信息泄露攻擊技術,可見DPA攻擊具有極大的殺傷力。防止DPA攻擊對實際應用中的加密器件安全性造成威脅,開發具有防御 DPA攻擊的VLSI密碼芯片,具有重大理論價值和現實意義。

2 DPA攻擊的基本原理

DPA攻擊是Kocher等人[3]于1999年提出來的,它是一門結合了統計分析與誤差修正的技術,利用不同明文輸入對應不同功耗曲線,推斷密碼算法中與密鑰相關的部分信息。對于密碼系統來說,功耗的變化主要由內部寄存器狀態跳變引起,統計學上表現為內部數據的漢明距離(Hamming Distance,HD)或漢明重量(Hamming Weight, HW)。簡單來說,DPA成功的基礎是大量的功耗曲線樣本,再結合相關統計學方面的知識,其基本流程包括功耗樣本采集,理論功耗模型建立,密鑰猜測,功耗偏差分析和密鑰判斷[5,6]等,如圖1所示。

首先DPA攻擊者隨機選擇n個明文作為輸入進行N次加密運算,對應于每一次的加密運算的明文Pi,搜集相應的離散功耗信號Sij,以及相應的輸出密文Oi。功耗信號S中的i和明文輸入P中的i相關,j和采樣時間相關。則可使用選擇函數D(·,·,·)把Si分成兩部分:

圖1 DPA攻擊的基本流程

然后計算每一部分的平均功耗為

如果運算中涉及了選擇函數的某位或包含這個位的數據時,該數據的值是0或1會對功耗曲線的幅值有細小的影響。假定這個細小的差別為ε,并且在時間j*時計算D函數,則功耗之間的數學期望E可用下式表示:當j=j*時,加密模塊執行密鑰比特,則功耗大小與D函數相關

當j≠j*時,加密模塊執行其他比特,則功耗大小與D函數無關

從式(6)和式(7)可知,如果采樣明文足夠多,則T[j]就能計算出在時間j時的功耗差分ε。為了更好地探討防御DPA攻擊的方法,文獻[1]將式(6)改寫為

其中r為功耗偏差值,xi為i時刻0值的功耗值,yi為i時刻1值的功耗值,為xi的平均功耗,為yi的平均功耗。從上述分析中可以知道,防御DPA攻擊的主要思想就是使r盡可能地小,使之近似為0。

3 主流防御DPA攻擊技術的概述與分析

近年來,防御DPA攻擊技術作為一個熱點研究方向,在各個領域都引起了廣泛關注,涉及DPA攻擊的模型[7-9]、防御應用領域[10-14]和新的防御技術[15-19]等等。從IEEE歷年文獻的統計中可以發現,關于防御DPA攻擊技術的研究呈逐年遞增的態勢,其主要途徑大致可分為兩類:一是盡量降低功耗曲線的波動,減小功耗曲線中的信息含量,即采用降低信噪比的方法達到防御DPA攻擊的目的;二是盡量擾亂功耗曲線與數據的相關性,即采用增加隨機噪聲和冗余功耗達到防御DPA攻擊的目的。這兩種途徑都可以提高密碼芯片的安全性,使攻擊者難以實施DPA攻擊或者需要更多的功耗曲線樣本。主流防御技術包括隨機掩碼技術[20-36]、功耗隱藏技術[37-51]和功耗擾亂技術[52-54]等等。

3.1 隨機掩碼技術

Kocher等[3]在 1999年首次提出使用隨機掩碼(Mask)技術來防御DPA攻擊。Mask技術利用攻擊者不可能獲取的隨機變量m對密碼算法的中間變量V進行掩蓋,從而得到掩蓋后的中間變量Vm(Vm=V·m),使攻擊者每次獲取的功耗信息均由中間變量Vm產生,而且由于m是隨機變化的,每次加密并不相同,所以攻擊者將無法獲得中間變量V所帶來的功耗與密鑰的相關性。由于加密過程中的各個操作均是與數據相關的,所以要求整個加密過程中所有的中間變量都被m所屏蔽。典型的Mask分為兩種[6]:布爾型的 Mask,一般用異或操作實現x'=x⊕r;算術型的 Mask,一般用模加模乘來實現x'=(x-r)mod2k。其中,布爾掩碼與算術掩碼可以相互轉換,偽代碼如表1所示。

表1 偽代碼

圖2 基于Mask的標準單元

在隨機掩碼算法與芯片實現方面,Yoshikawa等人[20]提出多輪Masking方法防御DPA攻擊和高效的隨機數掩碼方法[21];Zhang等人[22]提出一種能防御DPA攻擊的橢圓曲線密碼算法;Prouff等人[23]提出利用置換表的方法防御一階旁道攻擊;Rivain等人[30]提出將高階 Mask[31-33]應用到高級加密標準(AES)算法中,實現防御 DPA攻擊。Mangard等人[1]提出一種通用的掩碼方法,將隨機掩碼用于AES密碼算法,實現對電路中所有處理單元的輸入和輸出全部屏蔽,達到防御DPA攻擊的目的。隨機掩碼AES加密算法包括掩碼操作,輪密鑰加,字節替換,行移位和列混淆等,如圖3所示。其中,為處理單元的輸入輸出狀態,m為屏蔽因子,字節替換中的非線性操作采用掩碼后Sbox實現。

3.2 功耗平衡技術

功耗平衡技術可以從根本上解決功耗泄露密鑰信息的問題,是近年防御 DPA攻擊的首選技術[37-51]。功耗平衡技術對密碼芯片內部的存儲信號采用漢明擴展編碼進行重新編碼,如比特“0”用“01”表示,而比特“1”用“10”表示。這就可以實現,從比特0變化到比特1和從比特1變化到比特0的狀態變化都相同,因此也就難以區分漢明重量和比特翻轉引起的功耗變化。從功耗分析上看,這個方法在理論上相對而言比較完善。但是從硬件實現上,它的資源消耗比較大,面積至少增加一倍以上,另外硬件實現上需要全部重新設計,沒有相應的自動化設計工具支持,比較費時費力。功耗隱藏技術研究已經非常成熟,相關功耗平衡邏輯電路也很多,主要包括雙軌邏輯[37-43]、SABL邏輯[40]、WDDL邏輯[41]、MDPL邏輯[42]和DDSLL邏輯[46]等等。

圖3 基于Mask的AES加密算法

在靜態互補CMOS邏輯中,只有輸出發生0→1跳變時,邏輯門才消耗能量。雙軌邏輯在一定程度上打破了數據與功耗的相關性,雙軌邏輯結構模型如圖4所示。Cq0為輸入端電容,Cqw為線電容,Cqj為輸出端電容。

圖4 雙軌邏輯結構模型

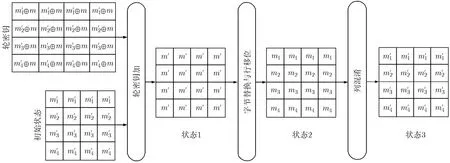

圖5 基于WDDL的與門

文獻[41]在 0.18 μm CMOS工藝下實現基于AES密碼算法的嵌入式安全協處理器芯片,如圖6所示。該芯片可應用在指紋識別上,包括密碼算法模塊,指紋匹配模塊,模板存儲單元以及接口電路等。該芯片由兩個處理器構成,32 bit SPARC V8處理器使用標準CMOS庫實現,第2個協處理器使用WDDL邏輯實現。該嵌入式安全協處理器芯片采用兩種方式防御DPA攻擊:第1種方法為WDDL邏輯,使所有邏輯門在每個時鐘周期都消耗相同的功耗;第2種方法稱為口令路由識別,確保WDDL邏輯在輸出節點上0和1的數量完全相同。對該安全協處理器芯片進行了防御 DPA攻擊的性能分析比較。對標準CMOS邏輯實現的AES算法,僅需要8000次功耗曲線樣本就能實現DPA攻擊;使用WDDL邏輯實現的AES算法使用1500000次功耗曲線樣本時仍難實現 DPA攻擊。實驗結果表明,WDDL邏輯與標準CMOS邏輯相比較,在安全性方面至少可以提高2個數量級。

圖6 基于WDDL的AES密碼算法協處理器

3.3 功耗擾亂技術

功耗擾亂技術包括時鐘功耗擾亂技術和旁路功耗擾亂技術[5,55-59]。時鐘功耗擾亂技術是指利用時鐘頻率的隨機變化對密碼芯片的微觀功耗進行擾亂。韓軍[5]提出基于時間隨機化的密碼芯片防御攻擊方法,建立了隨機時間延遲防御DPA攻擊的理論模型,并得到了隨機時間延遲抑制DPA攻擊的閾值條件。文獻[57]的分析結果表明,時鐘功耗擾亂技術在提高芯片安全性的同時,會降低部分功耗,但造成約16%時間損耗,影響數據處理性能。

旁路功耗擾亂技術是指在不影響系統性能的前提下,構建與密碼算法關鍵模塊相關的旁路模塊,擾亂其功耗與數據的相關性,實現防御DPA攻擊的目的。文獻[56]針對AES密碼算法關鍵模塊Sbox,提出如圖7所示的旁路結構,其中旁路模塊的電路結構為如圖8所示的環形振蕩器。該方法可以有效解決吞吐量退化問題。然而,在系統復位的時候偽隨機數發生器生成數據字節是相同的,這就有可能被攻擊者所利用。為了解決這個問題,文獻[60]采用了真隨機數發生器不僅能夠自動生成隨機數序列防御DPA攻擊,而且可以在提高系統安全性的同時減少面積開銷。

圖7 基于旁路功耗擾亂技術的Sbox結構框圖

4 防御DPA攻擊的前沿技術與發展趨勢

上述主流防御DPA攻擊方法并不完善,還存在以下方面的問題:Mask技術需要增加屏蔽因子和掩碼操作,改變了算法流程,并且在構造偽Sbox時往往需要十分大的硬件存儲空間,這樣就增加協處理器的面積;功耗平衡技術帶來電路面積增大和平均功耗上升,另外硬件實現上需要全部重新設計,沒有相應的自動化設計工具支持,比較費時費力;功耗擾亂技術能降低部分功耗,但通常會帶來時間損耗,影響數據處理性能,增加額外面積開銷。本節對未來可能產生重大影響的防御 DPA攻擊新技術進行探討,包括基于物理不可克隆函數(PUF)電路的防御DPA技術、基于多值行為的防御DPA技術以及基于多核處理器的防御DPA技術等,同時探測防御DPA技術的發展新趨勢和研究熱點。

圖8 基于環形振蕩器的旁路模塊

4.1 基于PUF電路的防御DPA攻擊技術

PUF最早由麻省理工大學的 Gassend等人[61]提出,是一種半導體芯片的“芯片DNA”技術,通過提取IC制造過程中不可避免產生的差異,生成無限多個唯一的、不可預測的密鑰。這些密鑰具有隨機性、唯一性和不可克隆性等特性[62-72]。利用PUF電路的唯一性和不可克隆性,將芯片制造的工藝偏差與具體密碼算法相融合,賦予電路輸出的數據具有特定含義,實現電路功耗與所處理數據沒有直接對應關系,使得攻擊者無法獲取真實信息。基于仲裁器和信號傳輸延遲的 PUF方案是由一個信號傳輸延遲電路和一個仲裁器組成,如圖9所示。電路中布置了上下兩條完全對稱的信號傳輸延遲通路,同一信號在兩條通路上競爭通過,仲裁器根據競爭結果判斷輸出是0或1。輸入激勵是一個64 bit的比特串,用來控制信號傳輸通路,輸出是1 bit,作為PUF的輸出響應。可以將PUF電路應用到AES加密芯片,設計抗DPA攻擊的AES芯片。

圖9 PUF的電路結構

4.2 基于多值行為的防御DPA攻擊技術

多值行為是指數字信號的取值數比傳統的取值數2(即0、1)多的情況[73-77]。以四值為例(邏輯值為0, 1, 2, 3),邏輯值的數量為傳統二值邏輯的兩倍,輸出端口邏輯狀態跳變(0→0, 0→1, 0→2, 0→3,1→0, 1→1, 1→2, 1→3, 2→0, 2→1, 2→2, 2→3,3→0, 3→1, 3→2, 3→3)數為傳統二值狀態跳變(0→0, 0→1, 1→0, 1→1)數的4倍。隨著基數的增加,狀態跳變的復雜性呈指數形式增長。將多值行為融合到防御DPA攻擊的VLSI設計中,利用多值行為狀態跳變的多樣性和復雜性,打破功耗與電路狀態跳變之間的對應關系,達到提高電路安全性能的目的。同時,多值信號可以增加電路單線信息攜帶量,提高空間或時間的利用率,這將有利于提升密碼芯片的性能。

4.3 基于多核處理器的防御DPA攻擊技術

多核處理器的優勢是每一個單核處理器都能以不同的時鐘頻率工作,結合時鐘擾亂技術防御DPA攻擊。另外,每個處理器的時鐘可調,可以使得它工作在最佳的狀態,任務多的時候就以接近滿負荷的高時鐘頻率工作,達到最高的性能[78,79]。Ambrose等人[80-82]提出多核處理器在防御DPA攻擊上的應用。基本思想是在越來越多處理器系統中利用功耗平衡的方法來防御DPA攻擊,即每運行一條加密指令,兩個結構完全相同的處理器單核,同時執行互補指令操作。當一個處理器開始執行加密算法時,自動啟動第 2個處理器的加密程序并執行互補指令,如圖10所示。

圖10 多核處理器的結構框圖

多核處理器防御 DPA攻擊還需要設計相應的密碼算法。文獻[80]針對AES算法提出一種適用于多核處理器的功耗平衡算法。該設計具有兩個顯著的優點,一方面僅當AES算法執行時兩個處理器才會進行平衡數據位翻轉的操作,另一方面當加密電路不執行AES算法時,兩個結構可分別執行獨立的操作。MUTE-AES算法結構如圖11所示,包括AES加密算法與互補AES加密算法。同時該設計思想也可應用于數據加密標準算法(DES),文獻[81]提出適用于多核處理器的 MUTE-DES算法,實現防御

DPA攻擊。

4.4 防御DPA攻擊技術研究熱點探討

4.4.1 高性能、低成本的防御技術研究目前,雖然已經提出不少防御DPA攻擊技術,但是存在的主要問題是硬件成本太高,運算速度偏低,因此如何在確保安全性的同時提高密碼芯片的性能,是未來防御DPA攻擊技術研究的熱點。半導體制造工藝的進步和市場的客觀需求,也不斷推動高性能、低成本防御技術的發展。Guo等人[83]在權衡芯片面積、速度和安全性的前提下,提出一種通用橢圓曲線加密算法(ECC)協處理器架構,達到防御旁道攻擊和故障攻擊的目的。Cevrero等人[48]提出通過MCML邏輯實現大大降低電路的功耗,達到低功耗防御功耗攻擊設計,并建立PG-MCML的標準單元庫,支持傳統的電子設計自動化(EDA)工具。

圖11 MUTE-AES加密算法

4.4.2防御復合型攻擊技術研究隨著DPA攻擊技術的研究使得密碼芯片開始時刻面臨復合型攻擊的威脅。復合型攻擊利用算法漏洞和旁道信息,綜合數學攻擊、功耗攻擊、電磁輻射攻擊、時間攻擊、錯誤攻擊和模板攻擊等等技術,只要任何一個環節存在問題,都有可能造成關鍵信息泄露。所以它的攻擊性更強,防御也更困難。Lejla等人[84]集合碰撞攻擊和DPA攻擊,提出DCA(Differential Cluster Analysis)攻擊方法;Benedikt等人[85]提出一種綜合旁道泄露信息的MIA(Mutual Information Analysis)攻擊方法,并且Nicolas等人[86]對MIA攻擊進行理論深化與可行性分析。目前關于防御復合型攻擊的文獻較少,有待學者進一步研究。

4.4.3 防御DPA攻擊的測試平臺防御DPA攻擊是一種實驗性很強的技術手段,由于信息安全的特殊性,相關的測試技術和設備又受到國外限制,而目前國內的測試條件和實驗設備相當有限,對大部分研究單位而言,防御DPA攻擊技術的評價標準和評估手段基本停留在理論分析和軟件仿真階段。因此,制定有效的防御DPA攻擊技術標準以及搭建防御DPA攻擊測試平臺,也是將來研究中必須解決的問題之一。

測試平臺主要包括DPA測試平臺的軟件、硬件設計。軟件方面需要包括集成各類數學模型的DPA數據分析軟件,實驗平臺運行控制軟件等;硬件方面需要包括集成加密芯片電路的硬件系統,功耗采集設備等。由 Tokyo Electron Device公司提供的SASEBO[87]是一款具有內置密碼算法電路,專門為邊旁道攻擊設計的 FPGA開發板,其中型號SASEBO-GII還增加了擴展外部實驗設備的功能,如圖12所示。它既可以提供密碼算法的工作環境,又可以針對具體的密碼算法實現旁道攻擊,是一個小型測試平臺。SASEBO-GII配備最新的 Xilinx Virtex-5 LX30/LX50 FPGA芯片用作算法電路,相比其它型號增加約4~7倍的邏輯電路面積;此外,它還向用戶提供多種配置FPGA的途徑,測試和用戶界面大大簡化。

關于防御 DPA攻擊技術還有以下幾個方面值得關注:DPA攻擊及其防御技術理論有待進一步完善;功耗攻擊技術與密碼學等理論內在聯系的研究有待于進一步深入;功耗安全策略等相關防御理論在密碼芯片設計中有待進一步應用;防御系統的功耗、延時、面積等方面開銷過大,電路結構有待進一步優化;防御系統性能評價缺乏統一的標準,基于功耗分析的相關度、2維相關性等的安全性能評價體系有待充實完善。

圖12 SASEBO-GII開發板

5 結論

本文對防御DPA攻擊技術進行了綜述,對主流防御DPA攻擊技術進行概述與分析,并對前沿防御技術與研究熱點進行探討。雖然對防御DPA攻擊技術的研究已經取得一定的成果,但是存在的問題依然嚴峻,有待研究者進一步探索。密碼芯片DPA防御技術研究是一個多學科交叉的工作,需要研究者具有現代密碼學、數理統計學、電路與系統、微電子學等多種學科的知識,從數學分析、軟件算法到電路結構,直至芯片 VLSI實現都要有深入研究。并且此項研究還需要綜合考慮多種因素,其中包括技術的因素,也包含社會和經濟的因素。開展密碼芯片的DPA防御技術研究,防止將來可能會出現的信息安全威脅,將對國民經濟的健康發展和社會穩定繁榮起到良好的促進作用。

[1]Mangard S, Oswald E, and Popp T. Power Analysis Attacks:Revealing the Secrets of Smart Cards[M]. Graz University of Technology, Austria, Published by Springer, 2007: 1-306.

[2]Kocher P C. Timing attacks on implementations of Diffie-Hellman, RSA, DSS, and other systems[C]. Advances in Cryptology(CRYPTO’96), Berlin, Springer, 1996, LNCS 1109: 104-113.

[3]Kocher P C, Jaffe J, Jun B,et al.. Differential power analysis[C]. CRYPTO’99, Santa Barbara, CA, USA, Lecture Notes in Computer Science, Aug. 15-19, 1999: 388-397.

[4]Gandolfi K, Mourtel C, and Olivier F. Electromagnetic analysis: concrete results[C]. CHES 2001, 2001, LNCS 2162:251-261.

[5]韓軍. 信息安全芯片的防御攻擊技術研究[D]. [博士論文], 復旦大學, 2006.

Han Jun. Research on attack countermeasures of security chip [D]. [Ph.D. dissertation], Fundan University, 2006.

[6]鄭新建, 張翌維, 沈緒榜. SPA和DPA攻擊與防御技術新進展[J]. 小型微型計算機系統, 2009, 30(4): 726-731.

Zheng Xin-jian, Zhang Yi-wei, and Shen Xu-bang. Advanced evolution of SPA and DPA attack and resistance techniques[J].Journal of Chinese Computer Systems, 2009, 30(4):726-731.

[7]Alioto M, Poli M, and Rocchi S. A general power model of differential power analysis attacks to static logic circuits [J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems, 2010, 18(5): 711-724.

[8]Wang Peng-jun and Hao Li-peng. A novel differential fault analysis on AES-128[C]. 2011 IEEE 9th International Conference on ASIC(ASICON), Xiamen, China, Oct. 25-28,2011: 9-12.

[9]Lu Y, Boey K, Hodgers P,et al.. Lightweight DPA resistant solution on FPGA to counteract power models[C]. 2010 International Conference on Field-Programmable Technology(FPT), Beijing, China, Dec. 8-10, 2010: 178-183.

[10]Bodhisatwa M, Debdeep M, and Indranil S. Design for security of block cipher S-boxes to resist differential power attacks[C]. 2012 25th International Conference on VLSI Design(VLSID), Hyderabad, India, Jan. 7-11, 2012:113-118.

[11]Mangard G. Securing implementations of block ciphers against side channel attacks[D]. [Ph.D. dissertation], Austria,Graz University of Technology, 2004.

[12]Oswald E, Mangard S, Pramstaller N,et al.. A side-channel analysis resistant description of the AES S-box[C]. 12th International Workshop Fast Software Encryption, 2005,LNCS 3557: 413-423.

[13]Kocher P. Design and validation strategies for obtaining assurance in countermeasures to power analysis and related attacks[C]. NIST Physical Security Workshop, San Francisco,America, 2005: 26-29.

[14]汪鵬君, 郝李鵬, 張躍軍. 防御零值功耗攻擊的AES SubByte模塊設計及其 VLSI實現[J]. 電子學報, 2012, 40(11):2183-2187.

Wang Peng-jun, Hao Li-peng, and Zhang Yue-jun. Design of AES subbyte module of anti-zero value power attack and its VLSI implementation[J].Acta Electronica Sinica, 2012,40(11): 2183-2187.

[15]Moradi A, Mischke O, and Paar C. Practical evaluation of DPA countermeasures on reconfigurable hardware [C]. 2011 IEEE International Symposium on Hardware-Oriented Security and Trust(HOST), San Diego, California, USA,June 5-6, 2011: 154-160.

[16]Bai Xue-fei, Huang Lu, Wang Yi-fei,et al.. Evaluation of DPA attack resistance of transistor-based adiabatic logic styles[C]. 2010 2nd International Conference on e-Business and Information System Security(EBISS), Wuhan, China,May 1-3, 2010: 22-23.

[17]臧玉亮, 韓文報. 線性反饋移位寄存器的差分能量攻擊[J]. 電子與信息學報, 2009, 31(10): 2406-2410.

Zang Yu-liang and Han Wen-bao. Differential power attack on liner feedback shift register[J].Journal of Electronics&Information Technology, 2009, 31(10): 2406-2410.

[18]Michael Z, Michael K, Marc S,et al.. Side channel analysis of the SHA-3 finalists[C]. Design, Automation & Test in Europe Conference & Exhibition(DATE), Dresden, Germany,March 12-16, 2012: 1012-1017.

[19]Lin Lang and Burleson W. Analysis and mitigation of process variation impacts on power-attack tolerance[C]. 2009 47th ACM/EDAC/IEEE Design Automation Conference(DAC),San Francisco, California, USA, July 2009: 26-31.

[20]Yoshikawa M and Sugiyama M. Multi-rounds masking method against DPA attacks[C]. 2011 IEEE International Conference on Information Reuse and Integration(IRI), Las Vegas, USA, Aug. 3-5, 2011: 100-103.

[21]Yoshikawa M and Kojima Y. Efficient random number for the masking method against DPA attacks [C]. 2011 21st International Conference on Systems Engineering(ICSEng),Las Vegas, USA, Aug. 16-18, 2011: 321-324.

[22]Zhang Tao, Fan Ming-yu, and Zheng Xiao-yu. Secure and efficient elliptic curve cryptography resists side-channel attacks[J].Journal of Systems Engineering and Electronics,2009, 20(3): 660-665.

[23]Prouff E and McEvoy R. First-order side-channel attacks on the permutation tables Countermeasure[C]. CHES 2009, 2009,LNCS 5747: 81-96.

[24]趙佳, 曾曉洋, 韓軍, 等. 抗差分功耗分析攻擊的AES算法的VLSI實現[J]. 計算機研究與發展, 2007, 44(3): 378-383.

Zhao Jia, Zeng Xiao-yang, Han Jun,et al.. VLSI implementation of an AES algorithm resistant to differential power analysis attack[J].Journal of Computer Research and Development, 2007, 44(3): 378-383.

[25]鄭新建, 張翌維, 彭波, 等. 抗DPA攻擊的AES算法研究與實現[J]. 計算機科學與探索, 2009, 3(4): 405-412.

Zheng Xin-jian, Zhang Yi-wei, Peng Bo,et al.. Research and implementation of DPA resistant AES algorithm [J].Journal of Frontiers of Computer Science and Technology, 2009, 3(4):405-412.

[26]Gebotys C H. A table masking countermeasure for lowenergy secure embedded systems[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems, 2006, 14(7):740-753.

[27]Alam M, Ghosh S, Mohan M J,et al.. Effect of glitches against masked AES S-box implementation and countermeasure[J].IET Information Security, 2009, 3(1):34-44.

[28]Fischer W and Gammel B M. Masking at gate level in the presence of glitches[C]. CHES 2005, 2005, LNCS 3659:187-200.

[29]Popp T and Mangard S. Masked dual-rail pre-charge logic:DPA-resistance without routing constraints [C]. CHES 2005,2005, LNCS 3659: 172-186.

[30]Rivain M and Prouff E. Provably secure higher-order masking of AES[C]. CHES 2010, 2010, LNCS 6225: 413-427.

[31]Coron J S, Prouff E, and Rivain M. Side channel cryptanalysis of a higher order masking scheme[C]. CHES 2007, 2007, LNCS 4727: 28-44.

[32]Rivain M, Prouff E, and Doget J. Higher order masking and shuffling for software implementations of block ciphers[C].CHES 2009, 2009, LNCS 5747: 171-188.

[33]童元滿, 王志英, 戴葵, 等. 一種抗DPA及HO-DPA攻擊的AES算法實現技術[J]. 計算機研究與發展, 2009, 46(3):377-383.

Tong Yuan-man, Wang Zhi-ying, Dai Kui,et al.. A DPA and HO-DPA resistant implementation of AES[J].Journal of Computer Research and Development, 2009, 46(3): 377-383.

[34]Najeh K, Lilian B, and Adel G. A masked correlated power noise generator use as a second order DPA countermeasure to secure hardware AES cipher[C]. 2011 23rd International Conference on Microelectronics(ICM), Hammamet, Tunisia,Dec. 19-22, 2011: 1-5.

[35]Kim Hee-Seok, Hong Seo-khie, and Lim Jongin. A fast and provably secure higher-order masking of AES S-box [C].CHES 2011, 2011, LNCS 6917: 95-107.

[36]Fumaroli G, Martinelli A, Prouff E,et al.. Affine masking against higher-order side channel analysis[C]. CHES 2011,2011, LNCS 6917: 262-280.

[37]Yue Da-heng, Li Shao-qing, and Zhang Min-xuan. Static timing analysis in dual-rail precharge logic based DPA resistant circuit design[C]. 2010 International Conference on Electronics and Information Engineering(ICEIE), Sichuan,China, Aug. 1-3, 2010: V1-236-V1-240.

[38]Bucci M, Giancane L, Luzzi R,et al.. Delay-based dual-rail precharge logic[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems, 2011, 19(7): 1147-1153.

[39]Guilley S, Sauvage L, Flament F,et al.. Evaluation of power constant dual-rail logics countermeasures against DPA with design time security metrics[J].IEEE Transactions on Computers, 2010, 59(9): 1250-1263.

[40]Zhang Yue-jun, Wang Peng-jun, and Hao Li-peng. Design of resistant DPA three-valued counter based on SABL [C]. 2011 IEEE 9th International Conference on ASIC(ASICON),Xiamen, China, Oct. 25-28, 2011: 9-12.

[41]Hwang T D and Hodjat A. AES based cryptographic and biometric security coprocessor IC in 0.18 μm CMOS resistant to side-channel power analysis attacks [J].IEEE Transactions on Journal of Solid-State Circuits, 2006, 41(4): 781-792.

[42]Bucci M, Giancane L, Luzzi R,et al.. Three-phase dual-rail pre-charge logic[C]. CHES 2006, 2006, LNCS 4249: 232-241.

[43]Sokolov D, Murphy J, Bystrov A,et al.. Design and analysis of dual-rail circuits for security applications[J].IEEE Transactions on Computers, 2005, 54(4): 449-459.

[44]Suzuki D and Saeki M. Security evaluation of DPA countermeasures using dual-rail pre-charge logic style[C].CHES 2006, 2006, LNCS 4249: 255-269.

[45]Atani R E, Mirzakuchaki S, Atani S E,et al.. Design and simulation of a DPA resistive circuit for tritium stream cipher based on SABL Logic styles[C]. 15th International Conference on Mixed Design of Integrated Circuits and Systems(MIXDES 2008), Pozna, Poland, 2008: 19-21.

[46]Renauld M, Kamel D, Standaert F,et al.. Information theoretic and security analysis of a 65-nanometer DDSLL AES S-box [C]. CHES 2011, 2011, LNCS 6917: 223-239.

[47]Iwai K, Shiozaki M, Hoang A T,et al.. Implementation and verification of DPA-resistant cryptographic DES circuit using Domino-RSL[C]. 2011 IEEE International Symposium on Hardware-Oriented Security and Trust(HOST), San Diego, California, USA, June 5-6, 2011: 28-33.

[48]Cevrero A, Regazzoni F, Schwander M,et al.. Power-gated MOS current mode logic(PG-MCML): a power aware DPA-resistant standard cell library[C]. 2011 48th ACM/EDAC/IEEE Design Automation Conference(DAC),San Diego, California, USA, June 5-9, 2011: 1014-1019.

[49]Djukanovic M, Giancane L, Scotti G,et al.. Leakage power analysis attacks: effectiveness on DPA resistant logic styles under process variations[C]. 2011 IEEE International Symposium on Circuits and Systems(ISCAS), Rio de Janeiro,Brazil, May 15-18, 2011: 2043-2046.

[50]Mangard S, Oswald E, and Standaert F X. One for all-all for one: unifying standard differential power analysis attacks [J].IET Information Security, 2011, 5(2): 100-110.

[51]Burns F, Bystrov A, Koelmans A,et al.. Design and security evaluation of balanced 1-of-n circuits[J].IET Computers&Digital Techniques, 2012, 6(2): 125-135.

[52]Maxime N, Youssef S, Sylvain G,et al.. RSM: a small and fast countermeasure for AES, secure against 1st and 2nd-order zero-offset SCAs[C]. 2012 Design, Automation &Test in Europe Conference & Exhibition(DATE), Dresden,Germany, March 12-16, 2012: 1173-1178.

[53]Liu Po-chun, Hsiao Ju-hung, Chang Hsie-chia,et al.. A 2.97 Gb/s DPA-resistant AES engine with self-generated random sequence[C]. 2011 Proceedings of the ESSCIRC(ESSCIRC),Helsinki, Finland, Sept. 12-16, 2011: 71-74.

[54]Ratanpal G B, Williams R D, and Blalock T N. An on-chip signal suppression countermeasure to power analysis attacks[J].IEEE Transactions on Dependable and Secure Computing,2004, 1(3): 179-188.

[55]Rakers P, Connell L, Collins T,et al.. Secure contactless smartcard ASIC with DPA protection[J].IEEE Transactions on Journal of Solid-State Circuits, 2001, 36(3): 559-565.

[56]Liu Po-chun, Chang Hise-chia, and Lee Chen-yi. A low overhead DPA countermeasure circuit based on ring oscillators[J].IEEE Transactions on Circuits and Systems II:Express Briefs, 2010, 57(7): 546-550.

[57]Bucci M, Luzzi R, and Guglielmo M. A countermeasure against differential power analysis based on random delay insertion[C]. 2005 IEEE International Symposium on Circuits and Systems, Kobe, Japan, May 2005: 3547-3550.

[58]Regazzoni F, Cevrero A, and Standaert F X. A design flow and evaluation framework for DPA-resistant instruction set extensions[C]. CHES 2009, 2009, LNCS 5747: 205-219.

[59]Tillich S and Groch A J. Power analysis resistant AES implementation with instruction set extensions [C]. CHES 2007, 2007, LNCS 4727: 303-319.

[60]Liu Po-chun, Chang Hise-chia, and Lee Chen-yi. A true random-based differential power analysis countermeasure circuit for an AES engine[J].IEEE Transactions on Circuits and Systems II:Express Briefs, 2012, 59(2): 103-107.

[61]Gassend B, Clarke D, Marten V D,et al.. Silicon physical random functions[C]. Proceedings of the 9th ACM Conference on Computer and Communications Security,Washington, DC, USA, 2002: 148-160.

[62]Pappu R, Recht B, Taylor J,et al.. Physical one-way functions[J].Science, 2002, 297(5589): 2026-2030.

[63]Lim D and Lee J W. Extracting secret keys from integrated circuits[J].IEEE Transactions on VLSI Systems, 2005, 13(10):1200-1205.

[64]Zhang Yue-jun, Wang Peng-jun, Li Yi,et al.. Model and physical implementation of multi-port PUF in 65nm CMOS[J].International Journal of Electronics, 2012(online).

[65]Suh G E and Devadas D. Physical unclonable functions for device authentication and secret key generation[C]. Design Automation Conference, San Diego, California, USA, 2007:9-14.

[66]Edward G S and Devadas S. Physical unclonable functions for device authentication and secret key generation [C]. DAC 2007, San Diego, California, USA, 2007: 9-14.

[67]Holcomb D E, Burleson W P, and Fu K. Power-up SRAM state as an identifying fingerprint and source of true random numbers[J].IEEE Transactions on Computers, 2009, 58(9):1198-1210.

[68]Guajardo J, Kumar S S, Schrijen G J,et al.. FPGA intrinsic PUFs and their use for IP protection [C]. CHES 2007, 2007,LNCS 4727: 63-80.

[69]Kumar S and Guajardo J. The butterfly PUF protecting IP on every FPGA[C]. IEEE International Workshop on Host,Anaheim, CA, USA, 2008: 67-70.

[70]Lin L and Burleson W. Analysis and mitigation of process variation impacts on power-attack tolerance[C]. DAC 2009,San Francisco, California, USA, 2009: 26-31.

[71]Majzoobi M, Koushanfar F, and Potkonjak M. Techniques for design and implementation of secure reconfigurable PUFS [J].ACM Transactions on Reconfigurable Technology andSystems, 2009, 2(1): 1-33.

[72]Suzuki D and Shimizu K. The glitch PUF: a new delay-PUF architecture exploiting glitch shapes [C]. CHES 2010, 2010,LNCS 6225: 366-382.

[73]吳訓威. 多值邏輯電路設計原理[M]. 杭州: 杭州大學出版社,1994: 18-55.

Wu Xun-wei. Design principles of multivalued logic circuits[M]. Hangzhou: Publishing of Hangzhou University Press,1994: 18-55.

[74]Wang Peng-jun and Zhang Yue-jun. Design of four-valued operation circuits of adder and subtraction based on neuron MOS transistor[C]. 2009 Asia-Pacific Conference Information Processing, Shenzhen, China, 2009: 382-385.

[75]Zhang Yue-jun and Wang Peng-jun. Design of multi-valued double-edge-triggered JK flip-flop based on neuron MOS transistor[C]. 2009 IEEE 8th International Conference on ASIC, Changsha, China, 2009: 58-61.

[76]Wang Peng-jun, Li Kun-peng, and Mei Feng-na. Design of a DTCTGAL circuit and its application[J].Journal of Semiconductors, 2009, 30(11): 115006-1-115006-6.

[77]Wang Peng-jun and Gao Hong. Design of novel QCTGAL circuit[C]. 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology Proceedings,Shanghai, China, 2010: 680-683.

[78]Yu Z Y, Michael J M, Ryan W A,et al.. AsAP: an asynchronous array of simple processors [J].IEEE Transactions on Journal of Solid-State Circuits, 2006, 43(3):695-705.

[79]Yu Z Y, You K D, Xiao R J,et al.. An 800 MHz 320 mW 16-core processor with message-passing and shared-memory inter-core communication mechanisms[C]. 2012 IEEE International Solid-State Circuits Conference Digest of Technical Papers(ISSCC), San Francisco, CA, USA, Feb.19-23, 2012: 64-66.

[80]Ambrose J A, Parameswaran S, and Ignjatovic A. MUTEAES: a multiprocessor architecture to prevent power analysis based side channel attack of the AES algorithm [C]. 2008 IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, Nov. 10-13, 2008: 678-684.

[81]Ambrose J A. Power analysis side channel attacks: the processor design-level context[D]. [Ph.D. dissertation],University of New South Wales, 2009.

[82]Ambrose J A, Ragel R G, Parameswaran S,et al..Multiprocessor information concealment architecture to prevent power analysis-based side channel attacks [J].IET Computers&Digital Techniques, 2011, 5(1): 1-15.

[83]Guo X, Fan J F, Schaumont P,et al.. Programmable and parallel ECC coprocessor architecture: tradeoffs between area,speed and security[C]. CHES 2009, 2009, LNCS 5747:289-303.

[84]Lejla B, Benedikt G, and Kerstin L R. Differential cluster analysis[C]. CHES 2009, 2009, LNCS 5747: 112-127.

[85]Benedikt G, Lejla B, Pim T,et al.. Mutual information analysis: a generic side-channel distinguisher[C]. CHES 2008,2008, LNCS 5154: 426-442.

[86]Nicolas V C and Standaert F X. Mutual information analysis:how, when and why?[C]. CHES 2009, 2009, LNCS 5747:429-443.

[87]Side-channel attack standard evaluation board [CL]. http://www.inrevium.jp/eng/sasebog2_user/, 2009.