遙控副載波數字化解調器技術研究

司瑩瑩

(濱州醫學院信息系統教研室,山東 煙臺 264003)

隨著通信技術迅猛發展,遙控技術作為通訊領域的一個分支,正向數字化、集成化、小型化、系列化方向發展。集成電路規模的擴大和生產工藝進一步提高,使遙控單元的數字化、軟件化成為可能,并替代現有的遙控單元,完成多模式解調功能。

與模擬解調器相比,數字化解調器有以下特點:(1)數字化解調器可編程能力強,對于相同的硬件平臺,通過軟件編程或參數的設置可以對載波頻率、碼速率、碼型等參數進行操作和控制;(2)抗干擾能力強,具有數字信號處理能力,易于仿真分析,便于多路復用、生產制造和調試[1]。

1 解調器原理

解調器由四個部分組成:數字下變頻模塊、載波同步模塊、位同步模塊和數據恢復模塊[2]。其結構如圖1所示。

圖1 解調器原理圖

輸入PSK 信號經過放大濾波等信號調理后,用模數轉換器直接進行正交采樣,產生兩路正交信號;將正交信號送入數字下變頻模塊(數字下變頻模塊由數字混頻器、數控振蕩器和帶通濾波器組成),信號與數控振蕩器產生的數字正交信號相乘,得到的兩路信號通過帶通濾波器,此帶通濾波器的帶寬恰好使信號的有用頻譜通過并阻止帶外的噪聲通過,經過帶通濾波和抽取后輸出為采樣速率較低的基帶數字信號I和Q;兩路基帶數字信號經過AGC(Automatic Gain Control),使其電壓增益自動地隨信號強度而調整,以達到自動增益控制的目的;輸出信號到載波同步模塊,載波同步模塊由復數乘法器、環路濾波器和數控振蕩器組成,使用科斯塔斯環[3]實現對副載波相位和頻率的跟蹤捕獲,以保證調制副載波和解調副載波的同頻同相;位同步模塊使用自同步法實現,信號經過位同步模塊后,實現符號定時的捕獲與同步,以保證本地估算采樣判決時刻始終與最佳采樣時刻一致;數據恢復模塊完成對原始調制信號的恢復,經過上述過程后得到脈碼調制數據PCM和時鐘CP,實現解調過程。

1.1 原理算法

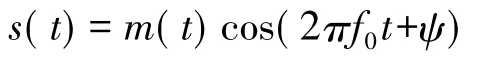

輸入的PSK 信號序列的表達式為:

其中,m(t)∈[-1,1]是二進制單極性隨機振幅,f0為接收信號的載波頻率,ψ為載波的瞬時相位[4]。

設在一個碼元持續時間T 內,經過帶通濾波后的接收信號和噪聲電壓為:

其中,n(t)為高斯白噪聲,根據隨機過程的理論,噪聲電壓可以表示為:

兩路正交信號通過數字下變頻后,高頻分量被去掉,得到的信號分量表示為:

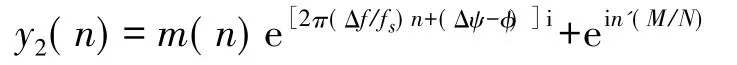

令Δf=fs-f為接收信號的頻率差,Δψ=ψ-φ為接收信號的瞬時相位差。輸出頻率fs接近于fc,使得Δf 接近與零,通過自動增益控制,放大電路的增益隨控制電壓而改變,此時得到的信號為:

選取適合的M、N值(M≥N),使不同載波和碼速率輸入下保持解調環路的結構不變。兩路信號經過復數乘法器后輸出的信號為:

通過設置頻率控制字和初始相位,數字控制振蕩器可生成所需的正余弦輸出序列,送入復數乘法器后得到的輸出信號為:

令σ=Δψ-φ,則當載波跟蹤環路設為鎖定狀態時,σ、Δf≈0,可將噪聲忽略,此時輸出信號則為:

將輸出的信號進行位同步,由于信號包含調制信息,即可得到解調信號。

1.2 載波同步

同步是調制系統十分重要的問題,只有收發兩端協調工作,系統才能真正實現解調功能。在相干解調中,相乘電路需要有相干載波,該載波必須要從接收信號中獲取,并且要求與接收信號具有相同的頻率和相位。載波同步就是在相干解調時,在接收設備中產生一個與接收信號的載波同頻同相的本地相干載波信號的過程,它是實現相干解調的基礎。本文介紹的解調器使用的載波同步環是改進的科斯塔斯環,它對傳統科斯塔斯環的改進是首先對兩路信號相乘獲得相位誤差信號,再對每個載波頻率進行π/2 相移。改進型的科斯塔斯環克服了傳統科斯塔斯環相位模糊的缺點[5],有利于提高信號的捕獲能力,適合于載波頻率經常變化時信號的提取。

環路濾波器是一種低通濾波器,主要作用是建立環路的動態特性,在鑒相器的輸出端衰減高頻誤差分量,以提高抗干擾性能[6]。當環路在跳出鎖定狀態時,可以提高環路以短期存儲,確保環路迅速重新捕獲信號。環路濾波器是實現載波同步的關鍵,在該解調器中使用環路濾波器目的是減弱由于輸入信號噪聲引起的相位誤差和高頻分量,以便在輸出端對原始輸入信號進行有效估計。環路濾波器對信號的動態響應程度取決于環路濾波器的階數,本文采用二階二型環,環路濾波器的傳遞函數可表示為:

環路濾波器[7]的結構如圖2所示。

圖2 環路濾波器結構圖

圖中C1為濾波器的比例通路的增益系數,C2為積分通路的增益系數,系數C1是無量綱的,C2必須有時間的量綱。C1和C2的值與選擇的環路參數(固有頻率ωn和無量綱的阻尼系數ξ)以及環路增益、采樣等均有關,C1、C2計算公式如下:

阻尼系數ξ 的值不宜過高,一般在0.5~1 的范圍內較好,大于1 的阻尼系數沒有過沖,阻尼系數小于0.5 的環路瞬態響應動態特性較差,過沖過大,在這里阻尼系數常取臨界阻尼系數0.707。ωn的取值范圍很寬,根據需要其范圍從10-5~108rad/s。Kd為鑒相器的增益系數,Ko為數控振蕩器靈敏度增益常量。

1.3 位同步

位同步是指接收端根據發送端發送數據的起止時間和時鐘頻率,產生一個時間基準相同、采樣判決時刻與最佳采樣時刻一致的定時脈沖序列。位同步又稱為碼元同步,其實現結構如圖3所示。

圖3 位同步實現結構圖

解調器中的位同步模塊通過自同步法[8]實現。解調器的位同步模塊通過相位誤差估算[9]輸出脈沖序列的采樣時鐘相位與最佳采樣時刻之間的相位差,然后產生一個頻率與定時誤差成比例的誤差脈沖,誤差脈沖經過環路濾波器濾除高頻成分和噪聲,進行低通濾波,得到頻率控制信號,通過數控振蕩器對頻率控制信號的頻率和相位進行調整。如果輸出脈沖序列提前于理想采樣信碼脈沖序列時刻,則使輸出脈沖序列扣除一個誤差脈沖,輸出的脈沖相位后退,實現采樣時刻滯后;反之則將輸出脈沖序列附加一個誤差脈沖,使輸出脈沖相位提前,實現采樣時刻提前,從而達到碼元同步的目的。這種自同步方法不需要改變時鐘相位,具有更好的穩定性,適用于對系統時鐘穩定性要求較高的場合。

2 數字解調器仿真

為了便于仿真,本文選用MATLAB 作為仿真工具。仿真數據源中的高斯白噪聲采用函數變換法產生,先生成(0,1)區間均勻分布的隨機數,再經過函數變換,利用瑞麗分布函數得到具有高斯噪聲特性的隨機數。

仿真前需要先運行配置初始化仿真參數,運行誤碼率自動仿真程序,用不同Eb/No 下誤比特數和總比特數相比,得到各信噪比下的誤碼率曲線。由于計算機直接生成仿真數據源,并且除加入高斯白噪聲外,不受其它噪聲影響,則不存在量化誤差。但是,較高的誤碼率需要很長的測試時間(如對1 kbit/s 在12 dB 時的誤碼率,一個點的測試大約需要10 h)。

文件運行結束后,繪制誤碼率曲線。1 kbit/s 誤碼率仿真結果如圖4所示。

圖4 1 kbit/s 誤碼率

利用圖1所示解調器,根據文中的算法仿真解調的誤碼率與理論誤碼率的比較如圖4所示,實線為理論誤碼率,圓點為仿真誤碼率。

3 結束語

本文介紹的解調器其優勢表現在:便于仿真分析、硬件設計實現;解調過程延遲少、抗干擾能力強、解調過程更穩定;載波同步、位同步響應速度快,跟蹤性能好,該解調器可以應用在低信噪比、較大頻率偏移范圍內工作。目前該解調器已得到工程化的應用。

[1]馮傳崗.論現代數字調制技術[J].有線電視技術,2003,(4):69-76.

[2]高翠東,趙琦,陸國雷,等.遙控副載波信號的軟件解調方法[J].信息安全與通信保密,2009,(12):50-52.

[3]張欣.擴頻通信數字基帶信號處理算法及VILI 實現[M].北京:科學出版社,2004:67-69.

[4]趙國棟,徐建良.基于多相濾波的正交采樣零中頻數字化接收及QPSK 高速解調的FPGA 實現[J].電路與系統學報,2010,(15):134-138.

[5]莊錫榮,焦會.改進型科斯塔斯(Costas)環探討[J].湖北成人教育學院學報,2009,15(1):121-123.

[6]時瑞瑞.中頻數字解調器的載波同步算法研究[D].碩士論文,2010,6:12-15.

[7]蔣毅凱,李國通,楊根慶.基于定點DSP 的軟件鎖相環的設計和實現[J].電子技術應用,2004,(4):51-53.

[8]孫海洋,劉杰.數字調制信號接收技術[J].現代電子技術,2008,(15):171-173.

[9]Gardner F M.A BPSK/QPSK Timing-Error Detector For Sampled Receivers[J].IEEE Trans.on Common,1986,34(5):423-429.