一種雷達窄帶數(shù)字接收機設(shè)計及關(guān)鍵技術(shù)研究*

王先超 祁 嶺

(海軍駐洛陽地區(qū)航空軍事代表室 洛陽 471009)

1 引言

傳統(tǒng)模擬體制的雷達接收機受采樣速率限制,且只能處理單一信號[1],設(shè)備可靠性穩(wěn)定性不高,接收機的數(shù)字化研究成為雷達系統(tǒng)發(fā)展重點。窄帶接收機由于其帶寬窄,在通帶內(nèi)出現(xiàn)同時到達多信號的概率小,可以實現(xiàn)對信號的高速處理,對帶內(nèi)信號有較高的攔截概率,是目前研究較多的一種數(shù)字接收機[2],本文研究了一種被動雷達系統(tǒng)窄帶數(shù)字接收機,設(shè)計上采取了基于脈寬匹配的多速率數(shù)字濾波器設(shè)計、采用歸一化處理運算的參數(shù)提取、通過FPGA計數(shù)實現(xiàn)方位角求取等多項技術(shù),可以增強信號的信噪比,縮短參數(shù)提取所需延時,簡化相位計算,該窄帶數(shù)字接收機已在工程中運用,對雷達系統(tǒng)設(shè)備穩(wěn)定、技術(shù)指標提升起到了重要作用。

2 系統(tǒng)概述

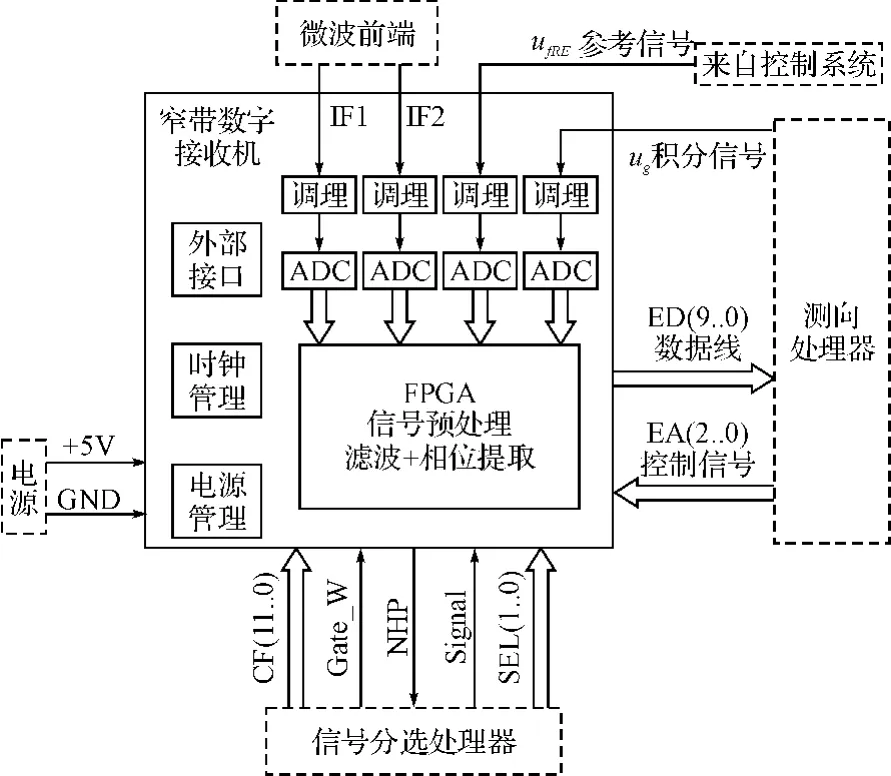

該窄帶數(shù)字接收機基于被動雷達信息處理系統(tǒng),雷達系統(tǒng)由信號分選跟蹤機、窄帶數(shù)字接收機及測向處理機三部分組成(圖1),信號分選跟蹤分機主要完成對環(huán)境的分選、識別、分析[3],對威脅信號提供PRI跟蹤波門,可在系統(tǒng)引導(dǎo)下對通過濾波器的信號進行PRI跟蹤,實時監(jiān)視跟蹤信號的變化,引導(dǎo)跟蹤器跟蹤;窄帶數(shù)字接收機主要完成數(shù)據(jù)采集和數(shù)據(jù)的預(yù)處理;測向處理分機完成閉環(huán)、開環(huán)測向算法、延遲線的數(shù)字控制并具有與信號分選跟蹤分機的通信功能。通過各分機的數(shù)據(jù)處理和分機間通信,即可完成輻射源信息采集與處理,并輸出控制信息,完成對輻射源的跟蹤。

3 窄帶數(shù)字接收機系統(tǒng)設(shè)計

3.1 系統(tǒng)框圖

窄帶數(shù)字接收機采用軟件無線電思想[4],將接收到的中頻信號通過ADC采樣后轉(zhuǎn)化為數(shù)字信號,然后進行數(shù)字下變頻處理,包括混頻、濾波、參數(shù)提取,得到所需的參數(shù)。

系統(tǒng)框圖如圖1所示,主要包括以下幾個部分:

1)數(shù)據(jù)采樣部分

利用高速ADC器件中頻信號進行采樣;同時,還選用低速ADC對參考信號ufRE和積分信號ug進行采樣。

2)信號處理部分

信號處理部分采用高性能FPGA實現(xiàn)[5],主要完成數(shù)字下變頻、數(shù)字濾波、相位差Δφ以及S、C提取、硬件數(shù)字積分求取、利用ufRE和ug計算方位角αfw等工作,之后將數(shù)據(jù)Δφ、和αfw在控制信號EA(2..0)控制下通過數(shù)據(jù)線ED(9..0)送入測向處理器。

3)外圍電路設(shè)計

為了保證電路的正常工作,還需要一定的輔助電路,如ADC前端調(diào)理電路、電源、時鐘及FPGA外圍電路等,各分機之間還需要進行隔離。

圖1 窄帶數(shù)字接收機系統(tǒng)框圖

3.2 系統(tǒng)工作模式

窄帶數(shù)字接收機能夠在開環(huán)和閉環(huán)兩種工作模式下給出所需信號,開環(huán)和閉環(huán)工作模式下的處理過程如下:

3.2.1 開環(huán)工作模式

在開環(huán)工作模式下,窄帶數(shù)字接收機接收兩路中頻信號IF1、IF2,利用FPGA對其進行數(shù)字鑒相后,得到相位差Δφ,測向處理器對其進行數(shù)字積分得到數(shù)字信號,通過求取的極大極小值之差,即可求出信號與彈軸夾角βy;通過比較模擬信號ug和ufRE之間的相位差,則可以求取方位角αfw。

3.2.2 閉環(huán)工作模式

在閉環(huán)工作模式下,窄帶數(shù)字接收機接受兩路中頻信號IF1、IF2,利用FPGA對其進行處理,得到IF1、IF2之間相位差的同相分量C和正交分量S,在C控制下對S進行積分,進而得到數(shù)字信號u′g;測向處理器利用模擬信號ug對駕駛儀進行控制,實現(xiàn)對導(dǎo)彈的控制。同時要求在閉環(huán)模式下也要輸出仰角βy和方位角αfw,處理過程同開環(huán)工作模式。

3.3 系統(tǒng)功能

窄帶數(shù)字接收機主要完成數(shù)據(jù)采集和數(shù)據(jù)的預(yù)處理,包括提取S、C、Δφ和αfw。即當(dāng)系統(tǒng)分別工作在開環(huán)模式和閉環(huán)模式下時,窄帶數(shù)字接收機能夠提供后續(xù)信號處理所需的信息,功能包括:

1)接收兩路中頻信號IF1、IF2,經(jīng)信號調(diào)理后,采用高速ADC芯片對其進行數(shù)據(jù)采集,求解兩路信號的S、C、Δφ,在C控制下對S進行數(shù)字積分,得到;

2)接收參考信號ufRE和積分信號ufRE,經(jīng)信號調(diào)理后,用低速ADC芯片對其進行數(shù)據(jù)采集,之后對其處理得到方位角afw;

3)將Δφ、afw等信號在控制信號 EA(2..0)控制下通過數(shù)據(jù)線ED(9..0)送至測向處理器。

3.4 系統(tǒng)工作過程

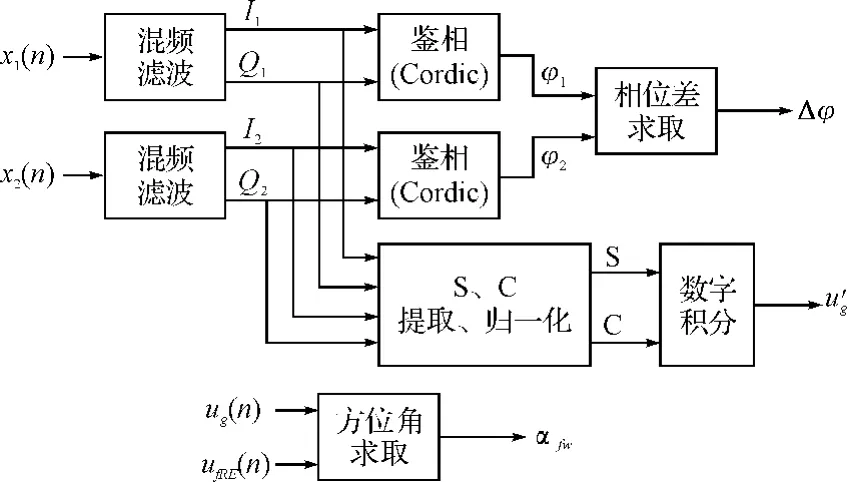

如圖2所示,系統(tǒng)將采集到的兩路中頻數(shù)據(jù)x1(n)和x2(n)、參考信號ufRE(n)、積分信號ug(n)送入 FPGA 內(nèi)部進行信號處理,得到Δφ、u′g、afw等信號,在控制信號 EA(2..0)的控制下,通過數(shù)據(jù)線ED(9..0)送入測向處理器進行進一步的處理。

圖2 系統(tǒng)工作流程

4 關(guān)鍵技術(shù)研究及實現(xiàn)

4.1 混頻、濾波

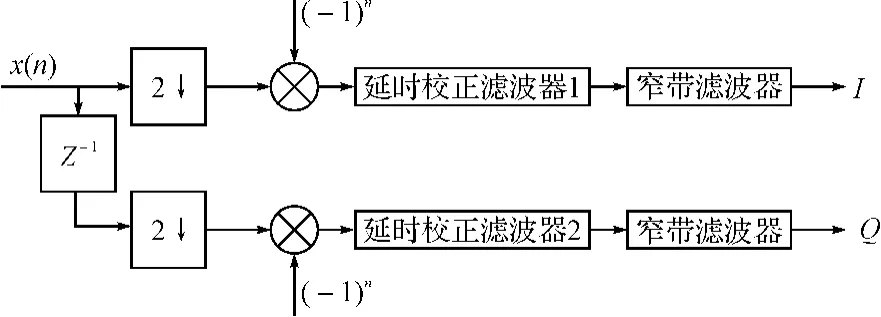

采用基于多相濾波的數(shù)字正交變換方法,可以得到本地的載波序列分別為0,1,0,-1和1,0,-1,0,混頻過程變得非常簡單,需要簡單的處理就可以完成,如圖3所示。

圖3 基于多相濾波的數(shù)字正交變換

如圖3所示,濾波分為兩部分,延時校正[6]和窄帶濾波。延時校正濾波器1和延時校正濾波器2可以消除抽取后數(shù)據(jù)在時域上的不對準(相差π/2),窄帶濾波器可以對信號的帶外噪聲進行濾除,提高信噪比。

本系統(tǒng)中設(shè)計了一種基于脈寬匹配的多速率數(shù)字濾波裝置,在對信號脈寬進行識別的前提下,接收機根據(jù)不同的脈寬采用不同的濾波器帶寬對信號進行處理,同時根據(jù)脈寬對輸出的數(shù)據(jù)速率進行調(diào)節(jié),可以在很大程度上濾除帶外噪聲,增強信號的信噪比,還可以減輕后續(xù)處理的復(fù)雜程度。

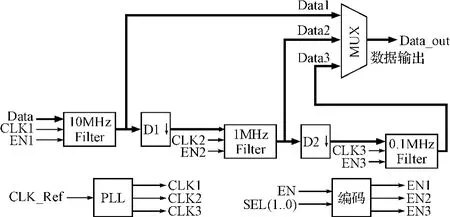

圖4 基于脈寬匹配的數(shù)字濾波器設(shè)計

圖4是基于脈寬匹配的數(shù)字濾波器框圖,采用了三種濾波器帶寬對信號進行濾波,分別是10MHz、1MHz、0.1MHz,其中采用了濾波器復(fù)用的方式,通過利用信號分選處理器給出的脈寬選擇信號SEL(1..0)對各級濾波器進行選擇,最終實現(xiàn)對不同脈寬類型的信號進行濾波;級間加入抽取模塊降低數(shù)據(jù)速率[7],有利于數(shù)字濾波器的設(shè)計;每級輸出Data1、Data2、Data3送入數(shù)據(jù)選擇輸出模塊 MUX,通過SEL(1..0)選擇最終數(shù)據(jù)輸出Data_out,減小系統(tǒng)功耗。各級濾波器的時鐘采用PLL統(tǒng)一管理。

系統(tǒng)在選擇某些脈寬類型時,可以禁用某些濾波器,如脈寬類型為00時,1MHz Filter和0.1MHz Filter不需要工作,可以通過給濾波器加入使能信號來完成。通過對EN信號和SEL(1..0)進行編碼,可以完成此功能。

4.2 S、C提取

4.2.1 提取原理[8]

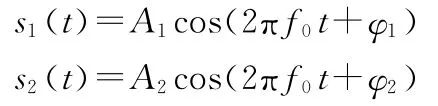

設(shè)兩中頻信號分別為

則經(jīng)過混頻后的信號濾除高頻分量后得到:

將信號s1(t)延時π/2后,在經(jīng)過混頻后的信號濾除高頻分量后得到:

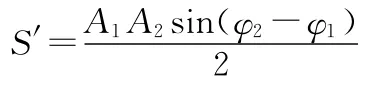

采用上述方法求解S′、C′,需要將其中一路信號延時π/2,對數(shù)字信號處理來講實現(xiàn)存在一定困難,而且采用上述方法求得的S′、C′與信號幅度A1A2有關(guān)系,所以考慮采用其它方法來求解歸一化后的S、C。本文采用歸一化處理運算,所需延時較小,約10個時鐘延時后即可得到歸一化后的S、C。

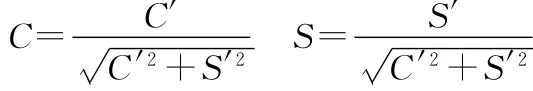

4.2.2 采用歸一化處理運算的S、C提取

把兩中頻信號分別經(jīng)過數(shù)字下變頻,得到兩路信號的同相分量和正交分量[9]分別為

用歸一化處理進行以下運算,得到

上述過程如平方、求和、開根號以及除法模塊,都可以在FPGA內(nèi)部調(diào)用模塊實現(xiàn)。

4.3 方位角的求取

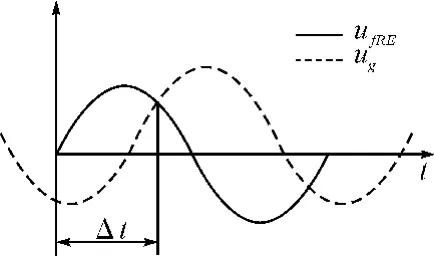

圖5繪出了參考信號ufRE(實線)和積分信號ug(虛線)的圖形,要求解方位角αfw,需要求解出兩路信號的相位差。傳統(tǒng)的求解相位差[10]的方法在本設(shè)計中很難實現(xiàn),原因在于天線旋轉(zhuǎn)一圈只能取得一個周期的參考信號和積分信號。如果對信號再進行濾波和相位提取,由于數(shù)據(jù)少,不能得到準確的值。

圖5 參考信號和積分信號示意圖

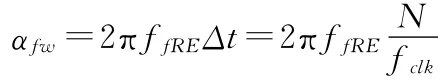

設(shè)計中采用另外一種方法實現(xiàn)方位角αfw的提取,可以通過比較兩路信號ufRE和ug過零點的時間差Δt,然后利用公式afw=2πffREΔt求得方位角αfw。

在利用FPGA實現(xiàn)時,可以在參考信號ufRE和積分信號ug的正向過零點時刻產(chǎn)生兩個尖脈沖,利用這兩個尖脈沖作為計數(shù)器的啟動信號和終止信號,將計數(shù)器輸出N和計數(shù)頻率fclk進行運算,便可得到Δt,求得方位角αfw:

方位角αfw的分辨率Δαfw由參考頻率fclk決定,Δαfw=2πffRE/fclk。

5 結(jié)語

本文提出了一種工程上實用的窄帶數(shù)字化接收機設(shè)計方案,采用高速采樣ADC、高性能FPGA芯片和軟件無線電思想,系統(tǒng)先進,集成度高,基于本設(shè)計思想開發(fā)的窄帶數(shù)字接收機已在某被動雷達信息處理系統(tǒng)中試用,具有實時處理性強、可靠穩(wěn)定的優(yōu)點。

[1]趙國慶.雷達對抗原理[M].西安:西安電子科技大學(xué),1999.

[2]孫墾.雷達數(shù)字化接收機[J].艦船電子對抗,2003,50(4):32-33.

[3]Mark A.Richards.雷達信號處理基礎(chǔ)[M].北京:電子工業(yè)出版社,2008.

[4]孫宏利.雷達接收機數(shù)字化分析[J].無線電工程,2011,41(3):25-27.

[5]韓慧奇.模塊化FPGA設(shè)計在某雷達接收機中的應(yīng)用[J].電子技術(shù),2009,51(9);33-35.

[6]戈穩(wěn).雷達接收機技術(shù)[M].北京:電子工業(yè)出版社,2005.

[7]ELINT:The Interception and Analysis of Radar Signals[M].BeiJing:Publishing House of Electrnics Industry,2008.

[8]蘇軍海,張龍.寬帶雷達機動多目標檢測[J].電子與信息學(xué)報,2010,32(3):564-569.

[9]Chan h C.Radar sea-clutter at low grazing angles[J].IEE Proc.-F,1990,137(2):102-112.

[10]何勤.一種通用中頻數(shù)字化接收機的實現(xiàn)[J].現(xiàn)代電子技術(shù),2009,298(11):15-18.