基于FPGA的DDS基本信號發生器的設計

趙麗娜,郭寶增,劉少鵬,馬 韜

(河北大學 電子信息工程學院,河北 保定 071002)

DDS(Direct Digital Frequency Synthesis)即直接數字式頻率合成,是從相位概念出發直接合成所需波形的一種頻率合成技術[1]。與傳統信號源所采用的用模擬方式生成信號不同,它是將先進的數字信號處理理論與方法引入信號合成領域。DDS技術在精確度、靈活度等方面都超過模擬信號發生器。并且DDS可實現相位連續變化,且具有良好頻譜的信號,這是傳統方法無法實現的。

FPGA的迅速發展為DDS提供了更加優良的技術手段,它具有處理速度快、可靠性高等特點。SOPC(System On Programmable Chip,片上可編程系統)是一種靈活、高效的SOC解決方案[2]。它以IP Core為基礎,將處理器、存儲器、IO口等系統設計需要的功能模塊集成到一個FPGA器件上,構建成一個可編程的片上系統,具有靈活的設計方式。本設計綜合以上軟硬件可編程協同設計技術,使得DDS電路在靈活性,可行性,精確性等方面得到很大提高。

1 DDS的基本原理

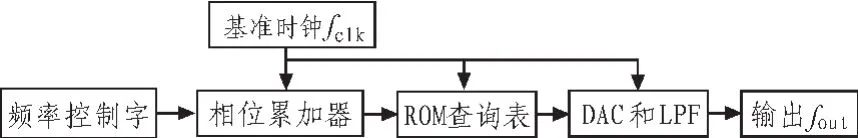

DDS信號發生器是由:頻率控制字、相位累加器、ROM表、D/A轉換器以及模擬低通濾波器LPF組成.原理框圖如圖1所示。

圖1 DDS原理圖Fig.1 DDS schematic

首先對波形的一個周期進行連續采樣,通過計算得到每一點對應的幅度值,然后以二進制格式存放在數據文件中。在時鐘脈沖fclk驅動下,每個時鐘周期內頻率控制字與相位累加器累加一次,產生ROM查找表的地址值,隨后通過查表變換,地址值被轉化為信號波形的數字幅度序列,即可得到幅度上離散的波形,再由數模變換器(D/A)將表示波形幅度的數字序列轉化為模擬量。最后經由LPF將D/A輸出的階梯狀波形平滑為所需的連續波形。理論上,采樣點數越多,生成波形精確度越高[3]。

2 基于FPGA的DDS設計

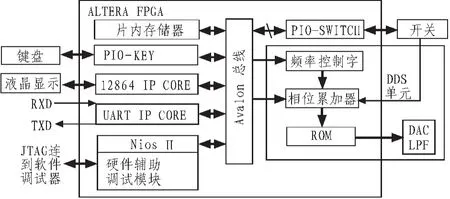

本設計在Altera的EP2C35F672C8芯片的基礎上,在SOPC Builder和QuartusⅡ開發環境下,利用SOPC技術,在FPGA中集成Altera的嵌入式軟核處理器NiosⅡ和其他外設,將硬件系統與軟件集成在單一可編程芯片中,從而實現片上的系統級設計。系統框圖如圖2所示[4],由DDS基本單元(由頻率控制字,相位累加器,ROM,DAC,LPF 構成),FPGA 外部硬件資源(撥扭開關 SWITCH、鍵盤 KEY、LCD12864)和 NiosⅡ處理器系統等構成了基本電路。四位撥扭開關選擇輸出波形,鍵盤控制輸出波形信號頻率,LCD12864顯示波形信號參數,各硬件模塊之間的協調工作通過NiosⅡ微處理器在圖形化開發環境NiosⅡIDE下用C語言來編程實現控制。

圖2 系統結構示意圖Fig.2 System structure schematic

3 各模塊設計

3.1 波形數據存儲方式

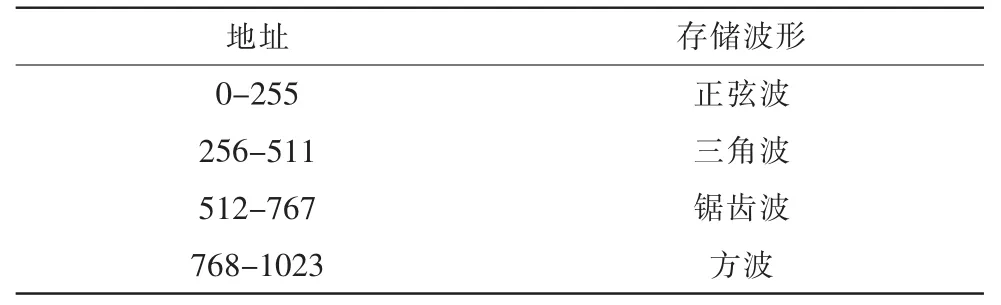

通過對DDS基本原理的分析得知只需更換波形存儲器中的波形采樣數據,就可以得到所需波形的信號。波形數據存儲方式包括順序存儲方式和間隔存儲方式[5],本設計采用順序存儲方式將方波,三角波,正弦波,鋸齒波4種波形采樣數據全部依次存儲在一個查找表里,數據分布情況如表1所示。通過改變尋址首地址,并在該波形數據存儲地址范圍內循環尋址,從而實現對所需信號波形的輸出。具體實現方法在累加控制模塊中有介紹。

表1 查找表數據分布圖Tab.1 Look-up table data distribution

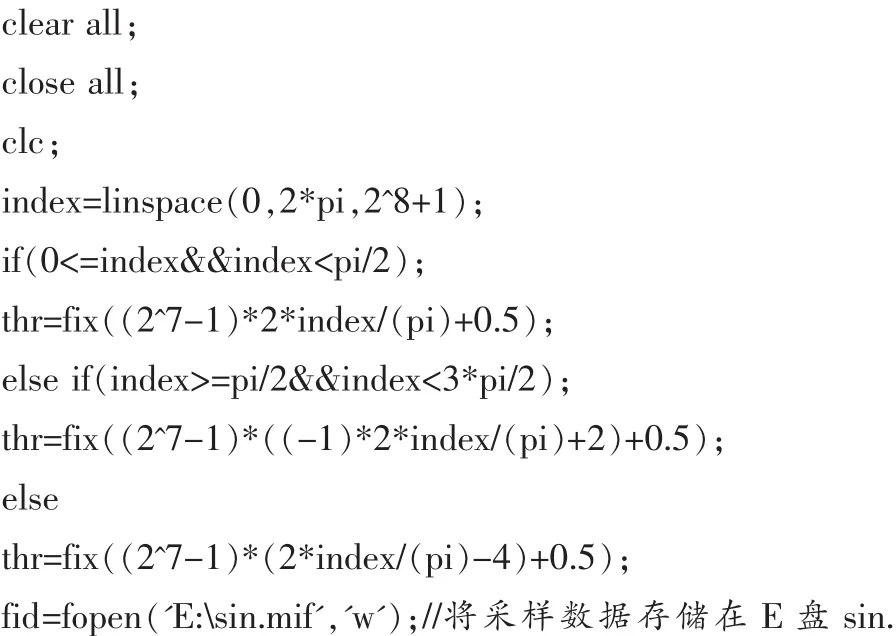

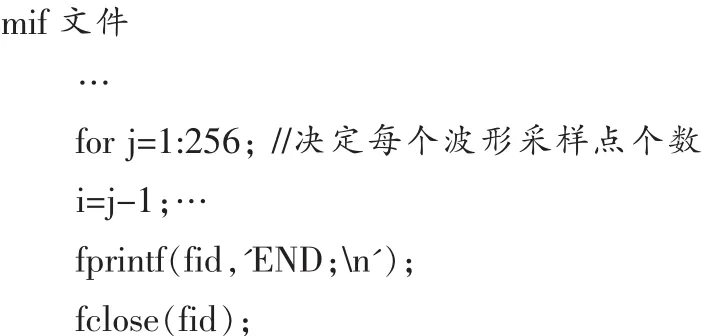

DDS模塊中的波形數據存儲器是用QuartusⅡ中的MegaWizard Plug_In Manager工具添加的LPM_ROM IP核,此存儲器ROM是用波形存儲文件.mif進行初始化,波形數據可以用matlab等工具生成,用matlab生成4種波形的波表數據程序如下:

由以上代碼生成的.mif文件即可在E盤目錄下找到,將.mif文件加載到ROM中,實現對ROM的初始化。

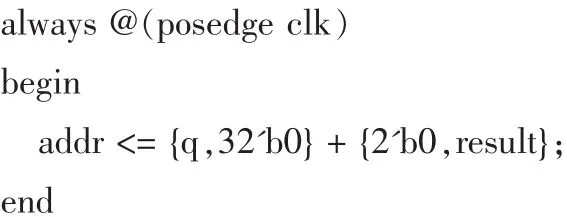

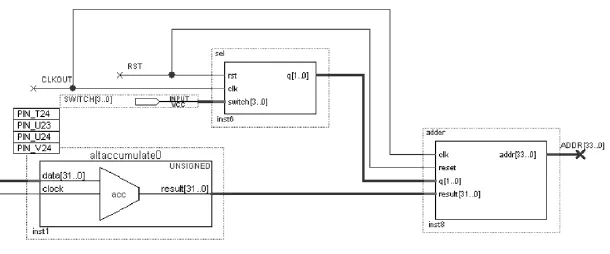

3.2 累加控制模塊

累加控制模塊如圖3所示,為了實現波形選擇性輸出,本設計在累加控制部分增加了選擇器,即圖3的sel模塊,作為系統尋址地址的高兩位,實現對波形查找表的范圍選擇功能。累加器Altaccumulate0的輸出做為累加控制模塊的低32位的輸出,實現在指定范圍內對查找表進行尋址。此設計方法相當于做了一個多路數據選擇器 。四位撥扭開關作為sel模塊的輸入控制,將尋址地址轉換成所需波形首地址,即可實現對波形選擇的控制。Adder模塊將sel和Altaccumulate0模塊輸出進行位拼接運算。其部分代碼如下:

設計中為了節省ROM的容量而采用相位截斷的方法,取累加器輸出的高十位作為ROM的尋址地址來進行查表。

3.3 LCD 12864 IP核設計

對于Altera SOPC Builder未提供的一些外設接口模塊,用戶可以通過自定義邏輯方法在 SOPC設計中添加自己開發的IP核,通過Avalon的讀寫時序對各個設備進行操作。本設計通過構建 IP核來直接控制NiosⅡ和LCD12864的接口,按照指定的時序將波形參數顯示在LCD上[6]。在SOPC Builder中自己定義component,并把液晶顯示模塊看成外部存儲器,直接做成Avalon總線Slave設備,IP核設計包含軟件部分和硬件部分,需要寫HDL模塊,定義控制狀態、數據寄存器和控制位,描述組件與Avalon總線的接口以及組件與液晶屏的接口。系統編輯器從文件中讀取I/O信號和參數信息。其次對LCD模塊進行初始化,由于SOPC Builder中的LCDl2864控制模塊已經考慮了LCD的讀寫時序,所以使用NIOSⅡIDE進行LCD驅動和控制時只需對LCD進行初始化[7]。

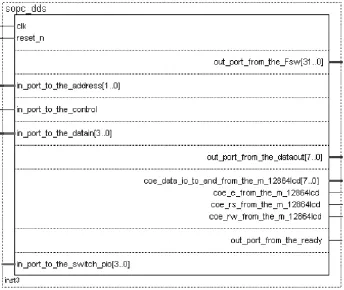

3.4 NiosⅡ嵌入式處理器系統

NiosⅡ是Altera針對其FPGA設計的嵌入式軟核處理器,它與其他IP核可構成SOPC系統的主要部分。它具有靈活的自定義指令集和自定義硬件加速單元,以及圖形化開發環境NiosⅡIDE[2]。經由SOPC Builder生成NiosⅡ嵌入式處理器系統,其CPU模塊框圖如圖4所示。

圖3 累加控制模塊Fig.3 Accumulate control module

圖4 CPU模塊框圖Fig.4 CPU module diagram

利用NIOSⅡIDE開發工具完成所有軟件開發任務,系統接收撥扭開關掃描模塊發來的4位掃描碼,根據掃描碼數值的不同進入不同的子程序,然后再通過FPGA的鍵盤掃描模塊向NIOSⅡ處理器發送鍵盤掃描碼,軟核處理器根據接收到的掃描碼產生相應的信號數據以及控制信號,并通過 PIO傳送給FPGA中的 DDS模塊 ,實現頻率控制字的變化,即輸出頻率可調,并將信號數據顯示在LCD上。同時DAC器件將DDS產生的8位信號數據進行數模轉換,從而產生頻率可調的方波、三角波、正弦波、鋸齒波[8]。

4 結束語

該信號源能夠很好地滿足對不同波形、不同頻率的信號的需求,具有很強的實用性,并且可以方便地通過液晶顯示器直觀地觀察到波形信號的參數信息。由FPGA實現的DDS信號發生器不僅可實現頻率可調波形變換且具有頻率切換快,信號的質量和精度高于模擬方式的特點。

[1]張金波,湛向,劉二偉,等.基于DDS/SOPC的多路可調諧波信號發生器[J].電力自動化設備,2008(11):74-78.ZHANG Jin-bo,ZHAN Xiang,LIU Er-wei,et al.The wide adjustable harmonic signal generator based on DDS/SOPC[J].Electric Power Automation Equipment,2008(11):74-78.

[2]方媛,李勇,李智君,等.基于NIOSⅡ軟核處理器的通信信號源SOPC設計[J].科學技術與工程,2007,7(12):2959-2963.FANG Yuan,LI Yong,LI Zhi-jun,et al.The SOPC design of communication signal source based on NIOSⅡsoft processors[J].Science Technology and Engineering,2007,7(12):2959-2963.

[3]黃小翰.基于FPGA的多功能波形發生器的設計[J].價值工程,2010(9):232-233.HUANG Xiao-han.The design of multifunctional waveform generator based on FPGA[J].Value Engineering,2010(9):232-233.

[4]李全利,王峰.基于Nios II的信號發生器[J].自動化技術與應用,2007,26(1):96-98,110.LI Quan-li,WANG Feng.The signal generator based on Nios II[J].Techniques of Automation and Applications,2007,26(1):96-98,110.

[5]李志鵬,郭勇,沈軍.基于DDS技術實現信號發生器[J].微計算機信息,2007,23(7-1):175-177.LI Zhi-peng,GUO Yong,SHEN Jun.The signal generator based on DDS technology[J].Microcomputer Information,2007,23(7-1):175-177.

[6]馬品宏.基于SOPC的任意波形發生器的研究與開發[D].大連:大連理工大學,2006.

[7]葛遠香,胡開明.基于NIOSⅡ的LCD控制器和矩陣鍵盤的IP核的設 計方法 [EB/OL]. (2010-08-16).http://www.elecfans.com/emb/arm/20100816221785.htm1.

[8]倪亮,吳麗敏,趙鵬飛.基于SOPC基本信號產生器的設計與實現[J].電子科技,2011,24(1):89-92.NILiang,WULi-min,ZHAOPeng-fei.The designandimplementation of basic signal generator based on SOPC[J].Electronic Science and Technology,2011,24(1):89-92.