基于ADSP-TS201的著陸雷達恒虛警電路實現(xiàn)

王浩程,楊春燕,張 豪

(空軍工程大學 信息與導航學院,陜西 西安 710077)

精密進場雷達以飛機作為主要探測目標,地物、云雨雪等都被視為雜波干擾,所以在設計中總是盡可能地采取措施抑制干擾,提高雷達發(fā)現(xiàn)目標的能力。為了使設備正常工作,干擾電平允許變化范圍通常比較小。雷達內部的熱噪聲、地物、氣象雜波的干擾電平很大,其變化有時高達幾十分貝。為了設備能穩(wěn)定正常的工作,必須保持虛警概率基本不變,因此,信號處理分機增加了恒虛警(CFAR)處理電路[1]。

近年來,CFAR方法出現(xiàn)了很多,然而,真正應用的并不多。通過對4種具有代表性方法的比較,得到一種可以實現(xiàn)且檢測性能較好的恒虛警處理方法。

1 恒虛警檢測方法

恒虛警檢測方法就是采用自適應門限代替固定門限,而且此適應門限能隨著被檢測點的背景噪聲、雜波和干擾的大小自適應地調整。如果背景噪聲、雜波和干擾大,自適應門限就調高;如果背景噪聲、雜波和干擾小,自適應門限就調低,以保證虛警概率恒定。所以設計雷達恒虛警檢測器的關鍵是獲取這種自適應門限的方法[2]。

常見的恒虛警檢測器有4種,單元平均恒虛警 (CACFAR)檢測器提供了對非起伏和斯威林起伏目標的最優(yōu)或準最優(yōu)檢測,但是,在雜波邊緣要引起虛警率的上升,將導致檢測性能下降,在雜波邊緣的檢測性能會明顯變壞。平均選小恒虛警檢測器(SO-CFAR)是就干擾目標提出的,但也僅在大干擾目標的情況下有效,而當兩個相差不大的大干擾出現(xiàn)在檢測單元兩側時,性能惡化,所以這種方案的局限性很大。平均選大恒虛警檢測器(GO-CFAR)可以明顯消除普通單元平均對數(shù)恒虛警電路在雜波過渡區(qū)內存在的虛警增加的現(xiàn)象。單目標、均勻雜波背景情況下,GO-CFAR是這幾種方法中最優(yōu)的[3-4]。

2 恒虛警電路設計

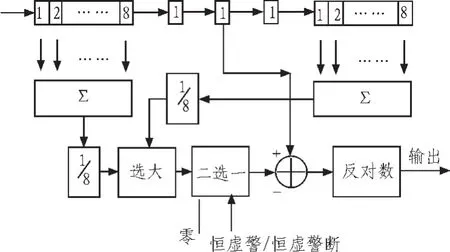

著陸雷達恒虛警電路采用平均選大恒虛警檢測方法。恒虛警檢測器的參考單元N取l6,如圖1所示。

圖1 恒虛警電路圖Fig.1 CFAR circuit diagram

設計思路是:將檢測點的幅度減去噪聲的平均值(由虛警電位器調整),再將相鄰七個距離單元的信號進行相關運算,若超出虛警門限,則作為有用目標信號處理,輸出高電平,打開實時信號選擇支路;若低于虛警門限,則作為虛警信號處理,輸出低電平,關閉實時信號選擇支路,阻止視頻信號輸出。圖中,被測信號單元兩側各空一個單元,使目標信號本身不參與雜波均值的估計,這樣可以避免被測單元對雜波強度估計值的影響。

3 實現(xiàn)電路

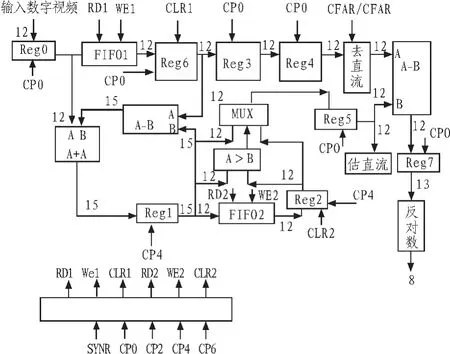

ADI公司的ADSP TS201處理器片內集成大容量存儲器,兼有ASIC和FPGA的信號處理性能,能夠支持本次設計的實現(xiàn),其實現(xiàn)電路組成如圖2所示[5]。

圖2 實現(xiàn)電路Fig.2 Application circuit

其中先出寄存器模塊FIFO 1存貯前8個距離單元的回波數(shù)據(jù),而先進先出寄存器模塊FIFO2存貯后8個距離單元的回波數(shù)據(jù)之和的平均值。輸入數(shù)據(jù)進入芯片內部,經累加電路(采用加新值,減舊值的方案),前8個距離單元數(shù)據(jù)之和,在CP4脈沖到來時打入寄存器Rag1中,同時后8個距離單元數(shù)據(jù)之和的平均值也由FIFO2中取出,并存在寄存器Rag2中,二者經選大后大者存在寄存器Rag5中,同時被測數(shù)據(jù)也存入寄存器Rag4中,二數(shù)據(jù)經減法運算,其差送出芯片,再經反對數(shù)電路,得到恒虛警輸出。

8個距離單元的數(shù)據(jù)累加器,在零距離的前8個距離單元時間內要完成初始化過程:加新值減去零,這樣經過8個距離單元,累加寄存器內將保持著前8個距離單元的數(shù)據(jù)之和,從第9個距離單元開始,才進行“加新減舊”運算,這樣使累加器和寄存器內總是保存當前最新8個距離單元的數(shù)據(jù)之和。這祥,只有經過l9個距離單元,后8個距離單元數(shù)據(jù)之和的平均值才有效。故FPGA內部需產生兩個清零信號:FIFO1輸出寄存器清零信號為CLR1,F(xiàn)IFO2輸出寄存器清零信號為CLR2。雷達的航向天線和下滑天線是以1 Hz的頻率交替工作的。當天線轉換時,其存貯器內仍保留著另一個天線掃描時的數(shù)據(jù),這些數(shù)據(jù)需要廢棄,而要存貯掃描后的新數(shù)據(jù),且要不斷地更新。當接收到天線轉換的信息時,要產生兩個清零信號:CLRl和CLR2,分別對兩個存貯器清零。

估直流電路是在雷達休止期內,取16個距離單元,電平在恒虛警和非恒虛警兩種工作狀態(tài)時,直流電平基本不變。

4 仿真驗證

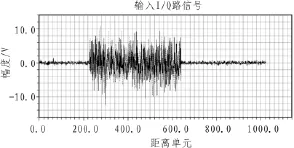

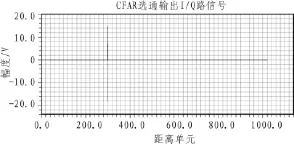

運用針對ADI公司的DSP器件而專門開發(fā)的平臺—Visual DSP++進行編程仿真,驗證所設計的恒虛警電路功能[5]。輸入一組雷達原始數(shù)據(jù),對其進行處理,根據(jù)輸出的波形驗證此檢測器。輸入信號波形如圖3所示,輸出信號波形如圖4所示。

圖3 輸入信號波形Fig.3 Waveform of input signal

圖4 輸出信號波形Fig.4 Waveform of output signal

由圖3可知,目標信號湮沒在各種噪聲中,必須經過濾波處理才能得到所需信號波形。將雷達信號數(shù)據(jù)輸入仿真系統(tǒng),從圖4輸出信號波形上看,波形較為理想,達到了預期目標。

通過仿真驗證,發(fā)現(xiàn)輸出信號已經將雜波大部分濾除,所得信號基本與所需目標信號一致,結果比較理想,說明設計比較合理[6]。

5 結束語

文中著重介紹了一種著陸雷達恒虛警處理的實現(xiàn)方法,并在FPGA上進行了電路設計,最后通過仿真進行了驗證,取得了較好的效果。

[1]丁鷺飛,耿富錄.雷達原理[M].西安:西安電子科技大學出版社,2006.

[2]何友.雷達自動檢測與恒虛警處理 [M].清華大學出版社,1999.

[3]都基焱,胡軍,張百順.七種恒虛警率處理方案及性能分析[J].現(xiàn)代雷達,2004,26(4):47-50.

DU Ji-yan,HU Jun,ZHANG Bai-shun.Performance analysis of seven kinds of CFAR processing methods[J].Modern Radar,2004,26(4):47-50.

[4]Petrovic M M,Dimitrijevic D D,Kostic A T.Sampling rate influence on detection performance of CFAR algorithms implemented in radar extractor[C].TELSIKS 2001:57-60.

[5]羅勇江,劉書明,肖科.VisualDSP++集成開發(fā)環(huán)境實用指南[M].北京:電子工業(yè)出版社,2008.

[6]劉書明,羅勇江.ADSPTS20XS系列DSP原理與應用設計[M].北京:電子工業(yè)出版社,2007.