基于PCI Express接口的高速數據傳輸系統設計

周曉波,夏 敏,鄒浩杰

(北京交通大學 電子信息工程學院,北京 100044)

高速鐵路列車具有很高的運行速度,其無線通信網絡需要適應高速的移動環境,支持列車最高速度500 km /h和平均速度350 km /h的運行情況。較高的運行速度會增加無線通信數據傳輸的誤碼率,并且會造成信號的衰落率較高,即信號的變化較快。因此需要快速跟蹤信道參數的變化,以降低無線傳輸的誤碼率。

對信道參數的跟蹤面臨高速數據的采集和傳輸問題。目前,國內大部分的高性能數據采集卡都是基于PCI、CPCI和VME等總線,最高傳輸速率難以超過400 Mit/s。為解決傳統數據傳輸的瓶頸,提出基于PCI Express接口的高速傳輸系統設計方案。

1 PCI Express拓撲和鏈路結構

經簡化的PCI Express系統拓撲結構中包括:根聯合體、交換器、終端和橋,如圖1。每條虛線均代表兩個PCI-E(PCI Express)設備之間的一條連接,這種連接稱為鏈路。

(1)根聯合體用于初始化整個PCI-E結構并配置每條鏈路,將中央處理器(CPU)與交換器、終端和PCI-E to PCI橋這3項功能之中的一個或多個相連接。

(2)交換器用于將數據向下游路由并傳送至多個PCI-E端口,以及從每個獨立端口將數據向上游路由并傳送至單一的根聯合體。PCI-E交換器也可以從一個下游端口靈活地向另一個下游端口路由并傳送數據,不再局限于傳統PCI系統所要求的嚴格的樹形結構。

(3)終端通常駐留在應用內,用于在系統中將應用連接到PCI-E網絡。終端具有請求和完成PCI-E事務處理的功能。

(4)PCI-E to PCI橋用于將PCI-E與其他PCI總線標準(如PCI/PCI-X)相連接,適用于同時采用了這些體系架構和PCI-E的系統。

圖1 PCI Express系統拓撲結構

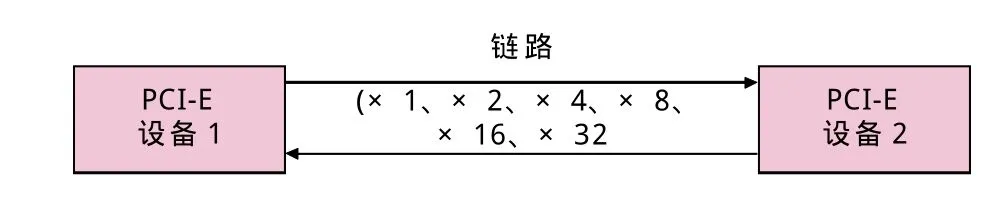

PCI Express設備之間為鏈路形式的互連,如圖2。在每個方向上都可以有×1、×2、×4、×8、×16 或×32 個信號對, 這些信號對稱為通道,每條通道在每個方向上的發送和接收速率為2.5 Gbit/ s。

圖2 PCI Express鏈路結構

2 系統設計

2.1 系統分析

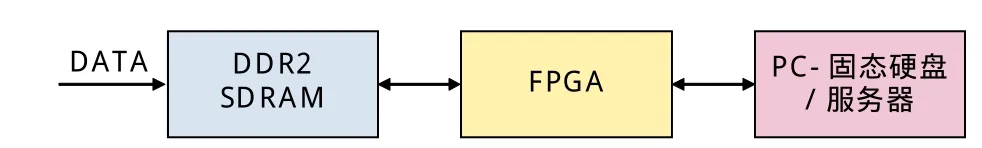

數據流向如圖3,其中,第2代雙倍數據率同步動態隨機存取存儲器(DDR2 SDRAM)對數據(DATA)進行緩存,FPGA主要完成數據的處理和傳輸,PC—固態硬盤/服務器,主要完成對數據的存儲和后期處理。

圖3 數據流向

FPGA是在復雜可編程邏輯器件(CPLD)的基礎上發展起來的新型高性能可編程邏輯器件,集成度很高,可以完成極其復雜的時序與組合邏輯電路功能,適用于高速和高密度的高端數字邏輯電路設計領域。高性能的固態硬盤提供極大的存儲空間或者利用服務器通過廉價冗余磁盤陣列(RAID)技術提供近乎無限的存儲空間, 而且使得數據存取速率成倍提升, 又有充足的運算資源進行數據采集的后期處理。本文主要討論采用PCI Express接口實現將采集的高速數據傳輸到固態硬盤的技術,以及高速數據傳輸系統的設計。

2.2 設計方案

本設計方案中采用模塊化設計思想。為提高設計性能,降低產品開發成本,縮短設計周期,采用IP核實現PCI Express協議和對DDR2 SDRAM的控制。

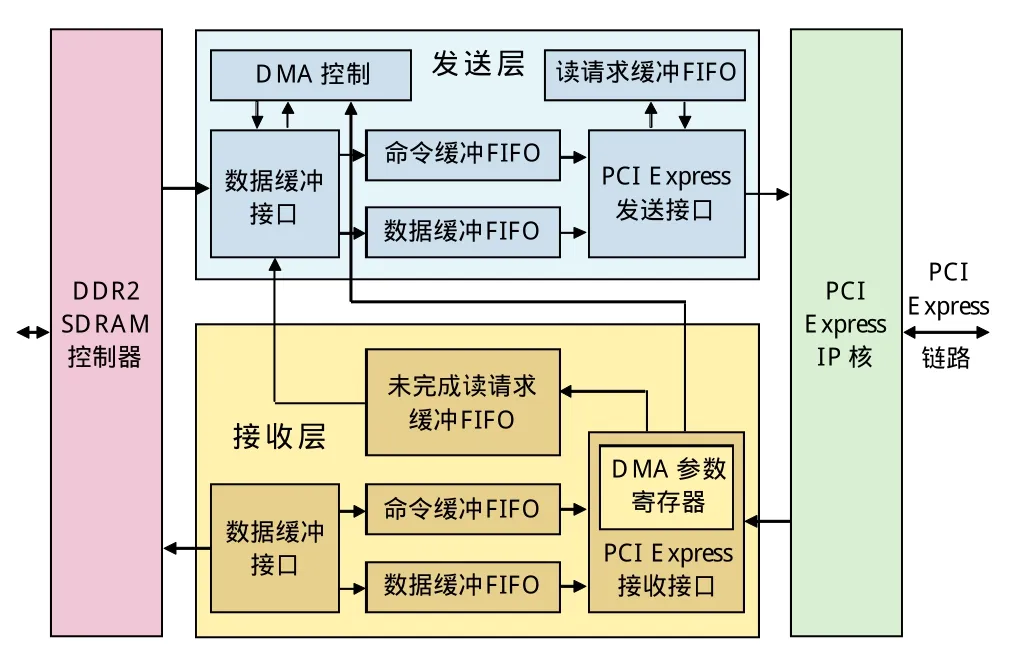

對設計方案進行如圖4的模塊劃分。在可編程邏輯器件領域,IP(Intellectual Property)核是指將一些數字電路中常用但比較復雜的功能模塊,設計成參數可修改的模塊,讓其他用戶可以直接調用這些模塊,從而簡化設計,縮短開發周期。

圖4 模塊劃分

2.3 各模塊實現功能

2.3.1 DDR2 SDRAM控制器

DDR2 SDRAM控制器是通過行地址選擇(RAS#)、列地址選擇(CAS#)、寫使能(WE#)、時鐘使能(CKE)和芯片選擇(CS#)一組控制信號線組合成控制命令,完成對DDR2 SDRAM的操作,如寫命令、讀命令和空操作、加載模式寄存器、自動刷新、預充電、選擇組激活行等。

2.3.2 PCI Express模塊

PCI Express采用數據包方式在系統應用層內傳輸數據,并用于數據接口與PCI-E設備的各層之間。應用層用于發起事務處理,而事務處理層用于將應用程序的請求轉換成PCI-E事務處理包。數據鏈路層用于為這個包添加一個序列編號和鏈路循環冗余校驗碼(LCRC)。數據鏈路層還確保了雙向事務處理能夠正確地得到接收。最終,物理層能夠通過PCI-E鏈路發送事務處理。

PCI Express IP核能夠實現PCI Express接口協議中處理層、數據鏈路層和物理層的邏輯功能。

2.3.3 發送層和接送層

發送層和接送層主要完成對傳輸數據的緩沖和處理,實現數據的發送和接收功能。

2.3.4 數據緩沖接口模塊

數據緩沖接口模塊主要實現與前端接口對接,并對數據進行合并或者拆分的處理。檢查在接收層中未完成讀請求緩沖FIFO中是否還有未完成的讀請求命令,如果有則通過DDR2 SDRAM控制器讀取DDR2 SDRAM中的數據并將相應的命令和數據分別寫入命令緩沖FIFO和數據緩沖FIFO;在接收層中,通過命令緩沖FIFO和數據緩沖FIFO與DDR2 SDRAM控制器進行交互,完成數據的讀取和寫入。

2.3.5 DMA控制模塊

DMA控制模塊使得外部設備可以發起對存儲器或其他外部設備進行直接讀和寫的操作,進行數據交換,不需要經過CPU,減少中間環節,提高傳輸速度。本設計方案中,通過設置接收層中的DMA參數寄存器,DDR2 SDRAM可以直接對存儲器進行DMA讀和寫操作 。

2.3.6 數據緩沖FIFO模塊

數據緩沖FIFO模塊主要實現對傳輸數據的緩沖以及DDR2 SDRAM和PCI Express IP核之間的跨時鐘域,使得數據傳輸同步,不丟失數據。

2.3.7 命令緩沖FIFO

命令緩沖FIFO模塊在接收層中將對從PCI Express IP核中接收到的數據包分解出的寫請求和完成請求命令進行緩存,在發送層中對讀請求命令、寫請求命令、完成請求命令進行緩存。

發送層的PCI Express發送接口通過命令緩沖FIFO和數據緩沖FIFO形成數據包送入PCI Express IP核,接收層的PCI Express接收接口則對來自PCI Express IP核的數據包進行分解,并將相應的命令和數據送入未完成讀請求FIFO、命令緩沖FIFO、數據緩沖FIFO或者發送層的DMA控制模塊。

2.4 驗證與仿真

利用Quartus II 聯合ModelSim對設計的相應模塊及整個方案進行仿真驗證。

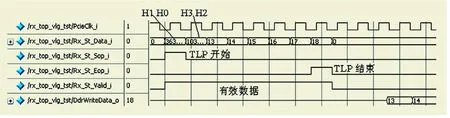

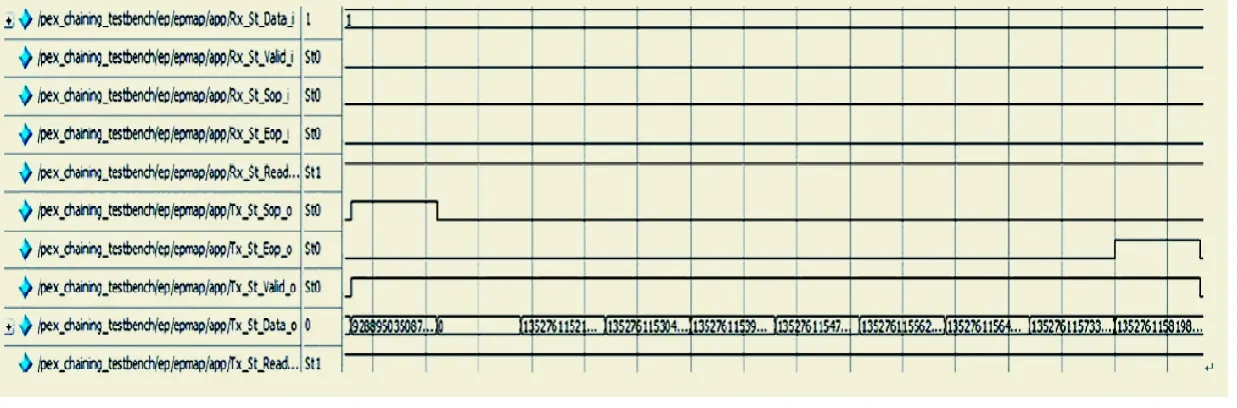

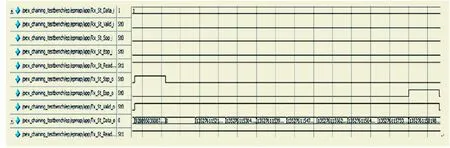

發送層和接收層數據時序如圖5和圖6。其中,TLP為數據包,H代表數據包的頭信息。

圖5 發送層時序圖

圖6 接收層時序圖

采用PCI Express IP核實現了PCI-E設備層中的處理層、數據鏈路層和物理層的邏輯功能。通過PCI Express IP 核提供的接口信號,實現數據的發送和接收。應用層只將數據封裝成數據包TLP或者對數據包TLP進行解析。

從圖5和圖6中可知,發送層和接收層的數據時序符合PCI Express1.0的協議規范中對處理層數據包TLP格式的要求。

對DDR2 SDRAM控制器、發送層、接收層、PCI Express IP核整個方案進行仿真與驗證,編譯庫和模塊文件,下載設計文件,對相關寄存器進行配置、建立鏈路訓練。在發送端和接送端截取相關數據信號的時序圖,如圖7和圖8。

圖7 發送端一幀數據

圖8 接收端一幀數據

通過圖7和圖8可以看出,除去數據包的頭信息和尾信息,發送端的一幀數據和接收端的一幀數據相同,因此表明發送和接收的數據一致,保證了數據傳輸的完整性。

3 結束語

第三代I/O互連總線PCI Express 是解決數據傳輸數據瓶頸問題的關鍵途徑,有著廣泛的應用前景。本文設計并實現了基于PCI Express 接口的高速數據傳輸系統,采用PCI Express1.0協議,目前可實現2.5 Gbit/ s的數據傳輸速率, 對方案進行改進,理論上可獲得5 Gbit/ s甚至更高的

數據傳輸速率。本系統方案已應用于高速數據采集卡中,且運行穩定可靠。

[1]夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2003.

[2]Ravi Budruk, Don Anderson, Tom Shanley.PCI Express系統體系結構標準教材[M].田玉敏,王 崧,張 波. 北京:電子工業出版社,2005.

[3]PCI-SIG. PCI ExpresR. 2.0Base Specification Revision 0.9[EB/OL]. http://www.pcisig.com/specifications/pciexpress/.

[4]Altera Corporation.PCI Express to External Memory Reference Design [EB/OL]. http://www.altera.com/support/refdesigns/ip/interface/ref-pciexpress-ddr3-sdram.html? GSA_pos=1&WT.oss_r=1&WT.oss=PCIExp ress to External Memory Reference Design.

[5]Altera Corporation. External Memory Interface Hand-book Volume 3—Section I.DDR and DDR2 SDRAM Controllerswith ALTMEMPHY IP User Guide [EB/OL]. http://www. altera.com/literature/hb/external memory/emi_ip.pdf GSA_pos=1&WT.oss_r=1&WT.oss=External Memory Interface Handbook Volume.

[6]Altera Corporation.PCI Express Compiler User Guide [EB/OL]. http://www.altera.com/literature/ug/ug_pci_express.pdf?GSA_pos=1&WT.oss_r=1&WT.oss=PCI Express Compiler User Guide.