高速同步串行接口的設計與實現

雷淑嵐,薛忠杰,2

(1.江南大學 物聯網學院,江蘇 無錫214122;2.中國電子科技集團公司第58研究所,江蘇 無錫214061)

0 引 言

近年來,DSP發展迅速,特別是集成了各種功能外設的DSP芯片的廣泛應用,對DSP通信接口的性能要求也越來越高。串行接口可以劃分為同步串行接口和異步串行接口,同步串行接口的基本協議相對比較簡單,易于實現。現有的同步串行接口的傳輸速率不高,且不夠靈活,應用范圍不廣泛[1]。

為了提高傳輸速率,增強兼容性,高速同步串行接口支持全雙工和半雙工同步通信,通信速率、通信數據寬度、時鐘極性、時鐘相位和數據移位方向均可配置,從而能夠和與串行外設接口 (SPI)兼容的器件或使用其他同步串口的器件進行通信。主要應用在DSP處理器和外設之間的通信,采用主/從模式也可以應用在多處理器間的通信。

1 高速同步串口的設計

1.1 整體架構設計

SSC接口分為5個部分[2]:寄存器配置模塊,時鐘產生模塊,數據緩沖寄存器模塊,移位控制邏輯模塊,中斷控制模塊,其整體架構如圖1所示。

CPU通過總線時鐘bus_clk_i、復位信號bus_reset_n_i、地址線bus_a_i、數據線bus_d_i和bus_d_o完成對寄存器的初始化及控制,數據讀寫和狀態監控。寄存器配置單元通過對寄存器的讀寫實現SSC接口的可配置。在時鐘產生模塊中,總線時鐘通過分頻與外設的高速、低速時鐘匹配,時鐘極性和時鐘相位的可配置,使SSC接口能夠與多種同步串口通信,ssc_sh_clk_o為主模式下的時鐘輸出,ssc_sh_clk_i為從模式下的時鐘輸入。移位控制邏輯模塊按照規定的時序邏輯,將待發送的并行數據轉換成串行數據通過ssc_ms_out_o或ssc_sl_out_o發送出去,將通過ssc_ms_in_i或ssc_sl_in_i采樣到的串行數據轉換成并行數據送入接收緩沖寄存器。利用數據緩沖寄存器實現數據發送和接收過程中的雙緩沖。中斷控制單元處理SSC接口的中斷源,ssc_t_irq_o是發送開始中斷請求,ssc_r_irq_o是發送結束中斷請求,ssc_e_irq_o是數據傳輸出錯中斷請求。信號ssc_slsi_i[7:1]和ssc_slso_o[7:0]是SSC接口從模式輸入選擇線和從設備選擇線,在從模式下,SSC接口通過ssc_slsi_i[7:1]被主設備選中;在主模式下,SSC接口通過ssc_slso_o[7:0]選中一個或多個從設備,實現和多個從設備通信。

圖1 SSC接口整體架構

1.2 模塊的結構設計

1.2.1 寄存器配置單元

寄存器配置單元主要利用多參數進行設置,對整個SSC接口實現可配置。寄存器主要包括控制寄存器(CON)、狀態寄存器 (STAT)、波特率定時/重載寄存器(BR)、從設備選擇寄存器 (SLSO)、從模式輸入選擇寄存器[3](SLSIS)。

控制寄存器中CON.PH、CON.PO的不同組合可以設置4種不同的時鐘方式;CON.MS選擇主/從模式;CON.EN選擇SSC接口是否使能,SSC只有在被使能時才能傳輸數據;CON.HB選擇數據傳輸時先傳輸低位還是先傳輸高位;CON.BM [3:0]配置不同的數據寬度,范圍從0001B-1111B(2到16位)15種不同的選擇;CON.LB選擇SSC工作在全雙工模式還是半雙工模式;CON.TEN、CON.REN、CON.PEN、CON.BEN分別是SSC接口發送出錯、接收出錯、相位出錯和波特率出錯的使能位,為0時,表示該出錯中斷被禁止,為1時,表示該出錯中斷被使能。在本設計中,通過添加PO、PH、HB、BM、LB等參數,實現SSC接口的可配置,增強兼容性,使SSC接口適用于不同的應用場合。

狀態寄存器中STAT.BSY為0時表示空閑,為1時表示正在進行數據傳輸;STAT.TE、STAT.RE、STAT.PE、STAT.BE分別是SSC接口發送出錯、接收出錯、相位出錯和波特率出錯的標志位,當檢測到錯誤時,對應的標志位被置1。

通過波特率定時/重載寄存器產生不同的波特率。

從設備選擇寄存器SLSO是SSC作為主設備時對從設備的選擇。當SLSO [7:0]中SLSOn置1時,對應的信號ssc_slso_o[n]有效,即選中相對應的從設備。

從模式輸入選擇寄存器SLSIS是SSC作為從設備時輸入線的選擇。在從模式下,SSC有7種從輸入選擇,SLSIS[2:0]為初始值000B時,說明SSC沒有從模式輸入線選擇功能,此時的SSC只能作為唯一的從設備與主設備通信。當SLSIS[2:0]的值為0001B到1111B時,SSC作為從設備,選中相應的從模式輸入選擇線,當主設備使該從模式選擇線有效時,就可以與該SSC進行通信。

1.2.2 時鐘產生單元

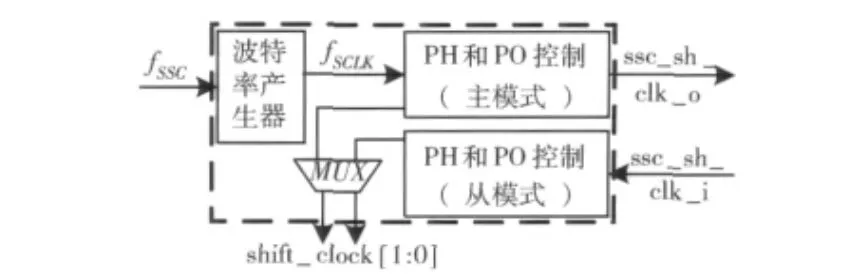

時鐘產生單元[4]如圖2所示,fSSC是總線時鐘頻率,fSCLK是通過波特率產生器對fSSC分頻得到的SSC的工作頻率。

圖2 時鐘產生單元內部結構

時鐘極性PO和時鐘相位PH控制著4種不同的時鐘方式,通過PH和PO的控制,檢測出主/從模式下時鐘邊沿的有效信號,控制數據傳送和采集時刻的時鐘邊沿。shift_clock[1:0]是SSC的數據轉移時鐘,是移位控制邏輯模塊的輸入,其高位是移位時鐘的標志,低位是鎖存時鐘的標志。

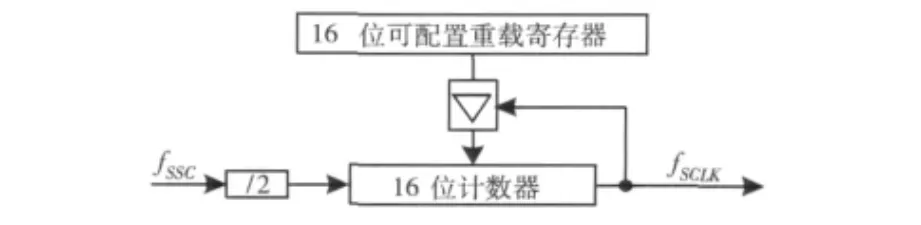

波特率產生器采用的是結構簡單、易于實現的偶數分頻[5],利用圖3中的16位的減法計數器實現。16位可配置重載寄存器 (BR)具有雙重功能,作為波特率定時或可配置重載寄存器。

圖3 波特率產生器

當SSC使能時,讀取BR的值并存儲到16位計數器,計數器進行遞減計數到零時,產生重新讀取BR的請求,接下來繼續讀取BR的值;當SSC被禁止時,可以重新配置BR,寫入重載值。

如果已知重載值為BR_value,則波特率可以通過式(1)計算

當總線接口時鐘頻率fssc=150MHz時,主模式下,BR_value的值為0000h-FFFFh,波特率的范圍可由75.0Mbit/s到 1.14Kbit/s,從模式下BR _value的 值 為0001h-FFFFh,波特率的范圍可由37.5Mbit/s到1.14Kbit/s。

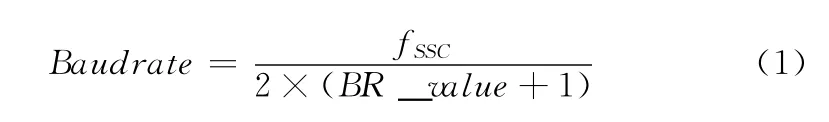

PH和PO的控制使SSC接口可以和不同的同步串行接口之間完成數據的發送和接收。用一個特定的移位時鐘沿(上升或下降)移出數據,同時用另一個時鐘沿鎖存接收到的數據。具體配置如圖4所示[6]。

圖4 時鐘極性和時鐘相位選擇

時鐘極性PO控制著空閑時鐘的電平是1還是0,時鐘相位PH控制著數據收發時的時鐘邊沿。時鐘極性和時鐘相位的可配置,使SSC能夠根據需要完成與不同傳輸協議的器件間的通信,只要相互通信的器件之間設置合適的時序方式,就能保證正常通信。

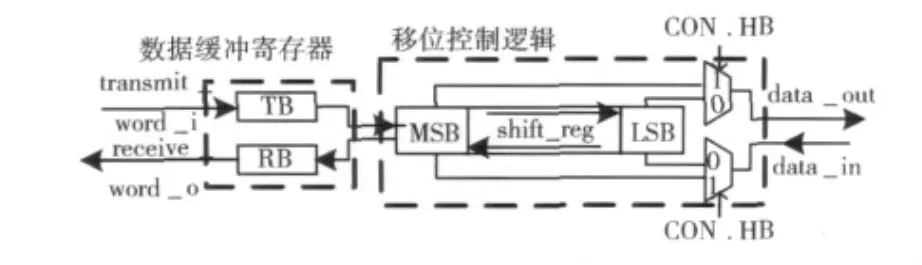

1.2.3 數據緩沖寄存器和移位控制邏輯模塊

如圖5所示[7]:TB是發送緩沖寄存器,RB是接收緩沖寄存器。CON.HB選擇數據移位方向,為 ‘0’時選擇LSB,表明先傳輸低位;為 ‘1’時選擇MSB,表明先傳輸高位。先傳輸LSB,可使SSC接口和同步模式下的SSC器件通信,或與8051的串行接口通信;先傳輸MSB,可使SSC接口和與SPI接口兼容的器件通信。

圖5 數據傳輸通路

移位控制邏輯模塊包含在主/從兩種模式下數據的收發過程,通過控制寄存器CON.MS位的選擇,同一時間只會在一種模式下工作。

SSC數據的發送和接收被同步,所以接收到的數據和發送的數據位數相同。移位控制邏輯模塊將數據發送和數據接收的時刻設為不同的時鐘沿,保證了傳輸數據的正確性。發送行為和接收行為相互交替,每個行為發送或接收一位數據。在移位時鐘shift_clock[1:0]高位移位時鐘標志有效的下一個時鐘沿發送數據,在shift_clock[1:0]低位鎖存時鐘標志有效的下一個時鐘沿接收數據。

移位控制邏輯采用狀態機實現[8],主要有s_shift_init、s_tr_shift、s_again、s_end_mm、s_end_sm這5個狀態,其狀態轉換圖如圖6所示。

圖6 數據傳輸的有限狀態機

其中各個狀態及相互之間的轉換如下[9]:

s_shift_init:空閑狀態。初始化收發移位計數器,并不斷檢測發送緩沖寄存器TB中是否有數據寫入,當檢測到有數據寫入時,移位寄存器一空就將這個數據移入,接下來轉入s_tr_shift狀態;沒有數據寫入,則繼續在s_shift_init狀態。

s_tr_shift:數據收發狀態。根據選擇的數據移位方向,在移位時鐘沿有效時,移位寄存器的最高/低位通過data_out發送后,移位寄存器左/右移一位,在下一個時鐘沿即鎖存時鐘有效時,接收的數據從data_in輸入,填充到移位寄存器的最低/高位,并判斷數據位是否已收發完。若沒有,則狀態機再次進入本狀態執行下一位數據的收發;當收發完成時,如果待發送的數據沒有準備好,則根據主/從模式的選擇進入s_end_mm狀態或s_end_sm狀態;如果待發送的數據已寫入發送緩沖寄存器TB,則轉入s_again狀態。

s_again:連續傳輸數據狀態。把發送緩沖寄存器TB中的數據復制到移位寄存器,重新載入收發數據寬度的值到移位計數器,狀態機進入s_tr_shift狀態完成此次數據的收發。

s_end_mm:在主模式下,結束此次數據傳輸,進入s_shift_init狀態等待下一次收發數據。

s_end_sm:在從模式下,結束收發數據,接下來,狀態機轉入s_shift_init狀態。

把主模式下和從模式下的數據發送和接收的有限狀態機整合成一個狀態機來實現,使得SSC接口結構更加簡單和使用更加靈活。

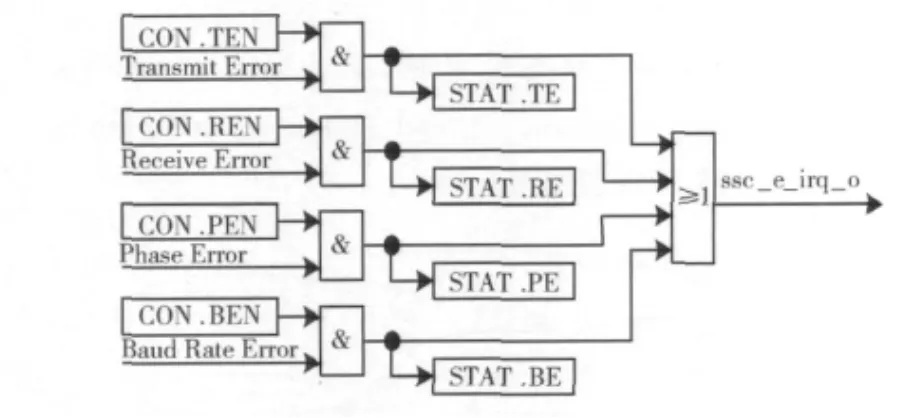

1.2.4 中斷控制單元

SSC接口能夠檢測4種數據傳輸過程中出錯的情況,如圖7所示。在主模式和從模式下均能夠檢測接收出錯[10]和相位出錯,發送出錯[10]和波特率出錯的檢測只適用于工作在從模式下。當檢測到錯誤時,且控制寄存器中對應的出錯使能位有效,對應的出錯標志位會被置位,并激活出錯中斷請求線ssc_e_irq_o。

圖7 SSC接口的檢錯機制

通過檢測狀態寄存器中的出錯標志位確定出錯中斷請求 產 生 的 原 因, 出 錯 標 志 STAT.TE、STAT.RE、STAT.PE、STAT.BE在進入出錯中斷服務程序時不能自動復位,中斷響應后必須由軟件清0。

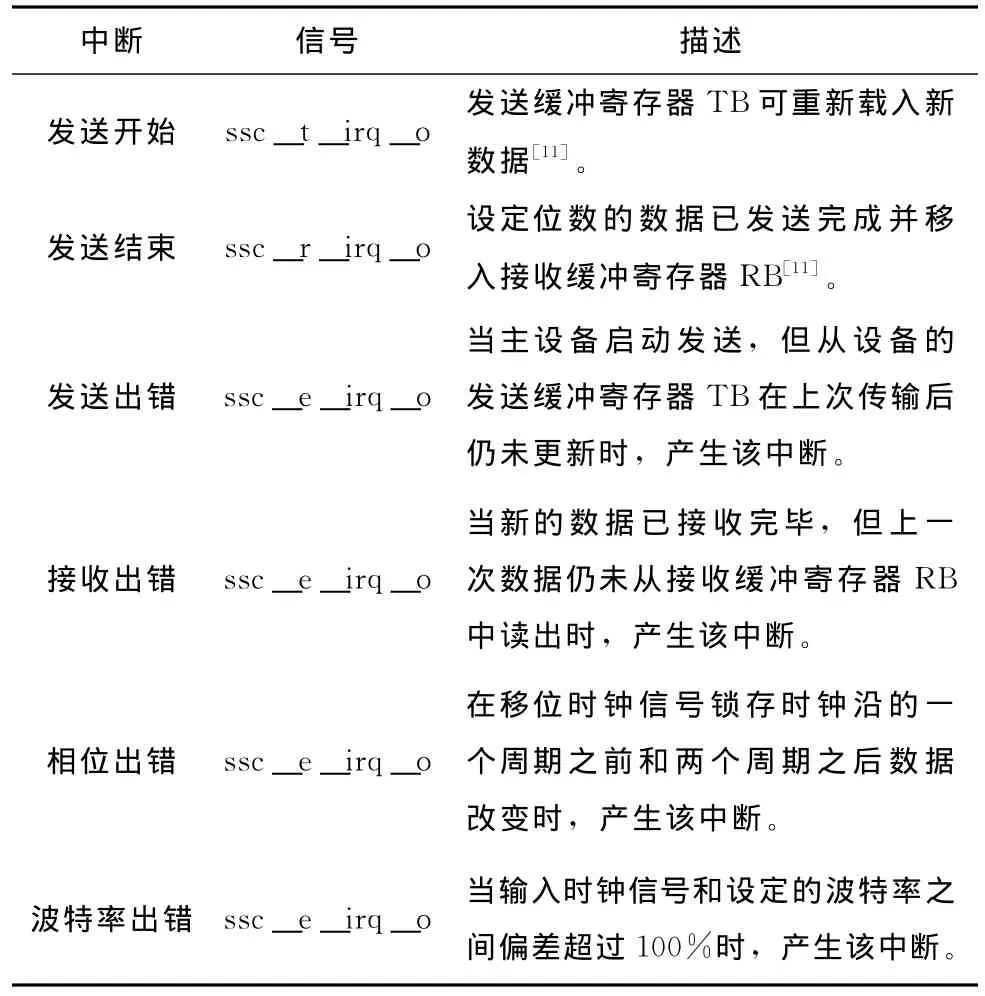

本設計的SSC接口共有6個中斷源,如表1所示。發送開始和發送結束中斷請求在主模式和從模式下均可產生。

表1 SSC接口中斷源

2 功能仿真與性能分析

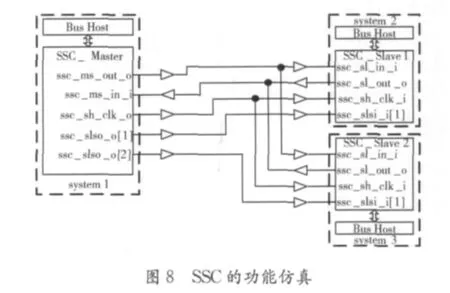

2.1 功能仿真

如圖8所示,通過SSC主從模式的選擇實現系統之間的通信[1,12],SSC接口作為主設備時,通過從設備選擇線ssc_slso_o[7:0]的選擇可以同時和8個從設備通信。

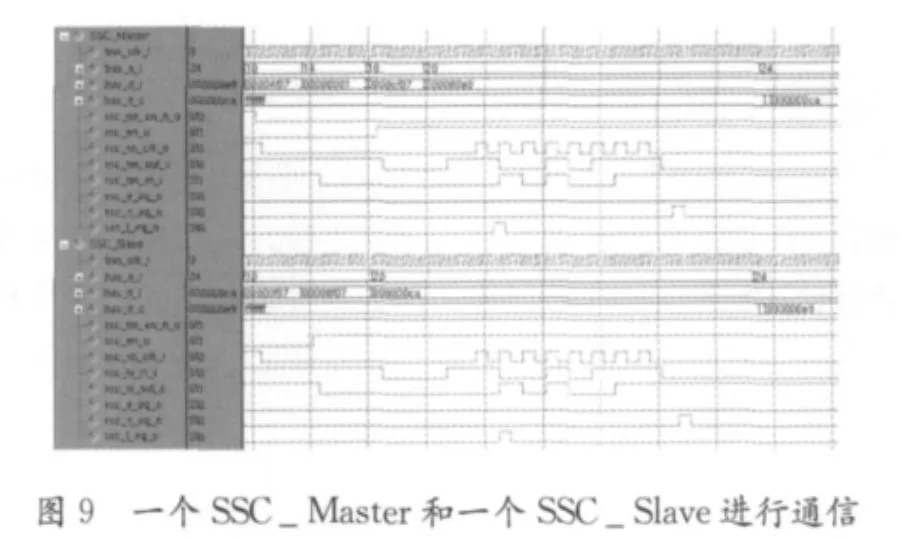

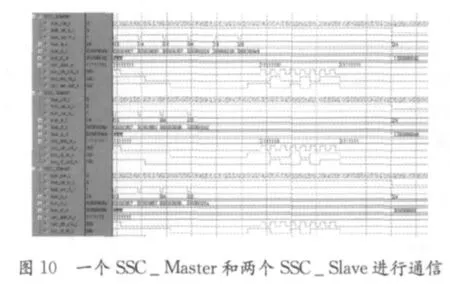

用Mentor公司的 Modelsim仿真工具進行功能仿真[13],圖9是一個SSC_Master和一個SSC_Slave進行通信,其中SSC_Slave的初始值默認從設備沒有輸入選擇功能。圖10是一個SSC_Master和兩個SSC_Slave進行通信,通過使從設備選擇線ssc_slso_o[1]有效,ssc_slso_o[2]無效,則SSC_Master只能和SSC_Slave1進行通信。

ssc_ms_en_n_o是SSC接口的主從選擇標志,為0表示SSC作為主設備,為1表示SSC作為從設備,ssc_en_o是SSC的使能標志,高電平有效。主設備和從設備在全雙工的模式下完成數據傳輸過程。

在從模式下,SSC的工作時鐘頻率不能大于總線時鐘的1/4。在初始化過程中,SSC的主設備實現總線時鐘的四分頻,產生時鐘信號,并作為從設備的時鐘輸入,主設備和從設備的時鐘極性PO和時鐘相位PH配置相同,其值都為0,即在ssc_sh_clk上升沿轉移數據,并選擇數據寬度為8位,從低位開始傳輸,并使能所有中斷請求。

在系統1中,主設備待發送的數據是e9H,在系統2中,從設備待發送的數據是caH。在SSC使能后,ssc_sh_clk的第一個上升沿開始傳送數據,第一個下降沿開始鎖存數據,待8位數據都收發完畢后,主設備的接收緩沖寄存器中的值為caH,從設備的接收緩沖寄存器中的值為e9H,說明SSC主從兩種模式下收發數據的正確。發送開始中斷請求ssc_t_irq_o在第一位數據開始發送后高電平有效,此時TB可重新載入新的數據,結束中斷請求ssc_r_irq_o在數據傳送過程結束后高電平有效,此時數據已發送完成并移入RB,出錯中斷請求ssc_e_irq_o在數據傳送過程中一直無效,說明數據收發完全正確。

SSC可以實現多系統之間的通信,如圖10所示,圖中數據傳輸過程和圖9中的類似。SSC_Master通過從設備選擇寄存器SLSO控制從設備選擇線ssc_slso_o[n]低電平有效。SSC_Slave1和SSC_Slave2都選擇ssc_slsi_i[1]為從模式輸入選擇線。當ssc_slso_o[1]低電平有效,SSC_Slave1的ssc_slsi_i[1]為低電平有效,則SSC_Master選中SSC_Slave1,完成數據傳輸。由于ssc_slso_o[2]無效,沒有選中SSC_Slave2,則SSC_Slave2接收不到主設備發送的數據,在接收緩沖寄存器中的值為初始值00H。當數據收發結束后,所有的ssc_slso_o、ssc_slsi_i被置高電平,可重新選擇從設備進行通信。

2.2 綜合結果與性能分析

該SSC接口采用TSMC 65nm工藝庫,用Synopsys公司的Design Compiler進行綜合,綜合時鐘為150MHz時,數據傳輸速率可達75Mbit/s,面積為11868um2,通過插入clock gating,進一步降低功耗[14],功耗僅為416.8uW。

高速外設總線SPI總線典型的數據傳輸時鐘是1.0MHz到70.0MHz,數據傳輸速率為8.75Mbit/s[15],而本設計中使用先進的工藝,在總線時鐘和數據傳輸速率上都有很大幅度的提高,面積和功耗得到有效降低。

3 結束語

本文完成高速同步串行接口的設計,通過寄存器配置單元實現SSC接口的可配置,使用更加靈活。通過功能驗證可知,該SSC接口能正確收發數據,且總線時鐘為150MHz,在主模式下,數據傳輸速率高達75Mbit/s,功耗為416.8uW,實現低功耗。由于多參數的設置,SSC接口不但可以和兼容SPI模式的接口通信,還可以和使用其他同步接口的器件通信,應用范圍更加廣泛。該同步串行接口已應用到了32位高速DSP中。

[1]Leens F.An introduction to I2Cand SPI protocols[J].IEEE Instrumentation & Measurement Magazine,2009,12 (1):8-13.

[2]CHEN Xi,HUANG Yi.SoC design and source code analysis[M].Beijing:Electronics Industry Press,2008:248-253 (in Chinese). [陳曦,黃毅.片上系統設計思想與源代碼分析[M].北京:電子工業出版社,2008:248-253.]

[3]Simon Srot,SPI master core specification [DB/OL].http://www.opencores.org,Rev.0.6,2007.

[4]Oudjida A K,Berrandjia M L,Liacha A,et al.Design and test of general-purpose SPI Msater/Slave IPs on OPB bus [C].7th International Multi-Conference on Systems Signals and Devices,2010:1-6.

[5]XU Haiming.DSP IC design and research-high-speed synchronous serial peripheral interface[D].Wuxi:Jiangnan University,2009:36-41 (in Chinese).[徐海銘.DSP集成電Z路設計與研究——高速同步串行外設接口 [D].無錫:江南大學,2009:36-41.]

[6]Akos Szekacs,Tibor Szakall,Zoltan Hegykozi.Realising the SPI communication in a multiprocessor system [C].5th International Symposium on Intelligent Systems and Informatics,2007:213-216.

[7]LI Yuefeng.Based on verilog+ HDL design and implementation of SPI reusable IP core[D].Chengdu:Southwest Jiaotong University,2008:23-48 (in Chinese).[李躍峰.基于 Verilog+HDL的SPI可復用IP核的設計與實現 [D].成都:西南交通大學,2008:23-48.]

[8]LIU Bo.Verilog HDL language programming proficiency [M].Beijing:Electronics Industry Press,2007:190-200 (in Chinese).[劉波.精通Verilog HDL語言編程 [M].北京:電子工業出版社,2007:190-200.]

[9]ZHAO Jie.Based on AMBA bus implementation and verification of SPI IP core [D].Hefei:University of Science and Technology of China,2009:36-39 (in Chinese). [趙杰.基于 AMBA總線的SPI協議IP核的實現與驗證 [D].合肥:中國科學技術大學,2009:36-39.]

[10]Oudjida A K,Berrandjia M L,Liacha A,et al.FPGA implementation of I2C&SPI protocols:A comparative study [C].16th IEEE International Conference on Electronics Circuits and Systems,2009:507-510.

[11]TI. MSP430x5xx/MSP430x6xx family user’s guide [DB/OL].http://www.ti.com.cn,2010.

[12]SU Kuifeng,LV Qiang.The principle and development of TMS320F2812[M].Beijing:Electronics Industry Press,2005:124-134 (in Chinese). [蘇奎峰,呂強.TMS320F2812原理與開發 [M].北京:電子工業出版社,2005:124-134.]

[13]ZENG Lieguang,JIN Depeng.Application specific integrated circuit design [M].Wuhan:Huazhong University of Science Press,2008:141-164(in Chinese).[曾烈光,金德鵬.專用集成電路設計 [M].武漢:華中科技大學出版社,2008:141-164.]

[14]YU Xiqing.ASIC design practical course [M].Hangzhou:Zhejiang University Press,2007:252-261 (in Chinese). [虞希清.專用集成電路設計實用教程 [M].杭州:浙江大學出版社,2007:252-261.]

[15]Dale Johnson.Implementing serial bus interfaces using general purpose digital instrumentation [J].IEEE Instrumentation &Measurement Magazine,2010,13 (4):8-13.