基于ARM和FPGA的經濟型數控系統硬件設計與實現

劉 更,王清理,孟 偉,趙 甫,張 寶

(1.中國航天科工集團第二研究院706所,北京100854;2.北京林業大學 信息學院,北京100083)

0 引 言

根據我國當前市場需求的實際情況,數控系統按功能和配置可分為高檔型、中檔型和經濟型3種[1]。中高檔數控系統功能齊全、加工精度高,多采用PC+NC構架的開放式數控系統,但價格較貴。經濟型數控系統由于其良好的性能價格比,目前在國內市場占據了一半以上份額[2-4]。經濟型數控系統多采用8位或16位單片機實現,具有品種多樣、功能較全、可靠性較高、價格低廉、操作簡單、維修方便等特性。隨著微電子技術和計算機技術的發展,以ARM為主的高性能嵌入式處理器在數控領域得到逐步應用。與單片機相比,嵌入式ARM處理器多為32位RISC處理器,具有運算速度快,外圍資源和通信接口豐富等優勢。同時,ARM處理器可運行實時多任務LINUX操作系統,基于LINUX開發的應用軟件具有實時性好,移植方便等優點。嵌入式ARM處理器設計技術的日益成熟完善,使得系統成本不斷降低,為應用嵌入式ARM處理器構建的經濟型數控系統提供了必要的條件。

EP9315[5]是一款內含ARM920T內核,低成本、高集成度、高性能的32位嵌入式ARM微處理器[3]。它內嵌MaverickCrunchTM協處理器,支持浮點運算和DSP處理指令,彌補了以往數控系統采用的ARM處理器其運算性能不佳的缺點。本方案以EP9315為核心,擴展Cyclone III[6]系列低成本FPGA,并以MSP430[7]單片機實現模擬接口實現的集采集、處理與控制為一體的經濟性數控系統,具有低功耗、低成本、信息處理能力強、接口豐富、可擴展性好等特點[8]。

1 系統總體設計

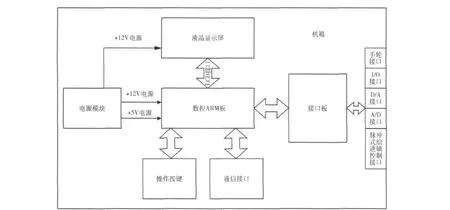

本文實現經濟型數控系統人機界面、手輪接口、網絡通信接口、4路給進軸控制、2主軸控制、64路輸入、24路輸出等功能。系統由以下部分組成:

(1)數控ARM板。它是本系統核心部分,實現系統的主要功能;

(2)人機接口。包括LCD顯示屏,按鍵板和接口轉接板,提供數控系統的各種輸入輸出接口;

(3)軟件。包括FPGA軟件和單片機軟件。

系統組成框圖如圖1所示。

圖1 系統組成框架

1.1 系統硬件設計

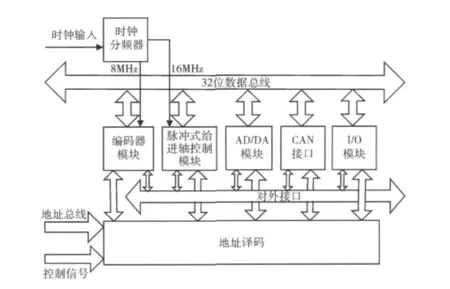

本節主要介紹數控ARM板的電路設計。數控ARM板是本系統的核心,電路設計時選用高集成度芯片簡化設計,降低成本。系統各功能主要由處理器、FPGA、單片機等元件設計完成。原理框圖如圖2所示。

1.1.1 處理器核心電路設計

本文采用Cirrus公司高集成、高性能、低成本的32位ARM嵌入式微處理器EP9315作為核心。它采用ARM920T內核,處理器時鐘可達250MHz。處理器內嵌MaverickCrunchTM協處理器,支持浮點運算和DSP處理指令,彌補了以往的ARM處理器運算能力較低的缺點。

在處理器AHB總線端擴展32MB Flash固化啟動程序、操作系統及應用程序,擴展64MB SDRAM用于加載程序并提高運行速度。AHB總線經驅動芯片擴展4Mbit高速鐵電存儲器用來保護關鍵數據[9]。數控應用程序將關鍵數據即時寫入該存儲器,若遇系統突然掉電,關鍵數據可在下次上電后通過程序恢復,并繼續執行未完成的加工,從而減少廢品率,節約加工成本。

1.1.2 FPGA電路設計

本文選用Altera公司Cyclone III系列FPGA芯片EP3C16F484。FPGA I/O管腳經過雙向總線驅動芯片連接到EP9315的AHB總線。處理器的片選信號nCS2連接至FPGA的I/O管腳,從而將FPGA映射到ARM內存空間0X20000000-0X2FFFFFFF范圍內。FPGA連接處理器端16根地址線,這樣FPGA內部就有65536字節空間可以被ARM處理器EP9315以內存的方式訪問。

FPGA實現I/O接口、CAN總線接口、單片機接口的譯碼和寄存器功能,并實現編碼器和脈沖式給進軸時序邏輯控制等功能,共占用295個I/O管腳。

1.1.3 單片機電路設計

本文應用TI公司低功耗單片機MSP430F167實現數控系統2路主軸控制和4路模擬量的采集。主軸控制模擬量輸出范圍-10V~+10V,模擬量輸入范圍為0~5V。MSP430單片機具有豐富的片上外圍模塊及高性能模擬技術,可配置8路12位模擬量接口,最大可提供2路D/A和6路A/D接口或8路A/D接口,輸入輸出模擬量范圍為0~2.5V。本系統通過擴展外圍運放電路實現2路12位-10V~+10V模擬量輸出和4路12位0~5V模擬量輸入。單片機模擬部分與系統數字部分采用數字隔離方式,通過12位AD數據線、12位DA數據線、3位地址信號、寫信號/WR、讀信號/RD完成數據交互。

1.1.4 外圍接口電路設計

ARM處理器片上集成了網絡MAC控制器,擴展PHY芯片KSZ8721[10]實現10/100M自適應網絡接口。通過片上集成的全速USB控制器、URAT控制器、LCD控制器、鍵盤掃描控制器,加上外圍接口電路實現USB、串口、LCD顯示以及鍵盤等接口功能。

通過FPGA擴展SJA1000實現CAN總線接口[11];擴展差分轉單端接口芯片AM26LV32實現4路24位編碼器接口[12];4路脈沖式給進軸控制輸出信號由FPGA產生,經高速光藕芯片HCPL0631隔離輸出控制給進軸[13];64入24出標準I/O接口由光藕TLP621和光繼電器 AYQ211實現[14-15]。

1.2 系統軟件設計

本文主要介紹FPGA和單片機兩部分軟件設計。

1.2.1 FPGA軟件設計

FPGA通過編程實現了I/O接口、CAN總線接口、與單片機接口部分的譯碼及寄存器功能,還實現編碼器和脈沖式給進軸控制的時序邏輯控制功能。

FPGA軟件設計采用模塊化設計方法,頂層采用圖形界面設計,各組成模塊采用Verilog HDL硬件描述語言進行設計。FPGA內部邏輯框圖如圖3所示。I/O接口、CAN總線接口以及編碼器等模塊主要涉及計數器、譯碼器和寄存器的設計,功能簡單、實現方便。本文主要介紹功能相對復雜的脈沖式給進軸控制模塊和單片機接口部分的軟件設計。

圖3 FPGA內部邏輯框架

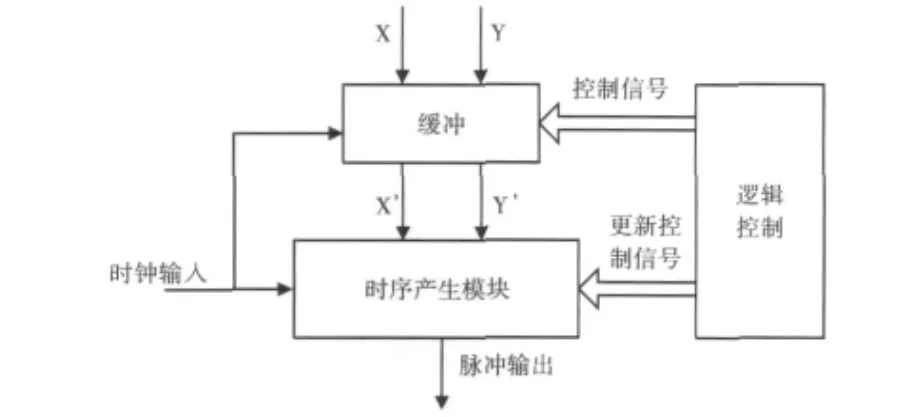

1.2.1.1 脈沖式給進軸控制模塊設計

脈沖式給進軸控制模塊控制數控系統伺服給進軸,該模塊輸出頻率最高為500KHz的均勻脈沖,并以2ms的插補周期更新脈沖輸出頻率。

根據插補周期,設計主時鐘頻率為16MHz,輸出脈沖高電平固定寬度為5個主時鐘周期,即312.5ns。設單周期輸出脈沖個數為x,輸出脈沖周期長度 (主時鐘周期數)為y,有公式y=32000/x-5,使得2ms周期內發出的x個脈沖分布基本均勻。該方法計數準確且余數處于周期的尾部,可使給進軸運轉平穩。

公式的運算由ARM處理器完成,處理器將運算結果送入脈沖式給進軸控制模塊。x,y值經過一級緩沖后送給脈沖時序產生模塊。緩沖保證2ms周期內計數值不被刷新,并且在每個周期的末尾時刻更新x,y的值,使得新的周期按照新的數據完成給進軸的控制輸出。脈沖式給進軸控制模塊框圖見圖4。

圖4 脈沖式給進軸控制模塊框架

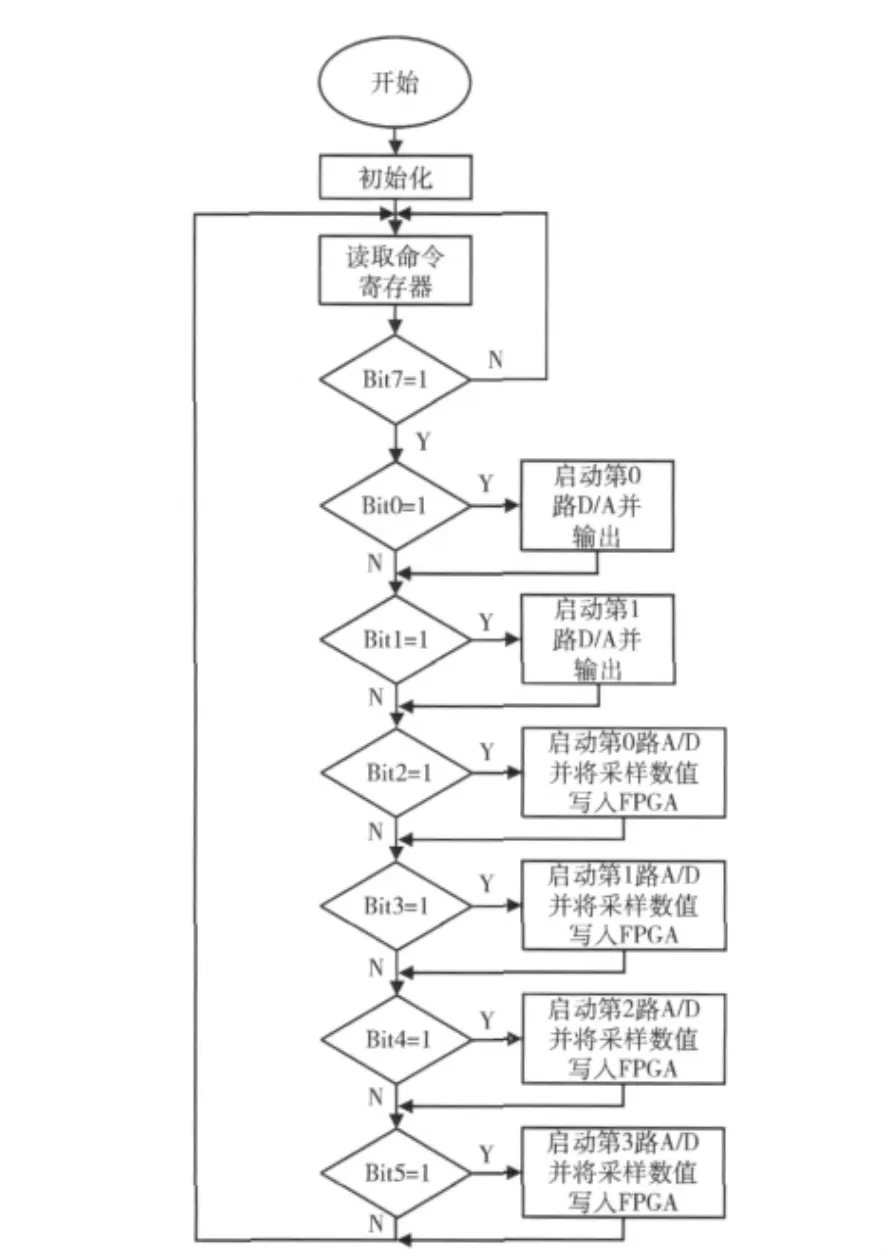

1.2.1.2 單片機接口模塊設計

FPGA內部設計6個12位數據寄存器,分別對應2路模擬量輸出和4路模擬量輸入。設計1個8位控制寄存器由ARM處理器寫入控制命令,單片機讀取控制寄存器值,并按相應的控制命令執行數/模或模/數轉換。

單片機讀取轉換使能位有效,且讀入控制命令為D/A轉換時,單片機接著讀取對應通道的模擬量輸出數據寄存器,然后通過D/A變換后輸出模擬量。當讀入控制命令為A/D轉換時,單片機采集對應通道的模擬量,經A/D變換后將數據寫入FPGA,并觸發FPGA向處理器發送中斷請求。轉換命令寄存器內容見表1。

轉換命令寄存器的內容被讀取后FPGA程序控制該寄存器清零,從而保證下次執行更新后的轉換命令。

表1 轉換命令寄存器

1.2.2 單片機軟件設計

單片機與FPGA之間通過12位AD數據線、12位DA數據線、3位地址信號、讀寫信號完成數據交互,實現系統A/D和D/A功能。信息交互方式描述如下:ARM處理器通過寫FPGA內部轉換控制寄存器,發送D/A或A/D轉換請求,單片機循環讀取FPGA內部轉換命令寄存器內容,并完成相應的D/A、A/D轉換。單片機程序流成圖如圖5所示。

2 實驗結果與分析

2.1 仿真結果與分析

在完成FPGA代碼設計后,通過仿真對系統主要功能進行了測試和驗證。先對各模塊進行分別設計和仿真,確認功能正常后再將代碼合成進行整個工程的仿真。本文主要介紹編碼器模塊和脈沖式給進軸控制模塊的仿真結果與分析。

2.1.1 編碼器模塊仿真與分析

編碼器模塊的輸入信號為伺服反饋脈沖,編碼器通過計數反饋脈沖值得到伺服運動位置和運動方向。該模塊仿真結果如圖6所示。圖中,方向控制信號DIRCON為低時,若脈沖A在脈沖B前,編碼計數器正向計數,表示正轉;若脈沖A在脈沖B后,編碼器逆向計數表示反轉。由仿真結果可見,脈沖計數值為反饋脈沖值的4倍,計數值與輸入吻合,模塊功能正常。

2.1.2 脈沖式給進軸控制模塊仿真與分析

圖5 單片機程序流程

將初始脈沖輸出個數x設為1000,經計算可得y值為27,并在下一2ms周期前將x值設為333,對應的y值為91,信號pulse1為脈沖輸出,pulse2為脈沖輸出使能信號,高電平有效。仿真結果如圖7、圖8所示。由仿真結果1可見,模塊輸出脈沖均勻。由仿真結果2分析,周期計數器c每計32000個clk時鐘后清零,保證2ms周期精準無誤;輸出脈沖計數器a在第一周期末尾計數共1000個,脈沖輸出個數準確,仿真結果功能正常。

2.2 系統功能實驗結果與分析

各部件生產完成后,將數控ARM板、鍵盤、液晶顯示屏、電源模塊、轉接板等部件集成到機箱內部,并按圖9連接數控系統與伺服驅動等實驗設備。然后對系統I/O接口、AD/DA接口、編碼器、顯示器和鍵盤接口、手輪接口、給進軸控制接口等功能進行測試。本文主要介紹給進軸控制接口和AD/DA接口的實驗情況。

在開發機上編寫單次脈沖發送測試程序并下載到數控系統上運行,與伺服相連接的監控微機能實時監控伺服驅動器的運行情況,包括收到的脈沖個數和電機轉速。分別測試極大值和其它幾個典型值并記錄結果于表2。隨后系統運行AD/DA測試程序,通過高精度數字萬用表和穩壓電源對系統模擬部分進行測試,測試記錄見表2。

圖9 測試連接

對實驗數據進行分析,系統A/D輸入精度約為±5LSB(±0.06mV),D/A 精度約為±0.16mV (±4LSB)。伺服驅動器收到的脈沖數與發送的脈沖個數相等,示波器觀測到的輸出脈沖波形均勻,當輸入值為1000時,脈沖輸出頻率達到500KHz。在單次發送脈沖測試正確后,用周期為2ms的中斷觸發脈沖輸出,同過伺服監控微機觀察到給進電機轉速平穩。其它接口如掉電保護功能、I/O接口、通信接口、顯示和鍵盤等接口經實驗驗證功能正常。

本文實現的經濟型數控系統具有以下特點:

(1)所選用處理器具有較強的浮點運算能力,提高了經濟型數控系統插補運算性能;

(2)提供多路大容量位置反饋編碼器,可實現較為精確的閉環控制功能;

(3)數控控制接口豐富,實現2路主軸,4路給進軸的控制功能。給進軸控制采用脈沖輸出式方式;

(4)通信接口豐富,實現了2路RS232串行接口,1路標準以太網接口,1路CAN總線接口,可實現數控系統的網絡化,并且提高了系統的可擴展性;

(5)實時數據掉電保護功能,可恢復掉電前的關鍵數據,降低廢品率,節約加工成本;

(6)采用高集成度FPGA設計,可靠性高、功耗低,FPGA程序設計采用模塊化方法,可擴展性好。

3 結束語

本文在對國內經濟型數控系統體系結構以及發展現狀進行綜合分析的基礎上,提出并實現了以ARM處理器EP9315和FPGA為核心的經濟型數控系統。該系統較現有經濟型數控產品具有浮點運算能力較強、接口豐富、可擴展性強,并提供掉電保護功能等特點,系統設計時通過多種方法降低成本,實現了較高的性能價格比。經實驗,系統各項功能正常,最終產品可通過裁減或擴展的方式適應各種經濟型數控機床的實際需求。

[1]WANG Yulin.The need for developing economical CNC system[DB/OL].http://www.cnki.com.cn/Article/CJFDTOTALJCYY200610081.htm,2011(in Chinese).[王玉琳.發展經濟型數控系統的必要性 [DB/OL].http://www.cnki.com.cn/Article/CJFDTOTAL-JCYY200610081.htm,2011.]

[2]LIAO Xiaoguo.CNC technology [M].Wuhan:Hubei Science and Technology Press,2004 (in Chinese).[廖效果.數控技術 [M].武漢:湖北科學技術出版社,2004.]

[3]WU Zhiheng.XU Xuanbo.Trends of CNC machine technology[J].Mechanical and Electrical Engineering,2004,33 (9)(in Chinese).[吳智恒,徐旋波.數控機床技術發展趨勢 [J].機電工程技術,2004,33 (9).]

[4]Trends of CNC system and CNC machine technology [DB/OL].http://articles.e-works.net.cn/445/article10136.htm,2011(in Chinese).[數控系統與數控機床技術發展趨勢 [DB/OL].http://articles.e-works.net.cn/445/article10136.htm,2011.]

[5]EP9315User’s guide [DB/OL].http://www.cirrus.com,2011.

[6]Cyclone III device handbook [DB/OL].http://www.Altera.com,2011.

[7]SHEN Jianhua,YANG Yanling,HUO Xiaoshu.Principles and applications of ultra-low power MSP430series 16bits microcontroller[M].Beijing:Tsinghua University Press,2004 (in Chinese).[沈建華,楊艷琴,霍驍曙.MSP430系列16位超低功耗單片機原理與應用 [M].北京:清華大學出版社,2004.]

[8]LI Suo.Design and implementation of economical CNC system based on uC/OS II and the hardware interpolation chip [D].Beijing:Graduate School of Chinese Academy of Sciences,2006 (in Chinese).[李鎖.基于uC/OS-II及硬插補芯片的經濟型數控系統的設計與實現 [D].北京:中國科學院研究生院,2006.]

[9]FM22L16datasheet [DB/OL].http://www.ramtron.com/files/datasheets/FM22L16_ds.pdf,2011.

[10]KSZ8721BL datasheet [DB/OL].http://www.alldatasheet.com/datasheet-pdf/pdf/412972/MICREL/KSZ8721BL.html,2011.

[11]Sja1000datasheet [DB/OL].http://www.zlgmcu.com/philips/can/sja1000/sja1000_cn.pdf,2011.

[12]Am26LV32datasheet [DB/OL].http://www.ti.com,2011.

[13]HCPL0631datasheet [DB/OL].http://www.avagotech.com/docs/AV02-0940EN,2011.

[14]TLP621datasheet [DB/OL].http://Toshiba-components.com/docs/optp/tlp621_en_datasheet.pdf,2011.

[15]AQY211EHA datasheet [DB/OL].http://panasonic-denko.co.jp/ac/e/index.jsp,2011.