三種一分三路等功率分配器的性能比較

徐 琰, 韓淑萍, 王俐聰

(上海無線電設備研究所,上海200090)

0 引言

在微波電路中,為了將功率按一定的比例分成兩路或者多路,需要使用功率分配器[1]。功率分配器反過來使用就是功率合成器。所以通常功率分配/合成器簡稱為功分器。功分器被廣泛地應用于微波及毫米波電路,在陣列天線的饋電網絡中,功率分配器可以將一路信號分成多路信號;應用于微波固態放大器,可以將多個信號合成一個更大功率的輸出信號。功分器是固態發射機的一個關鍵微波部件,功分器設計的好壞直接關系到固態發射機的效率、幅頻特性等性能的好壞。

多路功分器的設計可以分為兩類:第一類是通過一個結構將一路信號一次性地分成多路輸出;第二類是將一路信號經過一系列的一分二結構逐次地分成多路輸出。在第二類功分器中最基本的單元是一分二功分器,然后由基本單元級聯形成N路偶等分功分器,對于奇等分功分器,通常慣用的設計方法是將其中一路加負載匹配。但加負載后會引起某些指標的下降,故引起了對不同結構奇等分功分器的研究,通過三種一分三功分器的設計和仿真,比較各自性能的優缺點。

1 直接一分三的等功率分配器

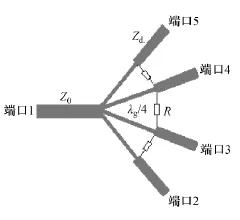

通常來講,通過一個結構將一路信號一次性地分成多路的功分器有較高的分配效率,信號經過的梯次少,插損較小。當功率分配的路數大于2時,微帶形式的一分多路功率分配器可分為兩類,分別是扇形和放射形,功分器拓撲結構如圖1和圖2所示。這種功率分配器各自有不同的應用側重點,對扇形功率分配器來講,電磁波在平面上傳播,對于不同的輸出端口,可以有不同的功率輸出。

圖1 扇形結構功率分配器

圖2 放射形結構功率分配器

圖3為采用扇形結構設計的一分三路功分器仿真模型,通道插損、通道之間隔離度的仿真結果分別如圖4(a)、4(b)所示。

圖3 一分三路功分器仿真模型

扇形結構功分器仿真結果:駐波小于1.5,相位差小于2.5°,最大插損-5.1 dB,最小隔離度為-14.6 d B。在理想情況下,直接一分三路功分器插損為-4.815 dB,仿真結果接近理論值。因為端口2、4之間沒有隔離電阻,端口2、4之間隔離度較差。

圖4 功分器插損及通道間隔離度仿真結果

2 基本單元一分二功分器的設計

第二類功分器是將一路信號經過一系列的一分二結構逐次地分成多路輸出,其最基本的單元是一分二功分器。為了保證各輸出端口有很好的隔離度,一分二的功分器采用威爾金森(Wilkinson)功分器[2]。

威爾金森功分器的對稱性保證了信號的平衡度和隔離度,隔離電阻進一步提高了輸出端口的隔離度,單節3 dB威爾金森功分器即可實現倍頻的帶寬。改變兩個輸出分支線的特性阻抗,可以實現任意功分比的分配。

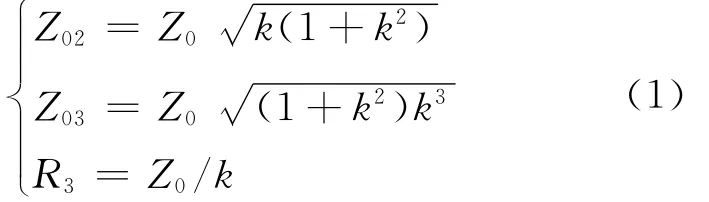

圖5(a)為傳輸線結構任意功分比的功分器原理圖。假設端口1無反射;端口2、端口3輸出電壓相等且同相;端口2、端口3輸出功率比值為1/k2,k為任意指定值。

兩段分支微帶線電長度L為λ/4,終端分別接負載R2和R3,設R2=k Z0,由傳輸線理論,可得 Z02、Z03、R3的計算公式為

式中:Z0為輸入端口特性阻抗;Z02、Z03分別為兩段分支微帶線特性阻抗;R3為端口3的負載。

圖5 功分器示意圖

取k=1,即得到3 dB威爾金森功分器的各參數值:Z02=Z03=Z0,R2=R3=Z0,圖5(b)為3 dB威爾金森功分器結構圖,為了增加隔離度,在端口2、3之間添加隔離電阻R,R=2Z0。

描述3 dB威爾金森功分器的關鍵指標有三個:駐波系數、插損和隔離度。由對稱關系可知,端口1、3間的插損等于端口1、2間的插損。設計功率分配器時要考慮:在工作頻帶內駐波系數盡可能的接近1,插損盡可能接近3 dB,隔離度絕對值盡可能大;一分多的功分器還要考慮各端口間的相位一致性。

3 加負載匹配的一分三路功分器

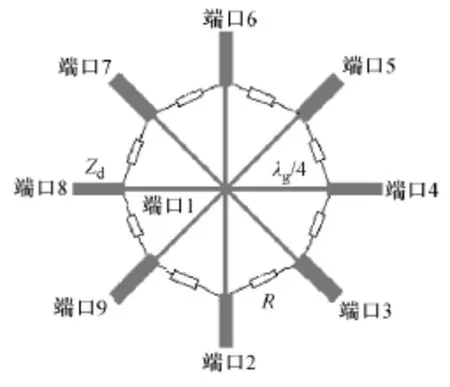

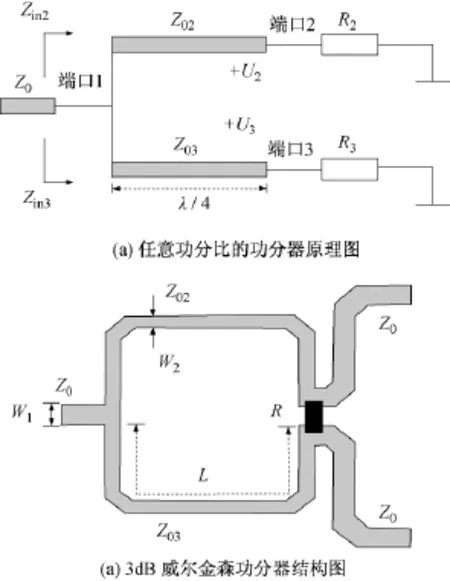

一分N路偶等分功分器可由多個威爾金森功分器電路級聯而成,N路威爾金森級聯功分器原理圖如圖6所示[3]。

圖6 N路威爾金森級聯功分器

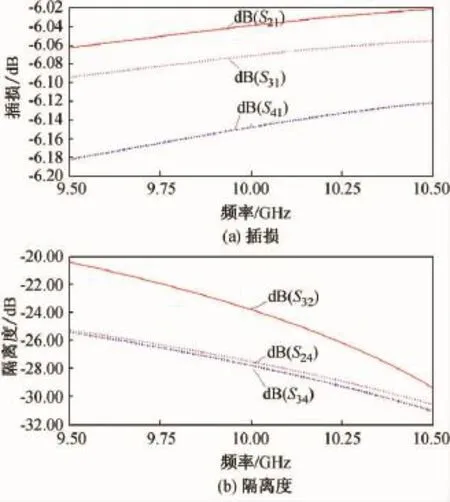

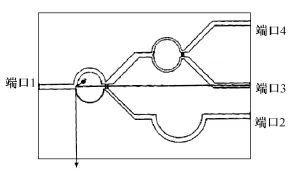

對于奇等分功分器,通常的設計方法是將其中一路加負載匹配。三個3 dB威爾金森功分器級聯形成一分四路功分器,選擇一分四功分器的其中一路加負載匹配設計一分三路功分器。仿真模型及端口設置如圖7所示。通道插損及通道之間隔離度仿真結果分別如圖8(a)、8(b)所示。

圖7 功分器仿真模型

圖8 功分器插損及通道間隔離度仿真結果

該功分器仿真結果:駐波小于1.25,相位差小于0.5°,最大插損-6.1 d B,最小隔離度為-23 dB。在理想情況下一分四路功分器插損為-6 dB,加負載匹配造成能量損失,仿真結果接近理論值。該功分器通道間隔離度較好。

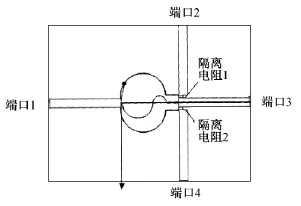

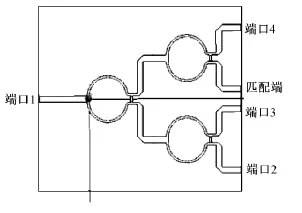

4 由兩個一分二功分器級聯的一分三功分器

在平面微波集成電路中,直接分成多路的簡單功率分配器不能滿足各輸出端口間高隔離度的要求;加負載匹配的功分器插損較大;第三種方法可以采用不等分一分二功分器與等分一分二功分器的級聯來設計一分三等功率分配器。

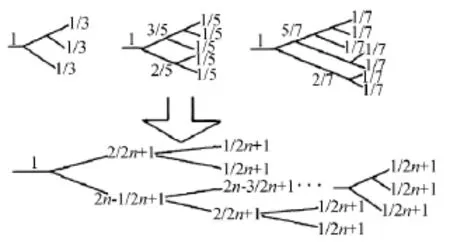

從最簡單的三等分功分器出發,可以先將輸入P0按1∶2不等分,然后再將初次分配后功率為2P0/3的一支再二等分。繼而推演得出五等分、七等分功分器的網絡拓撲結構,圖9為普遍奇等分功分器的拓撲結構[4]。

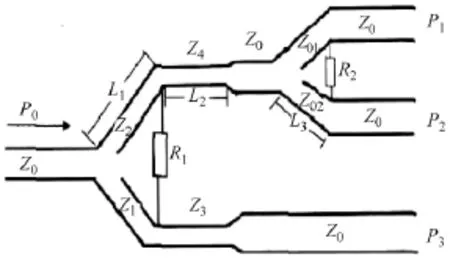

圖10為三等分功分器的結構,其中Z0是輸入和輸出端口傳輸線之間分支線特性阻抗,Z1、Z2、Z3、Z4為各段分支線的特性阻抗,Z01、Z02為兩等分支路的特性阻抗,R1、R2為隔離電阻的阻值。

圖9 奇等分功分器的拓撲結構

圖10 三等分功分器的結構

根據功分器的阻抗變換式(1),得到圖10中Z1= 102.98Ω,Z2= 51.5Ω,Z3= 59.46Ω,Z4= 42.05 Ω,Z01=Z02=70.72 Ω,R1=106.1Ω,R2=100Ω。由于輸入按1∶2不等分,所以圖11為采用不等分一分二功分器與等分一分二功分器級聯設計的一分三路功分器仿真模型,端口2分別與端口3,4的相位差可通過改變通道2的微帶線長度來控制。

圖11 一分三路功分器仿真模型

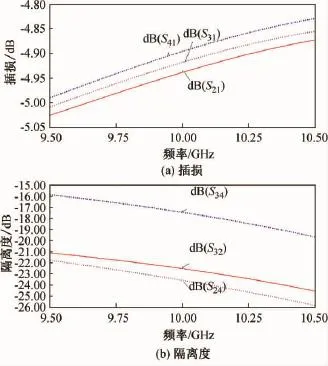

通道插損、通道之間隔離度分別如圖12(a)、12(b)所示。

該功分器仿真結果:端口駐波小于1.45,相位差小于0.5°,最大插損-4.9 dB,最小隔離度為-17.4 d B,插損仿真結果接近理論值。由仿真結果可見,采用不等分一分二功分器與等分一分二功分器級聯設計的一分三路功分器的隔離度比扇形直接一分三功分器的隔離度性能好。

5 三種結構功分器仿真性能比較

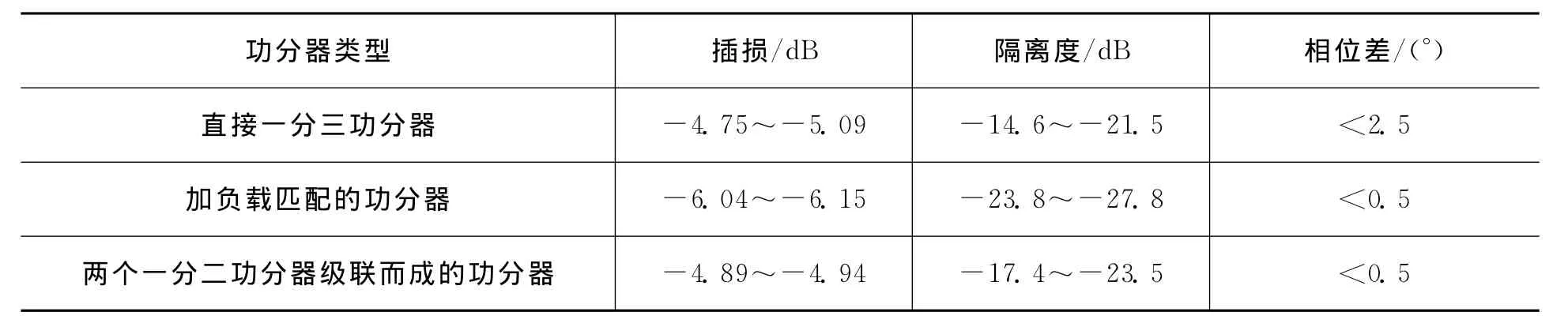

各種功分器的駐波性能可以通過改善匹配提高性能,主要比較不同結構功分器的插損、隔離度和相位性能,表1列舉了三種結構功分器的插損、隔離度、相位一致性性能的仿真結果。

分析表1中數據后得到如下結論:

a)扇形直接一分三功分器尺寸小、插損小,但有一路隔離度較差,相對其它兩種結構,各端口之間相位差稍大。

b)由三個3 dB威爾金森功分器級聯設計的一分三路功分器,各端口之間隔離度高,相位一致性好,由于其中一路接負載匹配損耗一部分功率,故插損較大;如果功分器工作頻率很高(超過K波段),接負載端容易影響其它端口幅相一致性,需調節匹配端口位置使影響最小。

c)由不等分和等分的兩個一分二功分器級聯設計的一分三功分器插損小且功率分配一致性好,相位一致性好,隔離度性能處于另外兩種功分器性能之間。

圖12 功分器插損及通道間隔離度仿真結果

表1 三種結構功分器性能比較

6 結束語

在總結一分三路等功率分配器的三種設計方法的基礎上,分別建模采用HFSS軟件仿真,并比較不同結構功分器的性能特點。三種功分器各有優勢,扇形直接一分三功分器插損小,但隔離度較差;由三個3 d B威爾金森功分器級聯設計的一分三路功分器端口之間隔離度高,但插損大;由不等分和等分的兩個一分二功分器級聯設計的一分三功分器插損小,隔離度性能處于另外兩種功分器性能之間,可根據使用場合尺寸、指標等要求來選擇合適的功分器形式。

[1] 清華大學《微帶電路》編寫組.微帶電路[M].北京:人民郵電出版社,1976:209-214.

[2] 程敏鋒,劉學觀.微帶型 Wilkinson功分器設計與實現[J],現代電子技術,2006,(20):25-26.

[3] 胡善祥,汪邦金,等.級聯功率分配/合成器功分器的優化設計[J],雷達與對抗,2007,(3):36-40.

[4] 趙晨星.奇等分微帶功分器的仿真設計[J],電訊技術,2006,48(7):77-79.