衛星移動通信終端的低功耗設計

王艷君,莊云勝

(1.通信網信息傳輸與分發技術重點實驗室,河北石家莊050081;2.中國電子科技集團公司第五十四研究所,河北石家莊050081)

0 引言

低功耗設計是指在產品的設計中,通過采用各種技術手段、降低產品功耗的技術[1]。低功耗的概念是由電子手表等工業首次提出的[2],進而在小型化、高集成度的消費類電子產品中得到了廣泛應用。

為了降低電路成本,提高電路穩定性、可靠性,需要進行低功耗設計,以保證在集成度提高時,單位面積可以維持同樣甚至更低的功耗;同時,因為在過去的30年中,電池的容量僅僅增加了2~4倍[3],遠沒有VLSI技術的發展迅速,所以在電池供電的手持設備中,電路的低功耗設計是延長待機時間的最有效手段;此外,在軍事應用中,在滿足使用要求的前提下采用更小的電池以減小整機的尺寸和重量,即意味著減小作戰負荷提高戰斗力,因此軍用手持設備的低功耗設計顯得尤為重要。

1 低功耗設計的研究內容

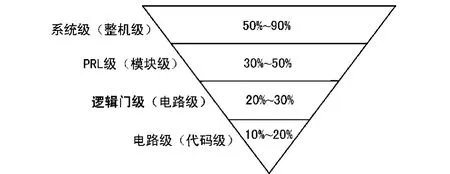

低功耗設計是通信終端設計的一個關鍵環節,是涉及到整機設計各環節的自上而下的設計技術。在IC設計領域,常采用如圖1所示的比例關系來表明在不同層面上采用低功耗設計技術對整體設計結果的影響,圖1可以同樣應用于設備的低功耗設計中(與括號中的級別相對應),即越是在高層采用相關設計,其設計結果對整機性能改善的程度越大。這是因為層次越高表明在設計中進行低功耗考慮得越早越全面,因此在較高層采用的低功耗設計策略效果越明顯。

圖1 設計的不同層次對功耗的影響

按照自上而下的設計原則,通信產品的低功耗設計可以分為整機級、模塊級、電路級和代碼級。

2 整機的低功耗設計

衛星通信終端通常由MCU模塊、信號處理模塊、射頻微波模塊和電壓轉換電路等電路模塊組成[4]。整機的功耗可以表示為:

式中,α為活躍因子,表示該模塊在整機工作過程中的活躍程度;pn為第n個模塊全工作狀態下功耗;N為整機可劃分開的電路單元,整機集成度越高,則N的值越小。

整機的低功耗設計就是采用合理的技術方案,在滿足整機各項功能、性能指標的前提下,通過提高設備集成度(減小N)、降低各模塊的活躍狀態(減小α)和減小模塊的工作功耗(pn)來降低整機的功耗[5]。

為了達到上述設計目的,整機級主要采用了如下的方法:

①以嵌入系統/處理器為核心,基于整機工作狀態感知的低功耗設計技術。工作狀態感知指的是處理器對操作人員使用狀態、用戶終端工作狀態和系統狀態等進行識別,根據用戶、終端和系統所處的狀態,啟用不同的節電策略,通過動態地改變式(1)中的活躍因子,達到降低總功耗的目的。例如:10 s工作人員不進行操作,則進入一級節電方式,如果10 min不操作則進入深度休眠;工作時間不到不進行接收嘗試,收不到下行導頻,則上行數據不發送等。

②優化整機方案,提高集成度電路。實體模塊是整機的直接組成單元,按照傳統終端設備的設計方法,功能復雜的手持機可能被劃分成十幾個電路模塊,這顯然不能滿足小體積低功耗的設計要求,因此本級進行低功耗設計的目的之一就是優化整機方案,對功能相同或類似的實體電路進行合并,提高整機集成度。

③合理選擇整機供電方案。選擇低電壓工作芯片是降低設備功耗的直接手段。因此,芯片(模塊)的選取均遵循小體積、低電壓和低功耗的選擇原則,并且每種芯片都具有待機模式(Standby)或睡眠功能(Sleep),都可以執行獨立的斷電操作。

選擇開關電源芯片替代傳統的線性DC/DC。減少直流電源電壓種類從而減少電源轉換芯片,并且仔細分析每種電壓的平均功耗,使電池組輸出接近于功耗大的電壓。

3 單元電路模塊的低功耗設計

現在的通信設備通常以數字電路為主,而當前大部分數字電路均采用CMOS電路,該類電路主要消耗4類功率:內部短路功耗、漏電功耗、開關電容功耗和啟動功耗。內部功耗是當門電路瞬變時,Vdd與地之間短路連接消耗的內部功率;漏電功耗是CMOS工藝普遍存在的寄生效應引起的;開關功耗則是來自負載電容,是由其充放電造成的;啟動功耗是電子設備或電子元件在上電時,由于電容等器件充電而產生的功耗,此類功耗只發生在開機瞬間。

開關功耗與短路功耗合稱為動態功耗。對CMOS電路而言,動態功耗基本上確定了總功耗。動態功耗為:

式中,f為開關頻率;C為對應的充放電電容;Vdd為電源電壓。從式(2)中可以看出,功耗與器件工作電壓的平方成正比,并且和工作頻率成正比。因此降低電路的動態功耗一方面是選擇低電壓供電的電路芯片;另一方面在于降低工作時鐘的頻率。對于嵌入式系統等智能處理器,由于在不同的工作狀態下處理的工作量不同,所以根據工作量的不同,采用自主調整供電電壓和工作頻率的方法可以節省大量的動態功耗。

漏電功耗通常稱為靜態功耗。產生靜態功耗的因素眾多,包括處于沒有完全關斷或接通的狀態下的IO以及內部晶體管的工作電流、內部連線的電阻、輸入與三態驅動的上拉或下拉電阻等。靜態功耗和器件的制作工藝有較大的關系。

在模塊和電路的設計中,可以采用以下方法來降低靜態功耗:①盡量選擇低功耗的CMOS芯片進行電路設計;②盡量少用匹配和衰減電路;③ 由于IO線上的上拉或下拉電阻要消耗一定的電流,因此盡量避免使用這些電阻,在無法避免時,盡量使用大阻值的電阻;④在成熟電路上去掉調試時使用的電源和工作狀態指示燈;⑤ 盡量不用雙極晶體管,這些器件需維持一個恒定電流,從而增加了靜態電流;⑥懸空的時鐘輸入會大大增加靜態電流,因此將不用的時鐘引腳連接至低電平;⑦ 提高集成度,減少器件間IO的使用。

4 FPGA的低功耗設計

FPGA是通信產品中最常用的信號處理與邏輯功能實現器件。如何降低FPGA的功耗已經成為一個重要的問題,許多學者從多個層面深入研究了FPGA的低功耗設計技術,在速度和面積方面,許多學者從系統級、開關級和門級等方面進行了深入研究。文獻[3]和文獻[5]提出了幾種復雜的FPGA功耗模型,研究了FPGA的結構參數并估計了不同的結構對功耗的影響。目前,基于SRAM工藝的FPGA應用最為廣泛,并且由于本文只涉及到應用中的低功耗設計,因此以ALTERA公司基于SRAM工藝FPGA為例,討論其低功耗設計技術。

4.1 FPGA的功耗計算

FPGA的功耗可以由表示為:

式中,pINT為無負載情況下的內部功耗,該值可以從相應器件的用戶手冊中查詢得到;pdcout為FPGA的直流功耗:

式中,pdcn為第n個管腳上的直流功耗;d為配置管腳總數目;pacout為器件的動態功耗,它決定于器件管腳的工作電壓、容性負載和開關頻率等。

式中,a為交流輸出的管腳數目;Cn為該管腳的容性負載值;fn為輸出開關頻率;Vn為該輸出管腳上開關輸出電壓值。對于5 V的IO電壓,Vn的值取3.8 V,工作電壓等于或低于3.3 V時,Vn取值與VIO相同。

4.2 FPGA的低功耗設計

由式(5)可見,在芯片確定的條件下,系統時鐘頻率對FPGA的總功耗有顯著影響,因為時鐘信號的開關活動最多,容性負載最大。不過,時鐘速度又與處理能力直接有關。下面介紹幾種在保持FPGA處理能力不變的前提下,通過改變軟件的設計降低電路中時鐘處理速度,來達到降低芯片功耗的方法。

4.2.1 并行技術

并行處理是在高速信號處理中經常采用的一種方法,其目的是將一條數據通路的工作分解到N條通路上完成,這樣每條數據通路的工作頻率都為原來的1/N,以此達到可以處理高速信號的目的。并行處理技術用在低功耗設計中其本質就在保持電路處理能力的基礎上通過增加電路的面積來達到降低式(5)中的fn,進而達到降低功耗的目的。

當然,增加的電路面積和連線資源會導致電容Cn的增加,并且輸出端口增加的二選一電路也會導致部分功耗,但這部分功耗的增加與并行處理所節省的功耗相比還是很小的,幾乎可以忽略不計的[6]。

4.2.2 流水線技術

流水線技術也是一種通過增加面積來提高速度的通用設計技術[7]。在電路中插入寄存器(流水線),既可以理解為提高了系統運行速度,也可以理解為通過采用較低的時鐘速率,達到了相同的處理能力。這是因為流水線結構實際上是把一個功能模塊分成n個階段進行流水線作業,每個階段由一個子模塊來完成,在子模塊之間插入寄存器,以驅動這些小模塊,在低速情況下,每個模塊完成了整個處理工作的1/n。盡管增加的寄存器,增加了部分功耗,但與速度的降低帶來的功耗的降低相比,這部分功耗幾乎可以不計。

4.2.3 異步技術

同步電路是由同步時鐘統一驅動的電路,由于同步電路中時鐘速率往往高于數據速率,且僅作為驅動的時鐘貫穿整個程序,因此造成了很大的功耗浪費。而異步邏輯電路不采用全局時鐘,而是用握手信號協調模塊間的運作,因此異步電路本質上是數據驅動的電路。因為沒有時鐘驅動,在沒有數據,或者數據不變化,電路不動作,因此電路翻轉次數的降低節省了大量功耗[8]。

在實際設計中,異步電路實現起來有一定的難度,特別是在高速電路中,但對于一些低速或對時序要求不嚴格的設計,異步電路還是有很大優勢。

4.2.4 門控時鐘設計技術

門控時鐘設計技術是指在FPGA設計中,為每一個最小的功能模塊設置時鐘控制信號,在程序運行過程中,根據需要將不參與運算的模塊輸入時鐘關閉,以節省功耗的設計技術。該技術也是一種用于同步電路中的低功耗設計技術[9,10]。

5 結束語

在衛星移動通信終端的研制中,通過采用上述技術和設計方法,使得正樣產品的待機和單收狀態功耗分別比初樣產品降低了60%和38%以上,特別是實現了低于200 mW的待機功耗。測試結果表明,采用低功耗設計技術對終端的推廣應用起到了極大的促進作用。

本文結合衛星移動通信終端的特點,從整機、單元電路、主要元器件及FPGA代碼設計等幾個方面對低功耗設計進行詳細的討論,并在實際工程項目應用中取得較好的效果。

[1] 羅義軍,姚彥通.通信系統中的低功耗設計[J].電信科學,2005(6):13-15.

[2] 田 朋,尹 光.CMOS電路中系統級低功耗設計研究[J].遼寧大學學報自然科學版,2008,35(2):125-128.

[3] 蘇志雄,郭慧晶,吳一亮,等.無線傳感器網絡SOC芯片的低功耗設計[J].微計算機信息,2007,23(2):133-135.

[4] 李 廣,班亞明,趙燕飛.新型便攜式衛星通信終端設計[J].無線電通信技術,2012,38(3):23-25.

[5] 張 杰.一種低功耗手持終端的基帶單元硬件平臺的設計[J].數字技術與應用,2012(5):166-167.

[6] 朱卓婭.鋰離子電池管理芯片的研究及其低功耗設計[D].南京:東南大學博士學位論文,2005(1):11-32.

[7] 何艷霞,何永泰.FPGA低功耗的設計研究[J].楚雄師范學院學報,2012,27(6):22-25.

[8] 郭宏泓.超低功率異步電路設計研究[D].鎮江:江蘇大學,2009:2-3.

[9] 胡 靖.集成電路低功耗設計可逆邏輯綜合及性能分析[D].哈爾濱:哈爾濱工程大學博士論文,2008(9):18-26.

[10]謝 亮.嵌入式系統低功耗設計[D].上海:上海交通大學碩士論文,2011(9):30-38.