功率VDMOS器件的新型SPICE模型

朱榮霞 黃 棟 馬德軍 王錦春 孫偉鋒 張春偉

(1 東南大學國家專用集成電路系統工程技術研究中心,南京210096)

(2 中國空空導彈研究院紅外探測器技術航空科技重點實驗室,洛陽471009)

垂直雙擴散金屬氧化物場效應晶體管(VDMOS 器件)是新一代的電力電子開關器件.由于具有獨特的高輸入阻抗、低驅動功率、優越的頻率特性及低噪聲等優點[1-3],VDMOS 器件成為當前半導體分立器件中的高端產品,應用范圍廣,市場需求大,發展前景好.目前,VDMOS 器件主要應用于電機調速、逆變器、電子開關及汽車電器等領域[4-5].而SPICE 模型是連接半導體器件物理與電路的橋梁,VDMOS 器件的廣泛應用使得人們對其SPICE 模型的需求越來越大.

針對VDMOS 器件的SPICE 模型,Sanchez等[6]初步建立了一種包含準飽和效應的模型,但是該模型沒有考慮積累區電阻寄生結型場效應晶體管(JFET)的溝道夾斷對于器件特性的影響.Victory 等[7]建立了一種基于表面勢的VDMOS 模型,但該模型僅考慮了寄生JFET 溝道未夾斷的情況,且對漂移區電阻的計算并不精確.Chauhan等[8]將VDMOS 器件看成一個普通的N 溝道金屬氧化物半導體(NMOS)串聯一個受柵壓和漏壓控制的電阻,該電阻僅僅由一個沒有物理意義的經驗公式給出,因此,該模型無法準確描述外界電壓的變化對VDMOS 器件內部特性造成的改變.鑒于已有VDMOS 模型精確度差等問題,至今為止,沒有一個標準的SPICE 模型可以描述VDMOS 器件的特性.

本文在經典的MOS 模型——BSIM3v3 模型的基礎上,建立了一套新的描述VDMOS 器件電學特性的SPICE 模型.為了準確描述VDMOS 器件的電學特性,除了考慮外部節點柵極、源極、漏極之外,還增加了4 個內部節點,并將VDMOS 器件視為1 個普通NMOS 與4 個電阻的串聯.

1 VDMOS 器件結構及SPICE 模型

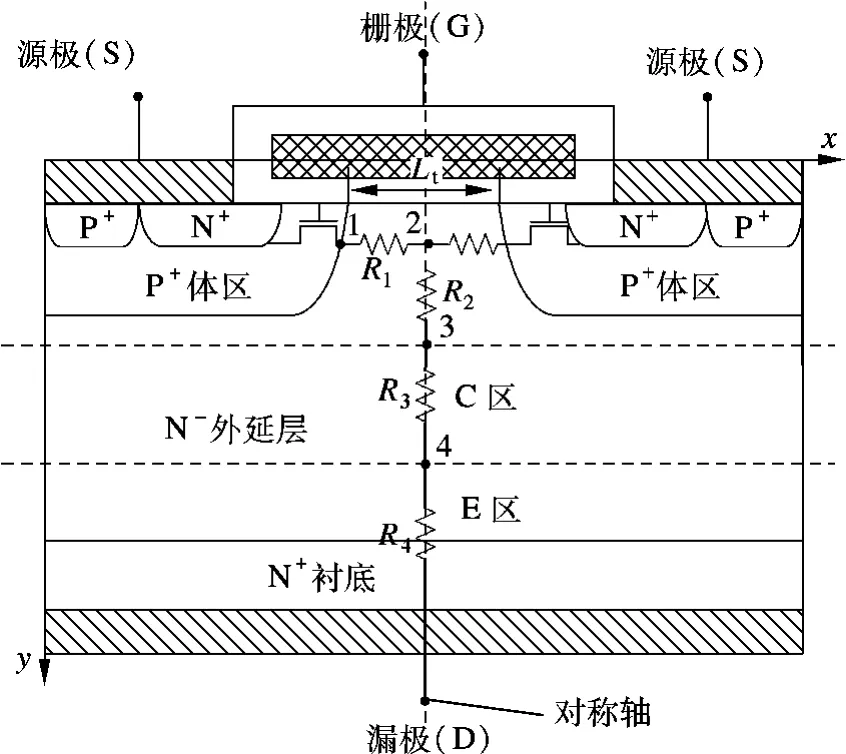

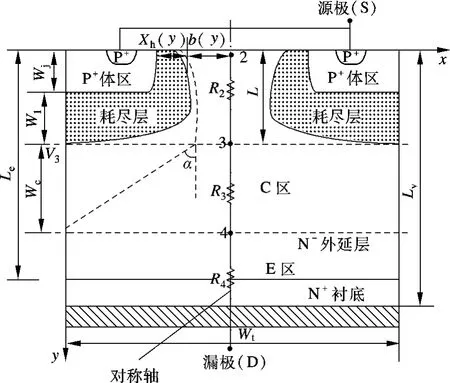

圖1 VDMOS 器件的元胞剖面圖

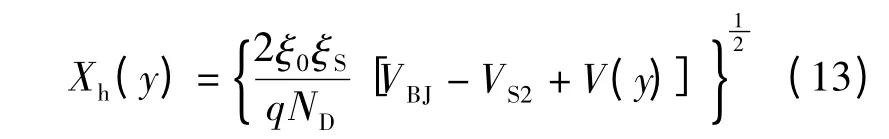

VDMOS 器件通常采用多元胞并聯的結構,以增大通態電流.圖1為VDMOS 器件的元胞結構圖.圖中,Lt為器件積累區的長度.可以看出,VDMOS 器件沿柵漏軸線對稱.如圖1所示,本文模型在源極(S)、柵極(G)、漏極(D)3 個外部節點的基礎上又增加了4 個內部節點,并分別將節點3 與節點4、節點4 與漏極D 之間的區域定義為C 區和E區.不同的區域對于VDMOS 器件電學特性的影響是不同的.如圖2所示,可將VDMOS 器件視為1個普通NMOS 器件與4 個電阻R1,R2,R3,R4的串聯.可將VDMOS 器件的源極、柵極及節點1 視為1 個普通的NMOS 器件.柵極電壓的變化可使積累區產生的電荷出現積累和耗盡2 種狀態,故節點1,2 之間的區域對于VDMOS 器件的影響可被視為1 個積累區電阻R1.2 個P+體區與N-外延層組成1 個寄生JFET 結構,隨源極、節點2 與節點3 電壓的變化,寄生JFET 結構的溝道耗盡或夾斷,故在節點2,3 之間引入了寄生JFET 電阻R2.考慮到VDMOS 器件的電流路徑在C 區與E 區是不同的[7],故將這2 個區域的電阻分別用R3和R4表示.只需要建立這4 個電阻的模型,便可得到VDMOS 器件的SPICE 模型.

圖2 VDMOS 器件的SPICE 模型結構圖

2 模型建立

2.1 積累區電阻R1

2.1.1 電流模型

在VDMOS 器件內部,沿x 軸方向流過積累區的電流為

式中,W 為器件的寬度;μN-eff為積累區的有效遷移率;Vg2為器件在積累區內的準費米勢;QN-為積累區內載流子的電荷,由積累區雜質電離引入的自由電子和柵極感應電荷Qin兩個部分組成,即

式中,q 為電子電荷;NN-,tsi分別為積累區的摻雜濃度及厚度.

將式(2)代入式(1),沿x 軸從節點1 到節點2對式(1)進行積分可得[9]

式中,V1,V2分別為節點1 與節點2 的電壓;V21=V2-V1.由式(3)可以看出,只要計算出Qin所在的積分項,就可以得出積累區的電流.

柵氧及積累區組成的結構類似于一個N 阱-P溝道金屬氧化物半導體(PMOS)結構.通過解泊松方程,得到積累區的柵極感應電荷Qin為[10]

式中,Cox為單位面積的柵氧化層電容;γG2為與工藝相關的體效應系數;ψs為積累區的表面電勢;φt為熱電壓.當ψs>0 時,積累區表面積累電子,Qin<0;反之,積累區表面耗盡或反型,Qin>0.

當積累區處于強反型狀態時,本文將Qin視為一個常數Qdep0,即

式中,Δφt為與熱電壓相關的參數;φFg為積累區的費米勢.

當積累區處于積累狀態時,Qin幾乎隨柵壓VG與Vg2的電壓差VGg2線性變化.令VFBg2為積累區的平帶電壓,當積累區處于積累狀態時,柵極感應電荷為

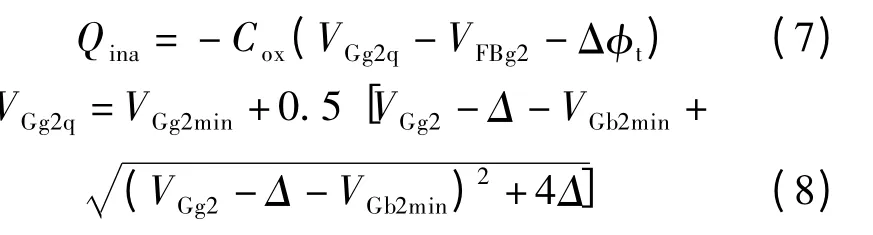

為了使用統一的公式來描述積累區處于積累狀態和強反型狀態時柵極感應電荷與VGg2的關系,引入了表面等效電荷Qina[11],即

式中,VGg2q為VGg2的有效值;Δ 為與工藝相關的參數;VGg2min為Qina=Qdep0時VGg2q的值.因此

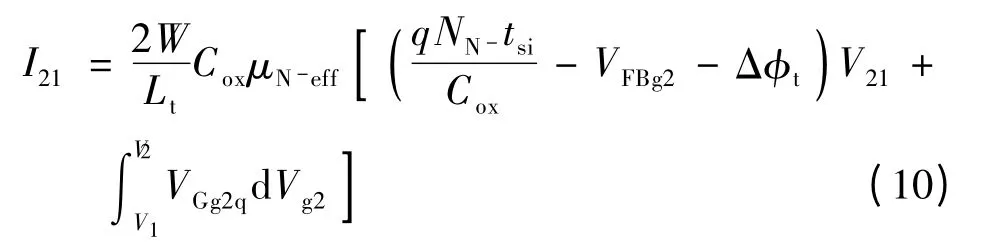

將式(7)代入式(3)得

令VG1=VG-V1,VG2=VG-V2.當VGg2=VG1,VGg2=VG2時,VGg2的值分別為VG1q,VG2q.將式(8)代入式(10)中的積分項簡化積分結果,得到

式中,V21q=VG2q-VG1q.

2.1.2 遷移率模型

VDMOS 器件在積累區的遷移率受橫向、縱向電場影響.在一定范圍內,橫向電場越強,積累區自由電子的速度越快;但當橫向電場過強時,積累區自由電子的速度則會達到飽和.縱向電場越強,積累區自由電子的運動越趨近于積累區表面,有效遷移率越低.遷移率的經驗模型為

式中,μ0為不考慮橫向、縱向電場影響時的遷移率;Esat為載流子速度飽和時的橫向電場.

將式(11)和(12)代入式(10),即可得出完整的積累區電流,進而可由R1=V21/I21得到積累區的等效電阻.

2.2 寄生JFET 電阻R2

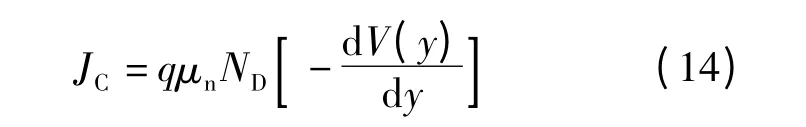

假設P+體區與N-外延層組成的寄生JFET的溝道(N-外延層)是線性緩變摻雜的,且其組成的PN 結為單邊突變PN 結.圖3為寄生JFET 電阻及C 區、E 區電阻的示意圖.圖中,寄生JFET 耗盡層的厚度為Xh(y),其溝道的半壁厚度為b(y)=Lt/2-Xh(y);L 為寄生JFET 的溝道長度;α≈45°為C 區電流路徑與y 軸的夾角[7];Wt為器件的長度;Wj為節點2 到P+體區下邊界的厚度;Wc為節點3 和節點4 之間區域的寬度;Le為節點2 到N-外延層底部的厚度;LV為節點2 到N+襯底底部的厚度;W1為PN 結產生的耗盡層的厚度.節點3 所在的垂直于y 軸的虛線表示電壓為V3的等勢線.

圖3 寄生JFET 電阻及C 區、E 區的電阻示意圖

寄生JFET 溝道的耗盡層厚度為

式中,ξ0為真空介電常數;ξS為硅材料的介電常數;ND為N-外延層的摻雜濃度;V(y)為以節點2為參考點的溝道電勢;VBJ為PN 結的接觸勢壘高度;VS2為源極電壓VS與V2之間的電壓差,即VS2=VS-V2.

2.2.1 線性區電流模型

根據歐姆定律,得到寄生JFET 的溝道電流密度為

式中,μn為寄生JFET 溝道的多數載流子遷移率.

考慮到該寄生JFET 為對稱柵結構,則寄生JFET 的溝道總電流為

將電流IC沿溝道從y=0 積分到y=L,即可得到肖克萊理論公式.將其簡化得到JFET 在線性區的電流方程為

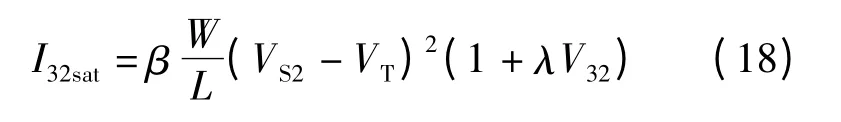

式中,工藝參數β =ξ0ξSμn/Lt;VT為閾值電壓;V32為節點3 與節點2 之間的電壓差,即V32=V3-V2.

2.2.2 飽和區電流模型

當V32增加到寄生JFET 的溝道夾斷電壓V32sat時,寄生JFET 的溝道開始夾斷.隨著V32的增大,夾斷點到節點2 區域內(導電溝道區)的壓差始終為V32sat,夾斷點向節點2 移動,電壓降V32-V32sat落在溝道夾斷區,進入導電溝道區的載流子將受溝道夾斷區電場的作用而漂移到節點3.因此,夾斷區的漏極電流仍由導電溝道區的漂移電流決定.

當V32=V32sat時,I32lin的值即為飽和電流I32sat.將V32sat=VS2-VT替換式(16)中的V32得

為考慮溝道長度調制效應,引入溝道調制系數λ=(ΔLV32)/L,其中ΔL 為寄生JFET 溝道夾斷區的長度,則修正后的飽和電流為

為使寄生JFET 線性區電流與飽和區電流連續,引入節點2 與節點3 之間的有效電壓V32eff[12],即

式中,δ 為V32eff的修正參數.

最終得到寄生JFET 區的電流方程為

同樣,可由R2=V32/I32得到寄生JFET 電阻.

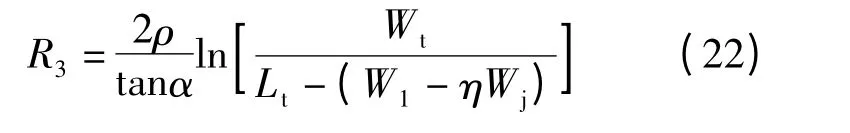

2.3 C 區電阻R3 及E 區電阻R4

在VDMOS 器件的C 區,由式(13)可得,該處由PN 結產生的耗盡層的厚度為

C 區的電阻由耗盡區的邊界決定,根據Victory 等[7]提出的方法可以得到電阻R3為

式中,ρ 為N-漂移區的電阻率;η 為參數.

在E 區,電流路徑的橫截面保持不變,因此該區域的電阻R4只與節點3,4 之間區域的寬度Wc有關.本文忽略漏端金屬的電阻,則電阻R4可表示為

式中,ρN為N+襯底的電阻率.

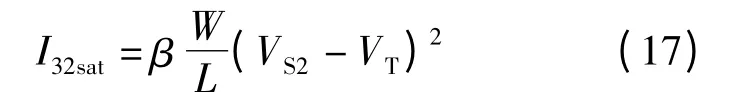

3 模型驗證

本文采用關態擊穿電壓為625 V 的VDMOS器件來驗證所建立的模型.圖4給出了在提模軟件MBP 中,使用本文所建模型對VDMOS 器件提模得到的擬合結果.由圖可知,該VDMOS 器件的準飽和效應嚴重,同時,基于本文模型得到的仿真值可以精確地擬合器件的準飽和區、飽和區及線性區.因此,本文提出的建模思路及方法是有效的.

圖4 仿真值與測試值的擬合結果

4 結語

本文建立了功率VDMOS 器件的SPICE 模型.在VDMOS 器件源極、漏極、柵極3 個外部節點的基礎上又增加4 個內部節點,分段考慮了各個節點之間器件的結構特征.通過將VDMOS 器件視為1 個普通NMOS 與4 個電阻的串聯,準確有效地計算這4 個電阻的阻值,建立了精確的VDMOS 器件的SPICE 模型.經驗證,該模型具有高的精確度,可以準確地擬合VDMOS 器件線性區、飽和區、準飽和區的電學特性.

References)

[1]Zhang Long,Yu Huilin,Wu Yifan,et al.On state output characteristics and transconductance analysis of high voltage(600V)SJ-VDMOS[C]//Proceedings of 2012 IEEE International Conference on Solid-State and Integrated-Circuit Technology.Xi′an,China,2012:1-3.

[2]Messaadi Lotfi,Smail Toufik.The electro-thermal sub circuit model for power MOSFETs[J].Microelectronics and Solid State Electronics,2012,1(2):26-32.

[3]Duan Baoxing,Yang Yintang.Power VDMOS transistor with the step oxide trench breaks the limit line of silicon[J].Micro &Nano Letters,2011,6(9):777-780.

[4]Bao Jiaming,Qi Haochen,Zhang Jian,et al.VDMOS modeling for IC CAD[C]//Proceedings of 2011 IEEE Joint International Information Technology and Artificial Intelligence Conference.Chongqing,China,2011:245-249.

[5]Antonios Bazigos,Francoins Krummenacher,Jean Michel Sallese,et al.A physics-based analytical compact model for the drift region of the HV-MOSFET[J].IEEE Transactions on Electron Devices,2011,58(6):1710-1721.

[6]Sanchez J L,Gharbi M,Tranduce H,et al.Quasisaturation effect in high-voltage VDMOS transistor[J].Solid-State and Electron Devices,1985,132(1):42-46.

[7]Victory J J,Sanchez J L,Demassa T A,et al.A static,physical VDMOS model based on the charge-sheet model[J].IEEE Transactions on Electron Devices,1996,43(1):157-164.

[8]Chauhan Y S,Anghel C,Krummenacher F,et al.A compact DC and AC model for circuit simulation of high voltage VDMOS transistor[C]//Proceedings of the 7th International Symposium on Quality Electronic Design.San Jose,CA,USA,2006:109-114.

[9]Jia Kan,Sun Weifeng,Shi Longxing.A novel surface potential-based short channel MOSFET model for circuit simulation[J].Microelectronics Journal,2011,42(10):1169-1175.

[10]Tsividis Yannis.Operation and modeling of the MOS transistor[M].New York:McGraw-Hill,1999.

[11]Shi Longxing,Jia Kan,Sun Weifeng.A novel compact high-voltage LDMOS transistor model for circuit simulation[J].Electron Devices,2013,60(1):346-353.

[12]Liu William.MOSFET models for SPICE simulation,including BSIM3v3 and BSIM4[M].New York:Wiley,2001.