基于DSP的高速動(dòng)車組車內(nèi)噪聲測(cè)試系統(tǒng)設(shè)計(jì)

辛光,伍川輝

(西南交通大學(xué)機(jī)械工程學(xué)院,四川成都 610031)

基于DSP的高速動(dòng)車組車內(nèi)噪聲測(cè)試系統(tǒng)設(shè)計(jì)

辛光,伍川輝

(西南交通大學(xué)機(jī)械工程學(xué)院,四川成都 610031)

為滿足高速動(dòng)車組車內(nèi)噪聲試驗(yàn)的需求,設(shè)計(jì)一種基于DSP的噪聲測(cè)試系統(tǒng),對(duì)測(cè)試系統(tǒng)的設(shè)計(jì)方案以及軟硬件實(shí)現(xiàn)進(jìn)行介紹。系統(tǒng)由控制部分和運(yùn)算部分組成:控制部分以高性能、低功耗的基于ARM Cortex-M3內(nèi)核的微控制器STM32F103ZET6為核心,擴(kuò)展了A/D采集模塊、NAND Flash存儲(chǔ)模塊以及藍(lán)牙通信模塊;運(yùn)算部分以TI公司的低功耗DSP芯片TMS320VC5509A作為核心,負(fù)責(zé)對(duì)采集的噪聲數(shù)據(jù)進(jìn)行實(shí)時(shí)處理,并把結(jié)果交給ARM發(fā)送給上位機(jī),以實(shí)現(xiàn)對(duì)試驗(yàn)效果的實(shí)時(shí)觀察;ARM與DSP通過雙端口RAM相連接,使得兩種處理器間的頻率差異得到解決并能有效地實(shí)現(xiàn)數(shù)據(jù)交換。實(shí)驗(yàn)證明:基于DSP的噪聲測(cè)試系統(tǒng)能很好地滿足高速動(dòng)車組車內(nèi)噪聲試驗(yàn)對(duì)噪聲數(shù)據(jù)采集和實(shí)時(shí)處理的需求。

測(cè)試系統(tǒng);DSP;ARM Cortex-M3內(nèi)核;高速動(dòng)車組;車內(nèi)噪聲;雙口RAM

0 引言

近年來我國的高速鐵路事業(yè)迅速發(fā)展,在提高列車運(yùn)行速度的同時(shí),帶來的噪聲污染也在加劇,噪聲已經(jīng)成為了評(píng)價(jià)高速鐵路對(duì)環(huán)境影響的主要指標(biāo)之一[1-2]。隨著人們生活水平的提高,對(duì)環(huán)境重視程度也不斷加大,車內(nèi)噪聲會(huì)直接影響到乘客乘坐列車的舒適度[3]。列車噪聲的測(cè)試和研究對(duì)噪聲來源、分布以及聲振關(guān)系的明確有著重要意義[4],也為優(yōu)化動(dòng)車組的設(shè)計(jì)提供了依據(jù)。針對(duì)傳統(tǒng)的基于工控機(jī)的噪聲測(cè)試系統(tǒng)存在可擴(kuò)展性差、體積大安裝不方便以及信號(hào)線長(zhǎng)抗干擾性差等缺點(diǎn),本系統(tǒng)介紹基于DSP的噪聲測(cè)試系統(tǒng),ARM單元負(fù)責(zé)數(shù)據(jù)的采集、存儲(chǔ)、與上位機(jī)通信,能實(shí)現(xiàn)多通道采樣和大容量數(shù)據(jù)存儲(chǔ),和上位機(jī)間的通信采用藍(lán)牙方式;DSP單元負(fù)責(zé)數(shù)據(jù)處理,兩個(gè)單元使用雙口RAM的中斷方式進(jìn)行連接,保證了數(shù)據(jù)交換的實(shí)時(shí)性。在處理器選取方面,均選用低功耗、高性能芯片,電路板做好抗干擾設(shè)計(jì),使得系統(tǒng)能適應(yīng)動(dòng)車組運(yùn)行過程中的特殊試驗(yàn)環(huán)境。

1 測(cè)試系統(tǒng)總體方案

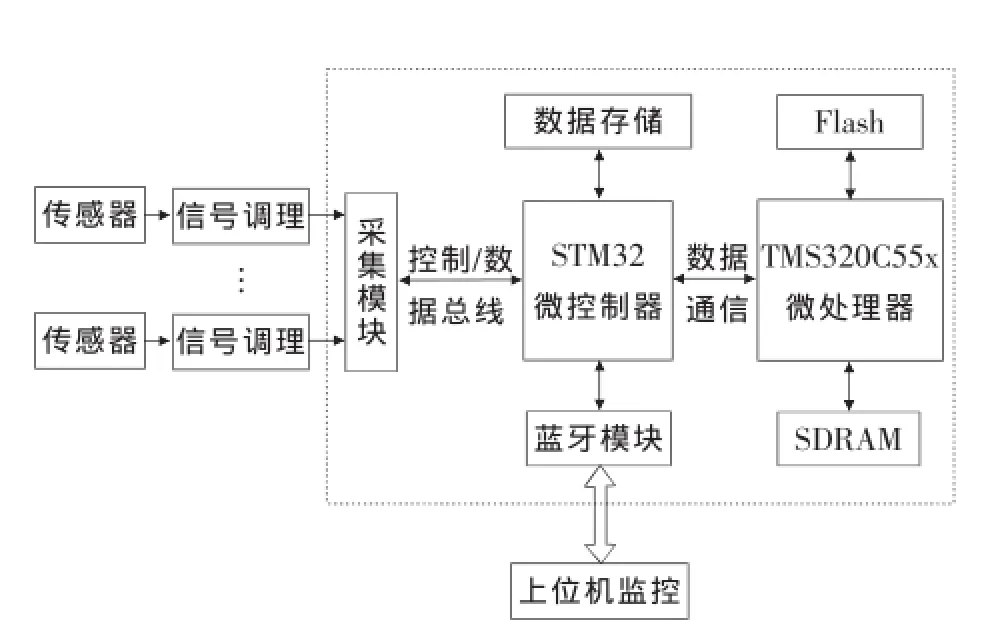

為滿足對(duì)噪聲數(shù)據(jù)的采樣和實(shí)時(shí)處理的要求,噪聲測(cè)試系統(tǒng)采用DSP與ARM的雙CPU構(gòu)架。控制部分由STM32F103ZET6作為主控芯片,通過SPI接口與A/D采集模塊相連,微控制器片內(nèi)自帶的定時(shí)器設(shè)定定時(shí)中斷,控制A/D芯片的采樣頻率,A/D模塊對(duì)經(jīng)調(diào)理過后的傳聲器信號(hào)采樣轉(zhuǎn)換。運(yùn)算部分由TMS320VC5509A作為主處理器,STM32將采集上來的數(shù)據(jù)寫入雙口RAM中并寫相應(yīng)的地址用以觸發(fā)DSP端的中斷,雙口RAM以中斷方式通知DSP取數(shù)據(jù)。DSP在完成噪聲算法過后,將結(jié)果寫入雙口RAM中,也同樣的寫相應(yīng)的地址觸發(fā)ARM端的中斷,ARM在接到中斷后讀取處理好的結(jié)果并由藍(lán)牙發(fā)送給上位機(jī),從而完成對(duì)試驗(yàn)的實(shí)時(shí)監(jiān)測(cè)。噪聲的原始數(shù)據(jù)儲(chǔ)存于本地NAND Flash中,用以后續(xù)的分析處理。系統(tǒng)總體框圖如圖1所示。

圖1 系統(tǒng)總體框圖

2 硬件設(shè)計(jì)

2.1 芯片選型

STM32F103ZET6為意法半導(dǎo)體(ST)公司推出的基于ARM Cortex-M3內(nèi)核的一款高性能芯片,它的封裝為L(zhǎng)QFP144腳,最高的工作頻率能達(dá)到72MHz,片上集成的存儲(chǔ)器有512K的Flash存儲(chǔ)器和64K的SRAM存儲(chǔ)器[5]。芯片有豐富的外設(shè):多達(dá)11個(gè)定時(shí)器,以及CAN、SDIO、SPI、USART、USB等多達(dá)13個(gè)通信接口。擁有可變靜態(tài)存儲(chǔ)控制器FSMC,能夠方便的與SRAM、NAND Flash和NOR Flash等連接,用以外擴(kuò)存儲(chǔ)器。片內(nèi)配置獨(dú)立看門狗和窗口看門狗,使得系統(tǒng)運(yùn)行得以保障。相比ARM7,Cortex-M3使用單一的Thumb-2指令集[6],使得代碼密度與處理性能都兼顧并且易于使用。在高度集成外設(shè)的同時(shí)也兼顧低功耗,STM32F103ZET6支持3種低功耗模式,可以對(duì)所需要使用的時(shí)鐘進(jìn)行單獨(dú)的使能控制,以優(yōu)化功耗。在具有高性能的同時(shí)還有低成本的和易開發(fā)的優(yōu)點(diǎn),使其具有極高的性價(jià)比和很高的應(yīng)用價(jià)值。

TMS320VC5509A是TI公司推出的繼C54x后的新型產(chǎn)品[7],C55x與C54x源代碼兼容。相比C54x,C55x擁有更為卓越的性能,核心頻率從C54x的120MHz提高到了300MHz,性能提高了5倍,C55x的功耗降低到0.05MW/MIPS。片內(nèi)配置6通道直接存儲(chǔ)器存取控制器DMA,擁有外部存儲(chǔ)器接口EMIF,能夠與EPROM、SRAM等異步存儲(chǔ)器以及同步DRAM進(jìn)行無縫連接。

2.2 數(shù)據(jù)采集模塊

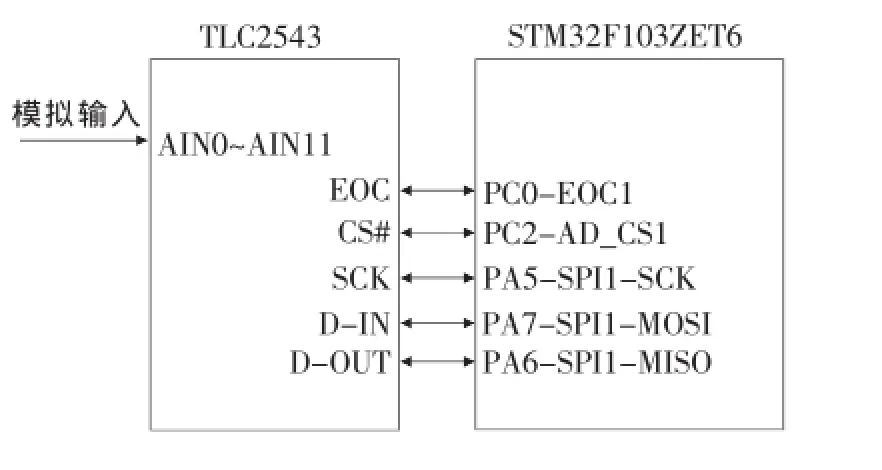

系統(tǒng)選用12位逐次比較型A/D轉(zhuǎn)換芯片TLC2543。TLC2543最高的采樣頻率能達(dá)到66kS/s,能提供11個(gè)采樣通道的輸入,本設(shè)計(jì)中使用2個(gè)通道采集噪聲數(shù)據(jù),能夠滿足系統(tǒng)需求。TLC2543采用4線制串行接口,能與微控制器的SPI總線接口無縫連接,STM32通過兩個(gè)SPI控制器可連接兩片TLC2543以獲得22個(gè)采樣通道。微控制器與A/D芯片連接如圖2所示。

圖2 微控制器與A/D芯片的連接圖

2.3 藍(lán)牙通信模塊

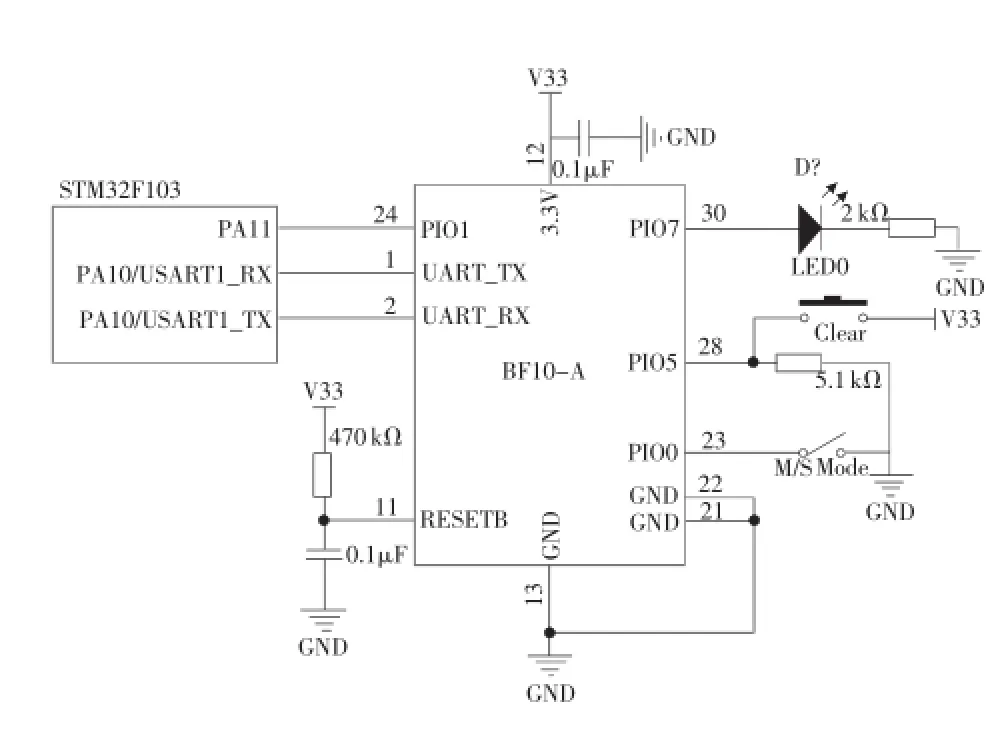

下位機(jī)與上位機(jī)之間的通信運(yùn)用藍(lán)牙方式,系統(tǒng)選用藍(lán)牙模塊BF10-A,該模塊基于BlueCore4-Ext芯片,完全兼容藍(lán)牙2.0規(guī)范。支持Uart接口,用來和微控制器連接。可以選擇的配置為主/從模塊,使用AT指令方式,可方便地修改模塊的藍(lán)牙名稱、配對(duì)碼、及波特率等。藍(lán)牙模塊與STM32的連接如圖3所示,其中BF10-A的PIO1口為藍(lán)牙連接狀態(tài)腳,當(dāng)連接成功時(shí)為高電平,接STM32的通用I/O以便設(shè)備監(jiān)控連接狀態(tài)。

2.4 ARM與DSP連接電路

圖3 藍(lán)牙模塊連接圖

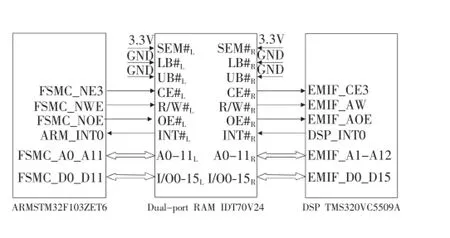

圖4 ARM與DSP雙口RAM通信方式連接圖

測(cè)試系統(tǒng)需要實(shí)時(shí)地進(jìn)行噪聲算法,ARM把采集上來的數(shù)據(jù)交由DSP處理,DSP再將處理結(jié)果送回ARM。ARM與DSP使用較多的通信方式主要有主機(jī)接口(HPI)方式、總線方式以及雙口RAM方式。HPI主機(jī)接口,是TI高性能DSP上配置的與主機(jī)進(jìn)行通信的片內(nèi)外設(shè)。主機(jī)是HPI的主控者,HPI作為一個(gè)外設(shè)與主機(jī)相連[8]。這種方式連線簡(jiǎn)單、體積小,但邏輯比較復(fù)雜,增加了應(yīng)用的難度。總線方式一般采用I2C、SPI等串行接口,其硬件連接簡(jiǎn)單,若片上有I2C、SPI外設(shè),則編程就會(huì)比較簡(jiǎn)單,作為串行傳輸,適合少量數(shù)據(jù)交換,穩(wěn)定性和傳輸速率不高。系統(tǒng)采用雙口RAM方式實(shí)現(xiàn)處理器間的數(shù)據(jù)交換,邏輯簡(jiǎn)單并且能很好解決ARM與DSP間頻率匹配問題[9]。

雙口RAM選用IDT公司的IDT70V24雙口RAM,大小為4KB,位寬為16b,工作電壓3.3V,最快存取時(shí)間25ns,滿足數(shù)據(jù)的高速存儲(chǔ)。它可以左、右兩個(gè)端口同時(shí)讀寫數(shù)據(jù),每個(gè)端口有屬于自己的獨(dú)立數(shù)據(jù)線、地址線和控制信號(hào)線。為避免左右端口控制器因占用RAM存儲(chǔ)區(qū)而產(chǎn)生競(jìng)爭(zhēng),雙口RAM提供了硬件仲裁、中斷仲裁和信號(hào)燈仲裁3種仲裁方式,與BUSY、SEM和INT 3個(gè)左右邏輯交互接口。本系統(tǒng)選擇中斷仲裁方式,具體實(shí)現(xiàn)過程為:雙口RAM的兩個(gè)特定的地址單元被用作“郵箱”,通過對(duì)特定地址單元的寫入和讀取,實(shí)現(xiàn)對(duì)RAM占用信息傳遞。當(dāng)右側(cè)端口在右側(cè)信息位FFE寫入數(shù)據(jù)時(shí),左側(cè)中斷INTL被觸發(fā),要清這個(gè)中斷,左側(cè)端口需讀這個(gè)信息位;同樣當(dāng)左側(cè)端口在左側(cè)信息位FFF寫入數(shù)據(jù)時(shí),右側(cè)中斷INTR被觸發(fā),右側(cè)端口通過讀這個(gè)信息位清中斷。ARM與DSP雙口RAM通信方式連接如圖4所示。

3 軟件設(shè)計(jì)

3.1 數(shù)據(jù)采集程序設(shè)計(jì)

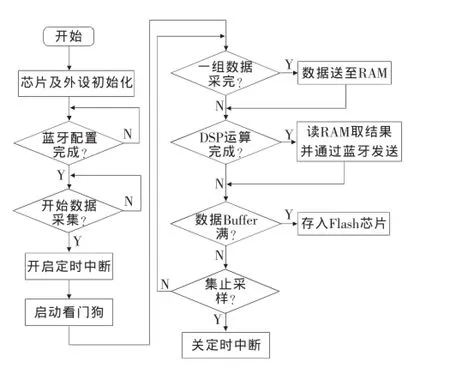

ARM系統(tǒng)的軟件編程使用的編譯環(huán)境為Keil MDK,有強(qiáng)大的仿真能力,能觀察外設(shè)的運(yùn)行狀況并且提供虛擬邏輯分析儀等功能,這些特性使調(diào)試很方便。系統(tǒng)的數(shù)據(jù)采集部分由ARM芯片控制,STM32自帶通用定時(shí)器(TIMx),通過對(duì)定時(shí)器的配置,使其產(chǎn)生定時(shí)中斷,以中斷來觸發(fā)采樣,就能通過設(shè)置定時(shí)中斷的頻率來確定采樣頻率。STM32通過SPI口連接LTC2543,并且把控制字通過DATA INPUT引腳傳入TLC2543來控制采樣,在每個(gè)定時(shí)中斷向?qū)慣LC2543命令字以采樣。為了減少CPU開銷,配置STM32片內(nèi)的DMA來搬運(yùn)采樣數(shù)據(jù),采樣數(shù)據(jù)送雙口RAM通知DSP完數(shù)據(jù)處理算法運(yùn)算,原始數(shù)據(jù)存入一個(gè)Buffer中,待Buffer滿后寫入NAND Flash保存,以備后續(xù)的詳細(xì)數(shù)據(jù)處理。數(shù)據(jù)采集程序放在TIM2定時(shí)器的中斷服務(wù)子程序中,完成對(duì)通道的掃描采樣和數(shù)據(jù)保存。ARM部分主程序流程如圖5所示。

圖5 數(shù)據(jù)采集主程序流程圖

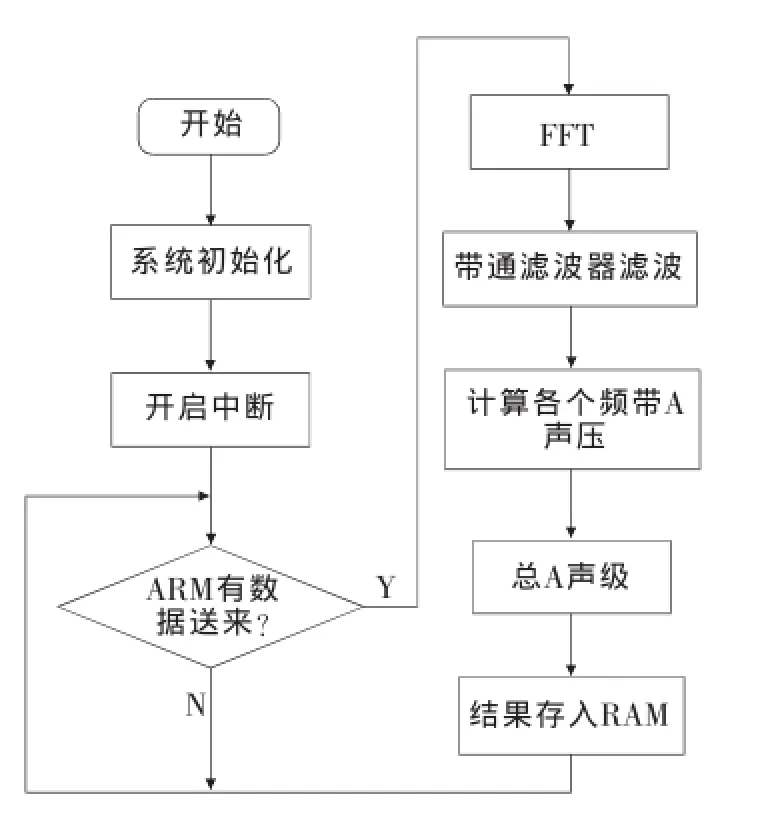

3.2 DSP運(yùn)算程序設(shè)計(jì)

DSP的程序流程如圖6所示。

圖6 DSP程序流程圖

DSP主要是進(jìn)行數(shù)據(jù)處理,完成特定的噪聲算法,當(dāng)ARM有數(shù)據(jù)采集好了送來時(shí),會(huì)寫雙口RAM相應(yīng)的“郵箱”,此時(shí)會(huì)觸發(fā)雙口RAM另一側(cè)的中斷信號(hào),DSP在接到中斷時(shí),就從RAM中讀取數(shù)據(jù),并開始數(shù)據(jù)的實(shí)時(shí)處理,把結(jié)果送回雙口RAM中通知另一側(cè)的ARM取結(jié)果,ARM取到結(jié)果后就通過藍(lán)牙方式發(fā)送給上位機(jī),這樣試驗(yàn)過程就能隨時(shí)觀察試驗(yàn)的效果。其程序流程就是一個(gè)主循環(huán),判斷中斷標(biāo)志來確認(rèn)是否進(jìn)行噪聲算法。

4 試驗(yàn)結(jié)果

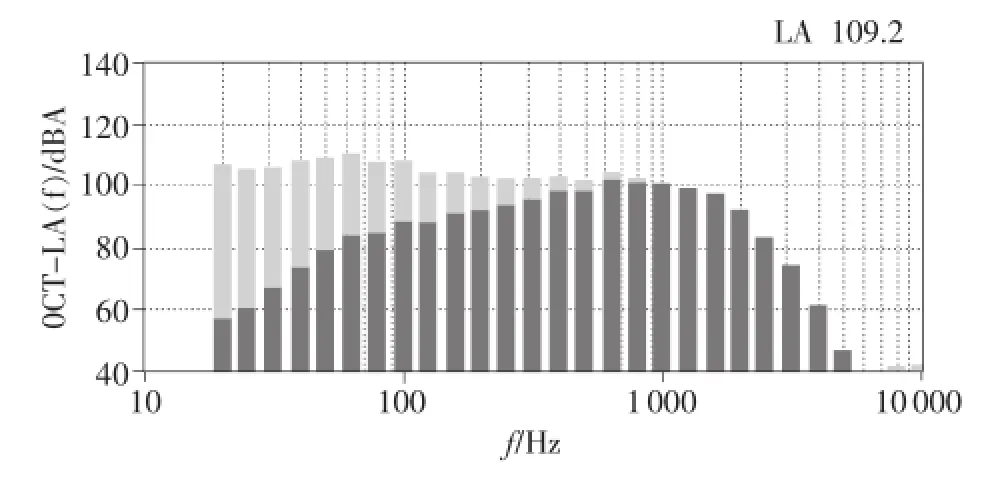

系統(tǒng)上位機(jī)實(shí)時(shí)監(jiān)控程序,通過藍(lán)牙接收下位機(jī)運(yùn)算結(jié)果,達(dá)到在試驗(yàn)過程中觀察結(jié)果的目的。監(jiān)控程序完成試驗(yàn)數(shù)據(jù)采集和儲(chǔ)存,主要獲得的參數(shù)包括1/3倍頻程、A計(jì)權(quán)聲級(jí)等。圖7所示為監(jiān)控程序顯示的列車某測(cè)點(diǎn)的1/3倍頻程譜圖,圖8所示為后續(xù)分析得出的列車某測(cè)點(diǎn)在不同速度下的噪聲譜圖。

圖7 列車某測(cè)點(diǎn)的1/3倍頻程譜圖

圖8 列車某測(cè)點(diǎn)在不同速度下的噪聲譜圖

5 結(jié)束語

基于DSP的高速動(dòng)車組車內(nèi)噪聲測(cè)試系統(tǒng),能夠?qū)崿F(xiàn)噪聲數(shù)據(jù)的實(shí)時(shí)采集與分析,其高性能、低功耗特性滿足動(dòng)車運(yùn)行環(huán)境下的測(cè)試需求,對(duì)噪聲的檢測(cè)提供了可行的方案,對(duì)噪聲研究和評(píng)價(jià)起到重要作用。系統(tǒng)結(jié)構(gòu)靈活,運(yùn)行穩(wěn)定,有很好的應(yīng)用價(jià)值。

[1]孫大新,高亮.高速鐵路輪軌噪聲及其控制措施[J].中國安全科學(xué)學(xué)報(bào),2005(11):88-90.

[2]周君.高速鐵路建設(shè)過程中如何治理噪聲污染的研究[J].鐵道工程學(xué)報(bào),2001(1):28-30.

[3]范蓉平,孟光,孫旭,等.基于心理聲學(xué)響度分析的高速列車車內(nèi)噪聲評(píng)價(jià)[J].振動(dòng)與沖擊,2005(5):46-48.

[4]邢淑梅,劉巖,張曉排.高速鐵路動(dòng)車組噪聲測(cè)試與分析[J].噪聲與振動(dòng)控制,2009(3):79-81.

[5]王永虹,徐煒,郝立平.STM32系列ARM Cortex-M3微控制器原理與實(shí)踐[M].北京:北京航天航空大學(xué)出版社,2008(7):47-56.

[6]Yiu J.ARM Cortex-M 3權(quán)威指南[M].北京:北京航空航天大學(xué)出版社,2009:28-29.

[7]汪春梅,孫洪波.TMS320VC55X DSP原理及應(yīng)用[M].3版.北京:電子工業(yè)出版社,2011:10-59.

[8]胡慶鐘,李小剛,吳鈺淳.TMS320C55x DSP原理、應(yīng)用和設(shè)計(jì)[M].北京:機(jī)械工業(yè)出版社,2006(1):200-203.

[9]翁奇財(cái),王維.嵌入式系統(tǒng)中CPU之間通信方式的比較[J].聲學(xué)與電子工程,2008(4):38-39.

High-speed EMUs interior noise test system based on DSP

XIN Guang,WU Chuan-hui

(School of Mechanical Engineering,Southwest Jiaotong University,Chengdu 610031,China)

In order to meet the demand of interior noise tests for high-speed EMUs,a DSP-based noise test system was designed.The system consists of the control part and the computation section.High-performance and low power consumption control part takes ARM Cortex-M3 corebased microcontrollers STM32F103ZET6 as the core and extends A/D acquisition module,NAND Flash memory module,and Bluetooth communication module.Computing part takes TI’s lowpower DSP chips TMS320VC5509A as the core and it is responsible for collecting the noise data in real-time processing,and sending the results to the host computer through the ARM in order to achieve real-time observation of the test results.ARM and DSP were connected with the dualport RAM,which made the frequency differences between two processors resolved with effective data exchange.Experimental results show that the noise test system based on DSP can meet the demands of noise data acquisition and real-time processing for high-speed EMUs interior noise test.

test system;DSP;ARM Cortex-M3 corebased;high-speed EMUs;vehicle interior noise;dual-port RAM

TP216+.2;U292.91+4;TB535;TP274+.2

A

1674-5124(2013)03-0084-04

2012-05-11;

:2012-07-20

“十一五”國家科技支撐計(jì)劃項(xiàng)目(2009BAG12A01)作者簡(jiǎn)介:辛光(1986-),男,四川成都市人,碩士研究生,專業(yè)方向?yàn)樽詣?dòng)化測(cè)試技術(shù)與PC儀器。