利用WinDriver實現鏈式DMA

黃世中 , 金志剛

(1.天津大學 天津 300072;2.河北省科學院 應用數學研究所,河北 石家莊 050081;3.河北省信息安全認證工程技術研究中心 河北 石家莊 050081)

利用WinDriver實現鏈式DMA

黃世中1,2,3, 金志剛1

(1.天津大學 天津 300072;2.河北省科學院 應用數學研究所,河北 石家莊 050081;3.河北省信息安全認證工程技術研究中心 河北 石家莊 050081)

PCI Express協議由于其高速串行、系統拓撲簡單等特點被廣泛用于各種領域。Altera公司的Arria II GX FPGA內集成了支持鏈式DMA傳輸功能的PCI Express硬核,適應了PCI Express總線高速度的要求。文中利用Jungo公司的WinDriver軟件實現了鏈式DMA的上層應用設計。首先給出了鏈式DMA實現的基本過程,接著分析了鏈式DMA數據傳輸需要處理的幾個問題,給出了相應的解決辦法和策略。采用這些方法,保證了DAM數據傳輸的正確性,簡化了底層FPGA應用邏輯的設計。

鏈式DMA;WinDriver;PCI Express;端點存儲器

在計算機與外設的通訊過程中,DMA方式,即Direct Memory access(直接內存訪問),由于無需計算機CPU的干預就可以在內存和外設之間傳輸數據,是一種高效的數據交換方式。因為對于高速的設備,如PCI Express接口的板卡設備,如果采用普通方式在存儲器和外設之間傳輸大量的數據將占用太多的CPU時間,嚴重影響系統的性能。而使用DMA方式則使傳輸數據的操作中CPU的涉及減小到最少。

要實現DMA的傳輸功能,在底層需要硬件本身具有這樣的功能模塊,即外設硬件可以主動發起數據傳輸。在上層則需要驅動與應用接口的配合。

文中給出如下的一種DMA傳輸方式的實現。硬件外設是基于Altera公司PCI Express硬核的FPGA加密卡,其與主機的接口采用是PCI Express接口。上層則采用了Jungo公司的WinDriver軟件提供的驅動和API接口。

1 鏈式DMA

PCI Express是用來互聯諸如計算機和通信平臺應用中外圍設備的第三代高性能I/O總線[1]。與原有的PCI并行總線相比,它沒有大量的數據和控制線,對于硬件電路設計者來說,省去了很多硬件設計工作。PCI Express的傳輸速度遠遠大于PCI總線,PCI Express 1.1版本單個鏈路的單向吞吐量能達到250 MB/s。對于需要與主機進行大容量傳輸的系統來說,該總線標準的優勢是非常明顯的。Altera公司的Arria II GX系列器件內建PCI Express硬核,無需PHY和IP核,有利于節約FPGA資源,簡化了PCI Express的接口設計。同時在用Quartus II軟件生成的基于PCI Express硬核的樣本工程中,集成了對DMA的支持功能[2],為進一步的硬件產品開發提供了基礎。

實際應用中,DMA的傳輸方式可分為兩種:簡單DMA和鏈式DMA。簡單DMA只需要主機告訴設備要傳輸數據的主機地址、設備地址和傳輸數據的長度,然后啟動DMA傳輸即可。但簡單DMA每進行一次傳輸,都要進行上面的設置,效率較低。

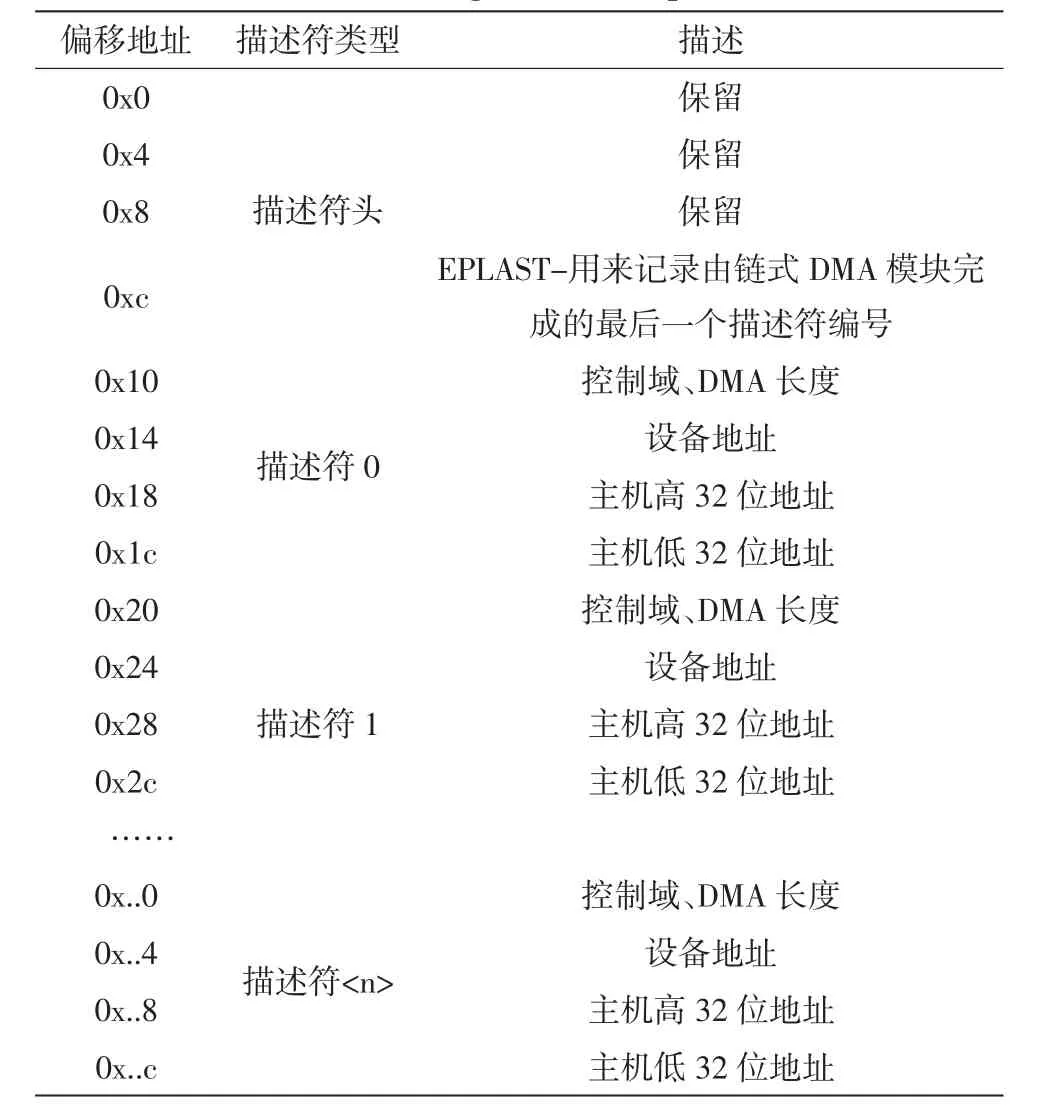

在用 Quartus II軟件的 MegaWizard Plug-In Manager工具生成的基于PCI Express硬核的樣本工程中,實現了一個32 KB的帶有字節寫使能控制的雙端口RAM的端點存儲器,其讀寫數據總線寬度均為128位;并且實現了鏈式DMA的傳輸功能。這是一種效率遠遠高于簡單DMA的傳輸方式,它只需要1次啟動操作,就可以完成多次DMA傳輸。具體實現的方法是:在主機端,需要開辟一塊內存區域,用來存儲描述符表。所謂描述符表,是用來描述在主機與外設之間數據傳輸有關的地址與長度信息的,它由一個表頭和多個描述符組成,其中每一個描述符對應一次DMA操作。用戶根據自己的需求填寫該描述符表,如下表所示。

表1 鏈式DMA描述符表Tab.1 Chaining DMA descriptor table

在上表中,偏移地址是指到描述符表內存區域開始處的字節偏移地址。DMA長度用來設置本描述符對應的DMA傳輸的長度,是以32位雙字為單位的。主機地址用來指示數據在主機端存放的位置。設備地址用來指示數據在設備的端點存儲器中存放的位置。控制域用來控制在該描述符傳輸完成時設備是否更新描述符頭的EPLAST域。

使用鏈式DMA傳輸數據時,主機首先通過設置DMA控制寄存器,告訴設備要傳輸數據的描述符表的起始地址和描述符的個數,然后啟動DMA傳輸。設備收到啟動DMA傳輸的命令后,首先根據主機提供的描述符表信息,檢索相應的描述符,并存儲到設備的FIFO中,然后根據每一個描述符中的地址和長度信息,進行相應的DMA數據傳輸。所有的DMA描述符處理完成后,設備更新描述符頭的EPLAST域。主機便可通過查詢EPLAST域獲得鏈式DMA傳輸完成的信息,從而可以啟動下一次鏈式DMA傳輸。

2 WinDriver中的DMA功能

WinDriver是Jungo公司提供的一種通用的驅動開發支持軟件,它簡化了用戶的上層驅動開發和應用接口開發,而且易于再封裝,實現商業化應用。該軟件提供了對PCI Express接口設備的驅動支持,而且也提供了對DMA實現功能的支持[3]。

WinDriver提供了兩種DMA緩沖區的分配方式,即連續緩沖區和分散/聚合緩沖區。前者當用戶申請緩沖區時,分配的是一個物理地址連續的內存塊;而后者分配的緩沖區在物理位置上可以是分段的,這些物理上不連續的內存段通過虛擬地址空間映射給用戶的是一個在應用層連續的緩沖區。

由于采用DMA傳輸數據時,設備需要的主機地址是物理地址;而在主機端,申請大塊的物理地址連續的內存區域往往是非常困難的。因此在使用DMA進行大量數據傳輸時,主機端使用分散/聚合緩沖區分配方式更方便和易于實現。此時,主機可以將緩沖區的每個內存段對應一個描述符,這樣采用鏈式DMA方式可以解決大的內存區域物理地址不連續的問題,方便了大存儲區域數據的傳輸。

3 具體實現

在具體實現時,主機是通過訪問的設備的BAR2地址空間來設置DMA控制寄存器的。DMA控制寄存器分為DMA讀控制寄存器和DMA寫控制寄存器,它們均是由4個32位的雙字組成,依次表示的含義是:控制域和描述表中描述符的個數、描述符表的高32位地址、描述符表的低32位地址、最后一個描述符的索引,其中第一個雙字的控制域部分用來控制在每個描述符傳輸完成時設備是否更新主機描述符頭的EPLAST域。DMA寫(即數據由設備向主機傳送)控制寄存器的開始地址位于BAR2地址空間的0字節偏移地址處,DMA讀(即數據由主機向設備傳送)控制寄存器的開始地址位于BAR2地址空間的16字節偏移地址處。主機可以通過調用WinDriver提供的API函數 WDC_WriteAddr32每次設置DMA讀/寫控制寄存器的一個雙字。

在每次DMA傳輸開始時,根據設備DMA的設計要求,必須先調用WDC_WriteAddr32函數向DMA讀/寫控制寄存器的第一個雙字寫入0xFFFF的內容,以使設備DMA進入到可以工作的狀態。這是因為設備每次執行完DMA操作后,處于停止工作狀態,只有通過對控制寄存器的第一個雙字寫0xFFFF才能使設備DMA模塊退出停止狀態,重新準備檢索DMA描述符。詳見樣本工程的altpcierd_dma_descriptor模塊的狀態機部分。

需要注意的是,描述表的描述符中的主機低32位地址必須是16的倍數,設備地址也必須是16的倍數。這是因為設備的端點存儲器是一個帶有字節寫使能控制的RAM,且其每個周期讀寫16個字節的數據。對于DMA讀操作來說,設備收到主機的帶數據的完成包后,是根據主機端的地址設置端點存儲器的字節寫使能控制信號的。如果主機端地址的低4位與設備端地址的低4位不一致,將導致數據起始存儲位置不正確。例如:如果主機端地址的低4位是8,設備端地址的低4位是0,端點存儲器寫的數據總線接收數據的第一有效時鐘周期內接收的16字節數據,低8字節對應的字節使能位是0,高8個字節才是有效的數據。這些有效數據被寫入端點存儲器規定存儲位置向后偏移8個字節的地方,這顯然與設備要求的存儲位置不符。

對于DMA寫操作來說,設備從端點存儲器中讀取數據時,直接將設備地址的低4位丟棄了,所以設備地址也應為16的倍數。如果主機端地址低32位不是16的倍數,根據設備的Descriptor/Data Interface處理規則和PCI Express規范中存儲器寫事務包的處理規則,將導致主機收到的數據包的有效數據位置向后偏移,部分有效數據丟失,例如:如果主機端低32位地址的低4位是8,那么將使得從端點存儲器讀取的數據的前8個字節丟失,主機端收到的數據的開始位置比預期位置向后移了8個字節。

在設置主機的描述表時,先調用WinDriver提供的API函數WDC_DMASGBufLock對申請的進行DMA數據傳輸的內存塊進行鎖定,然后根據鎖定的頁數,確定描述表中描述符的個數,每個描述符對應其中的1頁存儲區域。根據上面對主機低32位地址的要求,在申請進行DMA傳輸的內存區域時,申請的空間大小可以比實際需要存儲區域多16個字節。這樣,在調用WDC_DMASGBufLock函數對申請的內存塊進行鎖定后,如果第一頁的物理地址不是16的倍數(在多頁的情況下,后面的頁的物理地址均為16的倍數),可以DMA傳輸的實際區域向后移動相應的位置,以使數據存儲的開始位置的物理地址為16的倍數。例如,如果第1頁物理地址的低4位是4,那么可以向后移動12個字節作為DMA傳輸的開始位置。如果申請的空間由多頁組成,應注意第1頁對應的描述符傳輸數據的長度將減少,及對后面頁對應描述符的設備地址的影響。

設置完成DMA傳輸的描述符表后,需要通過設置DMA控制寄存器,告訴設備主機描述表的起始物理地址和描述符的個數。這里,也有上面類似的要求。即要求描述表的低32位地址為16的倍數,否則將導致設備FIFO每個周期接收的描述符不是一個完整的描述符,即可能是由前一個描述符的后8字節和后一個描述符的前8字節組成。這將導致以后DMA數據傳輸的混亂和錯誤。為此,在調用WDC_DMASGBufLock函數對描述符表存儲區域進行鎖定時,可以進行上面類似的地址對齊處理。

因為在調用WDC_DMASGBufLock函數對一塊存儲區域進行鎖定時,中間頁的大小均是4 KB的倍數[4]。這樣就可以估算出一塊內存區域大概可以分成幾頁,從而估計出描述符表由幾個描述符組成。比如文中的設備存儲器是一個32 KB的端點存儲器,因此進行一次DMA傳輸的描述符個數不超過9個,描述符表占用的存儲空間為:16+9*16=160字節。對于這種描述表所需空間少于2 KB的情況下,可以采用如下策略使得描述表的數據集中到一個物理頁中,以便于對DMA控制寄存器的設置,即如果所需空間為x(x≤2032)字節,那么申請 2(x+16)字節 (≤4 KB)的空間,這樣在調用WDC_DMASGBufLock函數進行存儲區域鎖定時,得到的頁數最多為2頁,且至少有一頁的大小不小于x+16字節。于是,便可用此頁作為描述符表的存儲區域,并使描述符表的起始地址滿足16的倍數的要求。

按照上面的策略,一次DMA傳輸至少可以處理含有(2032-16)/16=126個描述符的描述符表,至少可以傳輸124*4 KB=496 KB大小的數據。如果DAM傳輸的數據很多時,可以分成多次DMA傳輸,這樣仍可使每次DMA傳輸時,描述表的數據占用一個物理頁。

上面的策略,也可應用于DMA數據存儲區的設置。例如在我們進行的加密卡設計中,使用DMA寫模塊完成加密結果的輸出。對于公鑰算法,其加密結果的長度往往是固定的,比如,對2 048位的RSA簽名運算,其簽名結果長度為256字節。此時采用上面的策略,我們就可以通過一次DMA傳輸讀到簽名結果,這樣就簡化了底層設備對輸出接口的設計。

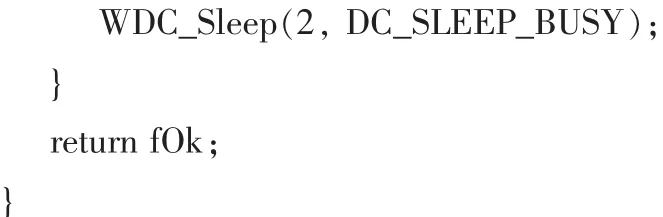

在設置完DMA控制寄存器后,設備開始進行MDA描述符檢索,然后開始進行數據傳輸,主機需要知道什么時候數據傳輸結束,以便進行其他處理或讀取傳輸結果。有兩種處理方式:中斷方式和查詢方式。由于Windows XP操作系統不支持消息中斷請求(MSI),故采用查詢的方式處理。這就需要設置描述符的控制域和DMA控制寄存器的控制域部分,以使設備更新描述符表的EPLAST域。需要指出的是:在設備DMA處理模塊的實現中,描述表的描述符頭中,最后一個雙字的低16位是EPLAST域的實際值,即最后完成的描述符的索引號,而高16位是其他的信息。因此可以用下面的DMAWaitForCompletion函數進行查詢處理。

在上面的函數中hDev為設備句柄;DT_HEAD_EPLAST為描述表的描述符頭中,最后一個雙字的地址指針;eplast_num為DMA傳輸的最后一個描述符的索引號,等于描述符表中描述符個數減1。函數的返回值為真,表示DMA傳輸正確完成。

為了使DMA緩沖區保持與CPU緩存、I/O緩存的同步,主機端應在設置DMA控制寄存器之前,對DMA傳輸的數據存儲區和描述符表存儲區調用WDC_DMASyncCpu函數[5],在完成DMA的傳輸查詢之后,調用WDC_DMASyncIo函數和WDC_DMABufUnlock 函數[5]。

4 結束語

對基于Altera公司PCI Express硬核的鏈式DMA應用,Altera公司雖然提供了上層Demo示例程序[6],但其只進行了MDA傳輸的性能測試。文中給出了處理DMA數據傳輸時,主機端需要面對和解決的幾個問題。通過這些處理方法和策略,保證了主機和設備之間DMA數據傳輸的正確性,簡化了底層FPGA應用的設計,為利用DMA模塊進行用戶的應用邏輯設計提供了基礎。

[1]馬鳴錦,朱劍冰,何紅旗,等.PCI、PCI-X和PCI Express的原理及體系結構[M].北京:清華大學出版社,2007.

[2]PCI Express Compiler User Guide[R].Altera Corporation,2010.

[3]WinDriver PCI/ISA/CardBus User’s Manual[R].Jungo Corporation,2008.

[4]徐洋,史學書,劉明波.基于PCI核的鏈式DMA的設計[J].國外電子測量技術,2008,27(6):42-45.

XU Yang,SHI Xue-shu,LIU Ming-bo.Design of scattergather DMA based on PCI core [J].Foreign Electronic Measurement Technology,2008,27(6):42-45.

[5]劉波,庫錫樹,孫兆林.基于PCIE總線協議的數據采集設備驅動程序實現[J].工業控制計算機,2007,20(7):28-29.

LIU Bo,KU Xi-shu,SUN Zhao-lin.Driver develop of data gathering device based on PCIe[J].Industrial Control Computer,2007,20(7):28-29.

[6]PCI Express High Performance Reference Design[R].Altera Corporation,2010.

Chaining DMA implementation with WinDriver

HUANG Shi-zhong1,2,3, JIN Zhi-gang1

(1.Tianjin Unirersity, Tianjin 300072, China;2.Institute of Applied Mathematics, Hebei Academy of Sciences, Shijiazhuang 050081, China;3.Hebei Authentication Technology Engineering Research Center, Shijiazhuang 050081, China)

The PCI Express protocol has been applied in more and more fields because of its serial high speed characteristic and simple system topology.The Arria II GX device, made by Altera Corporation, has integrated a PCI Express hard IP on itself,which supports chaining DMA transfers and meets the requirements of the high speed of the PCI Express bus.The chaining DMA implementation on the host side is designed using Jungo's WinDriver software.Firstly,the basic framework for the chaining DMA is presented.Then the problems need to be resolved for chaining DMA transfers are analyzed,and the corresponding solutions and strategies are given.By using these methods,not only the correctness of MDA transfers is guaranteed,and the underlying FPGA application logic design is simplified.

chaining DMA; WinDriver; PCI Express; endpoint memory

TP302

A

1674-6236(2013)08-0006-04

2012-12-12稿件編號201212088

河北省科技支撐計劃項目(12210720);河北省科學院重大攻關項目(12620,13605)

黃世中(1973—),男,河北南宮人,博士研究生,副研究員。研究方向:信息安全與密碼學。