一種二相線陣電荷耦合器件的數據采集器設計

高 翔,林金朝,龐 宇,宋得龍

(重慶郵電大學光電工程學院,重慶400065)

0 引言

二相線陣電荷耦合元件(CCD)即電荷耦合器件,是20世紀70年代初發展起來的一種新型半導體集成光電器件。它具有體積小、噪聲低、靈敏度高、可靠性好等特點,被廣泛應用于圖像傳感和非接觸測量等領域[1]。在高速應用時代,傳統的單路CCD已很難滿足高數據率的要求,帶有雙路輸出的二相線陣CCD便應運而生,其數據率可達單路輸出的兩倍。然而,由于輸出信號變成了兩路,導致在對輸出信號進行處理上變得更為復雜。傳統處理方式是將兩路信號分別進行處理,然后再將得到的數據合并在一起。由于本身處理一路信號就包含了濾波、采樣、放大等多個步驟,要處理兩路信號更是大大增加了處理電路的復雜度[2-4]。另外,由于數據量的巨大,要想正確地將兩路數據合并在一起也往往并不那么簡單。本文設計的數據采集系統使用雙路輸出CCD,并通過專門的數據處理器對其雙路信號進行處理,達到了電路簡單,性能可靠,實現方便的效果。

1 設計方案

采用TOSHIBA公司的TCD1703C型二相線陣CCD做模擬數據采集,并用Analog Devices公司的AD9826型信號處理器進行數據處理,實現對待測物的數據采集。TCD1703C具有7 500有效像元,其像元尺寸為7 μm×7 μm×7 μm,像元區總長52.5 mm,響應度為15 V/(lx·s),驅動頻率最大可達到20 MHz。AD9826是一款專門面向CCD的低功耗多通道信號處理器,其雙通道模式尤其適合處理奇偶雙路輸出的CCD信號。它內含最高30 MSPS的相關雙采樣器(CDS)、補償DAC、1~6倍可編程增益放大器(PGA)、16位精度ADC,可以極大地簡化信號處理電路的設計。

設計關鍵在于對CCD和信號處理器的驅動時序的設計。設計驅動時序有很多方法,包括數字邏輯電路、單片機、專用IC以及現場可編輯門陣列(FPGA)等。但數字邏輯電路結構復雜,用到大量計數器、門電路,時序難以配合,電路不穩定,抗干擾能力差,制作修改比較麻煩,體積占用也很大[5]。由于現在CCD驅動對頻率要求越來越高,大多數單片機的頻率都難以達到要求。雖然專用IC功耗低,集成度高,可靠性也好,而且產生的驅動時序也非常好,但價格過于高昂,靈活性也不好。所以,功耗小、成本低、易調試且穩定性好的FPGA成為驅動時序設計的最佳選擇。這里采用Altera的EP2C8Q208型FPGA,其價格適中,具有8 256個邏輯單元,138個I/O管腳,可外接超過50 MHz晶振,資源足以應對本系統的要求。針對FPGA的I/O口輸出電平為3.3 V,而大多數器件對控制驅動往往要求5 V電平的問題,可在后續模塊前端外接CMOS器件予以解決。

系統采用Top-down多層次結構電路的設計方法[6],利用圖形和文本混合進行設計,將系統分為分頻器、CCD驅動時序和信號處理控制時序3個模塊,整體設計框圖如圖1所示。其中,預處理電路包括差分電路和跟隨電路。差分電路通過一個差分放大器抑制掉輸出信號中的5 V直流分量,跟隨電路可以提高信號的負載能力,使信號更穩定。

圖1 整體設計框圖

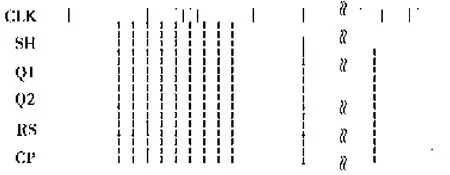

2 CCD驅動時序

TCD1703C的驅動由5路脈沖構成:SH、Q1、Q2、RS、CP。其中,轉移脈沖SH將CCD存儲柵中光積分所產生的光生電荷,并行地分別轉移到光敏區兩側的模擬移位寄存器的電荷勢阱Q1和Q2中。當SH脈沖結束時,SH為低電平,它使存儲柵和模擬移位寄存器隔離。存儲柵和模擬移位寄存器分別工作。存儲柵進行光積分,模擬移位寄存器在驅動脈沖的作用下串行地向輸出端轉移信號電荷,最后由奇數輸出端OS1和偶數輸出端OS2分別輸出,得到OS1信號和OS2信號。RS為復位級的復位脈沖,每復位一次輸出一個信號。CP是鉗位脈沖,用于鉗制輸出信號電平[7]。

由TCD1703C的數據手冊可以看到:其典型最佳工作頻率為1 MHz,5路脈沖的時序如圖2所示。由于該器件是兩列并行輸出,所以在一個SH周期中至少要有7 500/2個Q1脈沖,即TSH>3 750TQ1,而加上前后啞元數后,TSH應至少有3 822個Q1脈沖。另外,SH為高電平的時間應大于1 000 ns,1 MHz時鐘下的典型值為1 500 ns,RS和CP為高電平的持續時間典型值為100 ns。

圖2 TCD1703C驅動脈沖波形圖

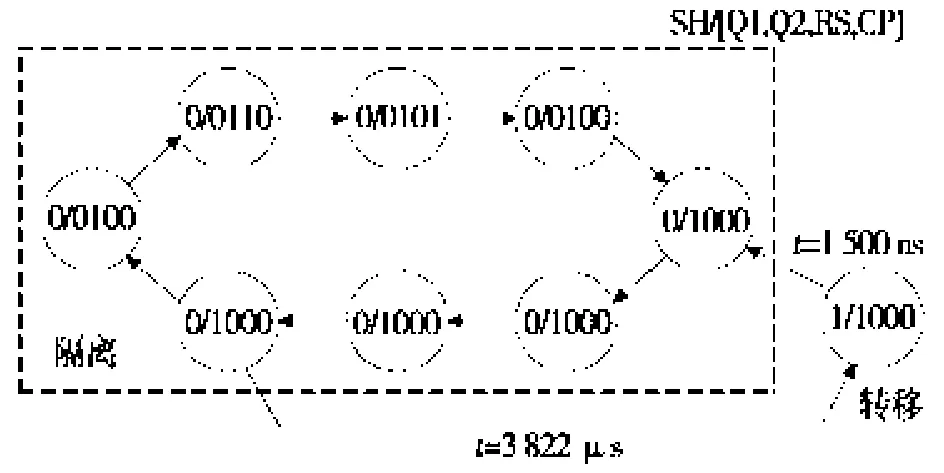

由此,FPGA可選用48 MHz的外部晶振,經六分頻后得到工作時鐘CLK=8 MHz,在CLK的上升沿(即每隔125 ns)每觸發一次狀態機,由計數器控制時間狀態轉換。當滿足3 822 μs后,CCD掃描完一行,這時SH置高進入轉移狀態,[Q1,Q2,RS,CP]保持1000狀態不變。當1 500 ns后SH置低進入隔離狀態,[Q1,Q2,RS,CP]開始輸出狀態序列[8-10]。狀態圖如圖3所示。

圖3 TCD1703C驅動時序狀態圖

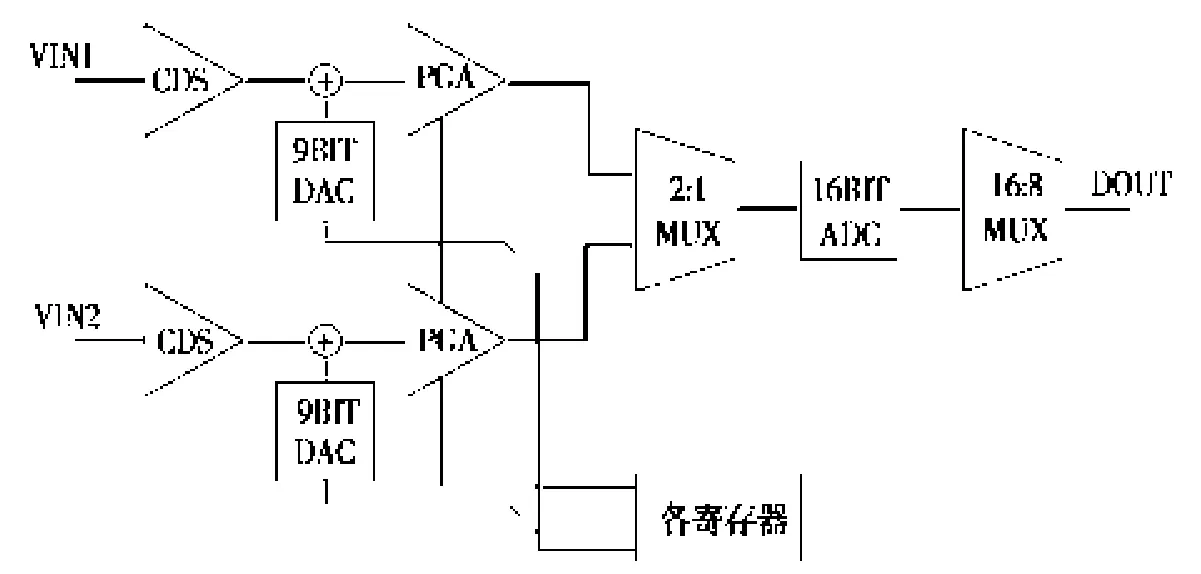

3 AD9826控制時序

AD9826是可編程的信號處理器,內含的相關雙采樣器有兩種采樣模式:CDS和SHA。CDS模式即對待采樣信號的參考電平和數據電平分別采樣的差分輸出,因前端已通過差分電路將TCD1703C的參考電平鉗制在0 V,故可直接將參考電平采樣時序輸入端接地,從而只需進行數據電平采樣,即SHA模式。AD9826工作原理如圖4所示。

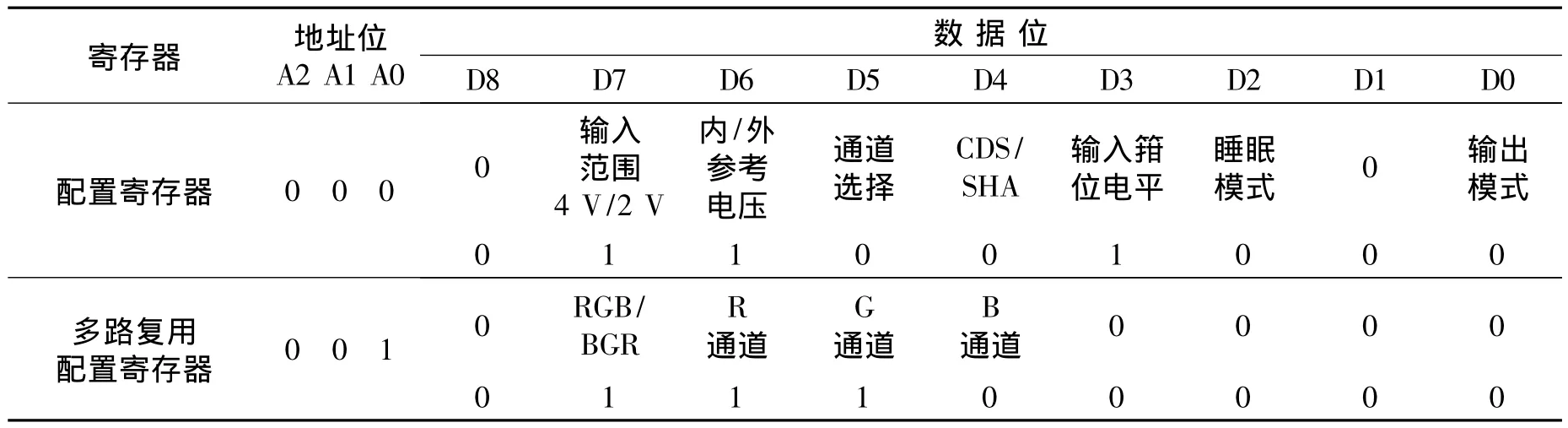

其內含的相關雙采樣器、增益放大器和模數轉換器的具體功能設置,都是通過編程串口配置其內部對應的各相關寄存器來實現的。其中,配置寄存器用來設置AD9826的操作模式和偏置電平;多路復用配置寄存器控制抽樣通道的相關命令和雙通道配置;放大電路增益寄存器有3個,分別設置3個輸入通道的PGA的放大倍數;補償寄存器也有3個,分別設置3個通道的補償電壓。這里只需要配置前兩種寄存器即可[11],具體配置見表1,可通過配置使AD9826工作在16 bit雙通道SHA模式。其中,因CCD輸出信號高低電壓差最大為4 V,故將AD9826的輸入范圍設置為4 V。

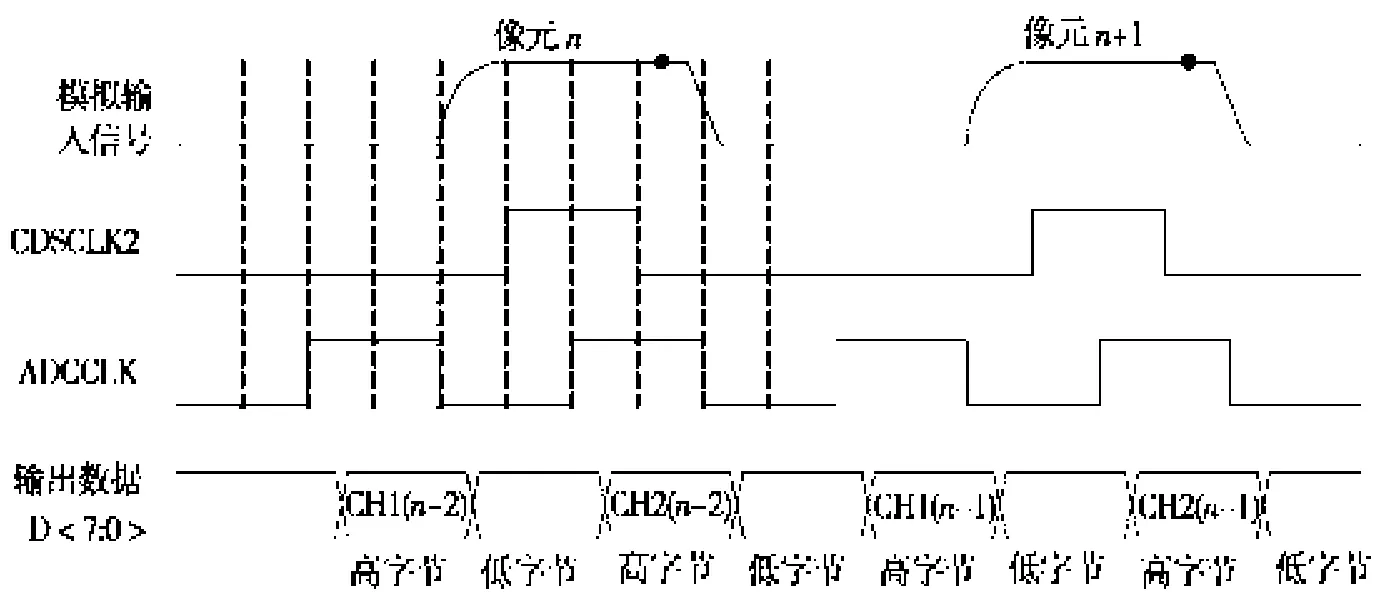

AD9826先在數據電平采樣時鐘CDSCLK2的下降沿分別對兩個通道的輸入信號進行采樣,并將采得的數據依次經過DAC和PGA處理,然后送入16 bit的A/D轉換器,轉換器在ADC采樣時鐘ADCCLK的下降沿對其進行采樣,由于AD9826的輸出只有8位數據線,所以將16 bit信號分成高低兩個8 bit信號分時輸出,如圖4所示。

圖4 AD9826原理圖

表1 相關寄存器配置參數

雙通道SHA模式的采樣時序如圖5所示。由圖5可以看出:AD9826的輸出數據相對采樣點有3個ADCCLK周期的時間延遲。在設計驅動時序時應當注意,CDSCLK2的頻率應與輸入信號相同,而ADCCLK的頻率是輸入信號的兩倍。由于CCD輸出信號頻率為1 MHz,故fCDSCLK2=1 MHz,fADCCLK=2 MHz。另外,由數據手冊[6]可知:CDSCLK2高電平持續時間應大于8 ns,ADCCLK2的下降沿不能位于ADCCLK前一個下降沿之前。

圖5 AD9826的雙通道SHA模式控制時序圖

通過上述分析,該控制時序同樣可由狀態機來實現,如圖6所示。

由TCD1703C輸出特性可知:兩路輸出信號中的有效分量是在Q2下降沿后10 ns輸出,由此便可確定AD9826控制時序與TCD1703C驅動時序間的相位關系。另外,由于TCD1703C正常工作時前后各有64和8個啞元信號,而這72個啞元信號是不需要采樣的。所以,可以在AD9826開始工作時,先用計數器對前64個啞元信號計數,等64個信號全部移出后啟動采樣時鐘,并在采滿3 750個點后中斷采樣時鐘,等待下一個采樣周期的到來。

圖6 AD9826控制時序狀態圖

需要注意的是:由于TCD1703C的輸出信號含有5 V的直流分量,不能滿足AD9826最大4 V的輸入范圍,所以應當在CCD信號輸出后先通過差分電路抑制掉該直流分量,以確保信號處理器的輸入信號為0~4 V。

4 試驗結果與分析

4.1 仿真波形

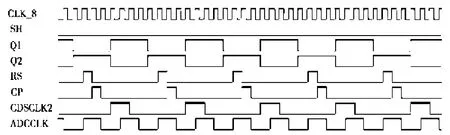

AD9826配置時序如圖7所示,其中,CLK_8為48 MHz外部晶振經分頻器分頻得到的8 MHz工作時鐘,SDATA為數據I/O口,SCLK為配置時鐘,SLOAD為負載脈沖。

圖7 AD9826配置時序

整體控制時序如圖8所示,其中,SH、Q1、Q2、RS、CP為 TCD1703C的驅動時鐘,CDSCLK2、ADCCLK為AD9826的采樣控制時序。

圖8 整體控制時序

4.2 試驗波形

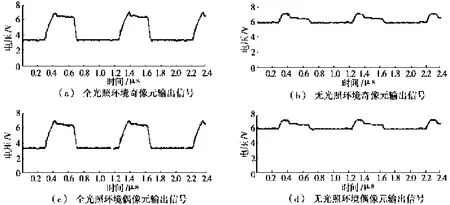

由示波器可觀察到TCD1703C的雙路輸出波形,如圖9所示。

圖9 CCD輸出信號波形

由于AD9826通過8位并行口高速輸出數據,用示波器難以觀察,可通過輸出口分別對地外接發光二極管(亮為1,滅為0)進行粗略觀察。因設置的信號輸入范圍為0~4 V,故當輸入電壓接近0 V時,發光二極管為00000000,此數將隨電壓增大而不斷增加;當輸入電壓為4 V時,輸出為11111111。因此,接入圖9所示CCD波形采樣后,全暗為00000000,隨著光照強度的增大而增加,直到全亮11111111。正常工作后可通過后續電路傳輸至計算機進行詳細數值分析,這里不再贅述。

5 結論

本文結合二相線陣CCD輸出信號的特點及其后續處理電路復雜的現狀,提出了一種通過專門集成的數據處理器對其雙路信號進行高速處理的方法。該方法簡化了信號處理電路的設計,解決了高速二相線陣輸出信號處理復雜的問題,具有較高的應用價值。經在實際電路中驗證,電路結構簡單,工作穩定可靠,處理結果可以滿足應用要求。

[1]王慶有.圖像傳感器應用技術[M].北京:電子工業出版社,2003.

[2]魏常偉,袁縱橫,張文濤,等.基于FPGA的新型告訴CCD圖像數據采集系統[J].測控技術與儀器儀表,2010(4):77-80.

[3]胡勝,楊雷,宋躍,等.基于ARM &FPGA的CCD圖像識別裝置[J].儀表技術與傳感器,2012(1):54-56.

[4]陳飛明,曹萬民,韓蘇雷,等.用二相雙列線陣CCD器件實時采集衍射圖樣[J].洛陽工學院學報,2001,22(3):83-86.

[5]閻石.數字電子技術基礎[M].北京:高等教育出版社,2006.

[6]王金明.數字系統設計與Verilog HDL[M].北京:電子工業出版社,2011.

[7]王慶有.CCD應用技術[M].天津:天津大學出版社,2000.

[8]魏冬冬,王大勇,李彩霞.CCD時序驅動電路的設計[J].傳感器與微系統,2011,30(9):112-114.

[9]商小川,周輝,張星祥,等.基于FPGA的大面陣CCD高幀頻驅動電路設計[J].液晶與顯示,2009,24(5):735-739.

[10]付天舒,趙春暉.基于Verilog的線陣CCD驅動時序設計[J].光學技術,2010,36(5):740-743.

[11]張殿富,趙源.基于FPGA的線陣CCD驅動時序及模擬信號處理的設計[J].國外電子元器件,2009,17(1):41-43.