基于多環鎖相寬帶細步進頻率合成器的設計

張文鋒,劉武廣,宋翔宇

(中國西南電子設備研究所 四川 成都 610036)

現代軍事電子對頻率源的綜合性能提出了越來越高的要求。寬頻段覆蓋、細頻率步進、低相位噪聲和低雜散水平成為了頻率合成器的重要發展趨勢。為實現上述目標,基于多環鎖相的綜合頻率合成方式成為了當前高端頻綜的主流設計方法。文中采用多環鎖相技術實現的寬帶頻綜,通過合理的頻段選擇方案、細步進雜散規避等關鍵設計技術的運用,較傳統單環鎖相式頻率源具備更低的相位噪聲、更小的頻率步進和低雜散等特點[1]。

1 多環鎖相寬帶頻綜設計原理

1.1 單環鎖相頻率合成器

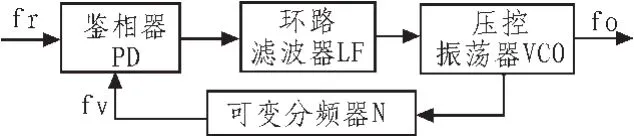

鎖相環(PLL)是一個負反饋的相位控制系統,基本的鎖相環路包括鑒相器 (PD)、環路濾波器 (LF)、壓控振蕩器(VCO)和可變分頻器幾個基本部分組成。其原理圖如圖1所示[2]。

圖1 單環鎖相頻率合成原理框圖Fig.1 Block diagram of PLL

圖1中,可變分頻器一般可集成在鎖相環芯片內部,通過程序進行控制。一般鎖相環頻率合成器的帶內相位噪聲計算方法為:

式中,PNSYNTH為頻率合成器帶內相位噪聲,PNTOT為鎖相環芯片底噪。

為保證能夠得到較高的頻率分辨率,一般只能通過降低鑒相頻率實現,造成N值加大,由(1)式可知,相位噪聲將惡化。因此,對于單環鎖相頻率合成器,相位噪聲和頻率分辨率是相互制約的指標。

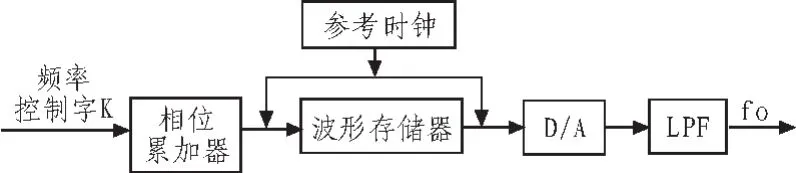

1.2 直接數字頻率合成器

直接數字頻率合成器(DDS)由相位累加器,波形存儲器,數模轉換器,低通濾波器和參考時鐘五部分,如圖2所示。在參考時鐘的控制下,相位累加器對頻率控制字K進行線性累加,得到的相位碼對波形存儲器尋址,使之輸出相應的幅度碼,進過數模變換器得到相對應的階梯波,最后經低通濾波器得到連續變化的所需頻率的波形[3]。

圖2 DDS頻率合成原理框圖Fig.2 Block diagram of DDS

DDS利用了相位反饋控制原理控制頻率輸出,不需要外部輔助頻率捕獲,易于集成,可實現很高的頻率分辨率,但是工作頻率有限,雜散水平較難控制。因此,將PLL和DDS組合起來,綜合運用兩者的優勢,可以既保證高頻率輸出,又能實現很高的頻率分辨率。

1.3 多環鎖相頻率合成器

多環鎖相頻率合成器有多種組成結構,包括PLL組合、DDS+PLL等,其中DDS+PLL的結構因頻率分辨率高和低相噪等優點,應用最為廣泛[4]。本文中選用的實現結構的設計思想是,利用DDS產生基帶信號,經與PLL兩次混頻擴頻,產生寬頻帶的高分辨率參考信號,進入鎖相環倍頻拓寬輸出頻率范圍,同時利用的PLL良好的窄帶載波跟蹤特性對DDS參考信號的雜散分量進行跟蹤濾波器,最終實現低相噪寬帶細步進頻綜輸出。

2 多環鎖相寬帶頻綜設計方案

2.1 設計目標

下面以1個工程實例為目標,介紹基于DDS+PLL多環鎖相技術設計寬帶頻綜的工作原理。該工程實例的主要技術指標要求為:

輸出頻率:10~13 GHz;

頻率步進:10 kHz;

輸出功率:>12d Bm;

相位噪聲:≤-90 dBc/Hz@1 kHz;≤-90 dBc/Hz@10 kHz;

諧波抑制:<-15 dBc;

雜散抑制:<-65 dBc;

2.2 設計方案

經分析,同時滿足細頻率步進和低相位噪聲、低雜散是設計難點。文中采用DDS+PLL多環鎖相頻率合成技術實現,工作原理如圖3所示。

圖3 DDS+PLL多環鎖相頻率合成原理框圖Fig.3 Block diagram of DDS+PLL Frequency Synthesizer

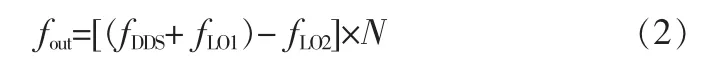

這是由多個鎖相環組成的電路結構。環路A為直接數字頻率合成環路,主要功能是產生步進細調的頻綜基帶,通過DDS產生步進10 kHz、帶寬100 MHz的基帶頻率信號;環路B為鎖相點頻源,產生S波段低相噪點頻,通過與DDS信號混頻,把細步進基帶頻譜搬移到S波段,帶寬不變;環路C為鎖相頻綜,產生L波段步進100 MHz的大步進頻綜,與第一級混頻輸出信號再次混頻,將窄帶細步進信號擴頻,輸出帶寬可大幅提高。環路D為通過鎖相倍頻N倍,實現X波段的寬帶細步進頻綜輸出。輸出信號與各功能環輸出信號的關系為:

該多環電路結構的主要優點是通過對DDS基帶信號的多級混頻,最終實現了寬頻段細步進的覆蓋。同時,通過合理的頻段分配,將各個鎖相環路的倍頻次數N控制在相對較低的水平,使相位噪聲的惡化量較小,保證了各個鎖相環及最終輸出信號相位噪聲的良好水平。

輸出信號的相位噪聲由單環A、B、C的相位噪聲和鎖相倍頻環D的倍頻次數決定。A、B、C環中,輸出相位噪聲由輸出頻率最高的B環(輸出頻率3.6 GHz)決定。鑒相器底噪為-233 dBc/Hz@10 kHz,鑒相頻率 100 MHz,反饋分頻比 N=3 600/100=36,根據(1)式可以估算,B環輸出信號相位噪聲為-233+10lg(100×106)+20lg72=-120 dBc(離載波 10 kHz處)。環路D最大倍頻次數約為6,最終輸出相位噪聲為-120dBc+20lg6=-104 dBc/Hz。考慮閃爍噪聲和電路中其他器件熱噪聲及工程實現性,實際信號輸出滿足-90 dBc/Hz@1 kHz@10 kHz的指標要求。

3 多環鎖相寬帶頻綜的電路設計與仿真

3.1 DDS電路設計

環路A采用了采用高性能DDS芯片AD9912。AD9912內置14 bit DAC;支持高達1GPS的采樣速率;采用1.8 V和3.3 V電源供電,在器件性能大幅提高的前提下也極大地降低了器件功耗;能夠生成高達400 MHz的捷變頻率正弦波形,最高頻率分辨率達到4 μHz。目前AD9912已廣泛用于頻率合成器、時鐘發生器、雷達以及各類測量裝置等[5]。

在環路A的設計中,100 MHz參考信號通過鎖相環倍頻至1 GHz,提供DDS參考時鐘,在頻率控制碼控制下實現細步進基帶輸出。

3.2 鎖相環電路設計

鎖相環路B、C采用了HITTITE公司的數字鎖相環芯片HMC440[6]。該芯片具有很低噪聲基底(-233 dBc/Hz@10kHz)和很高的鑒相頻率(1 300 MHz),集成5 bit數控程序分頻器,在本方案中的環路B、C使用,用于產生超低相位噪聲的fLO1和fLO2。

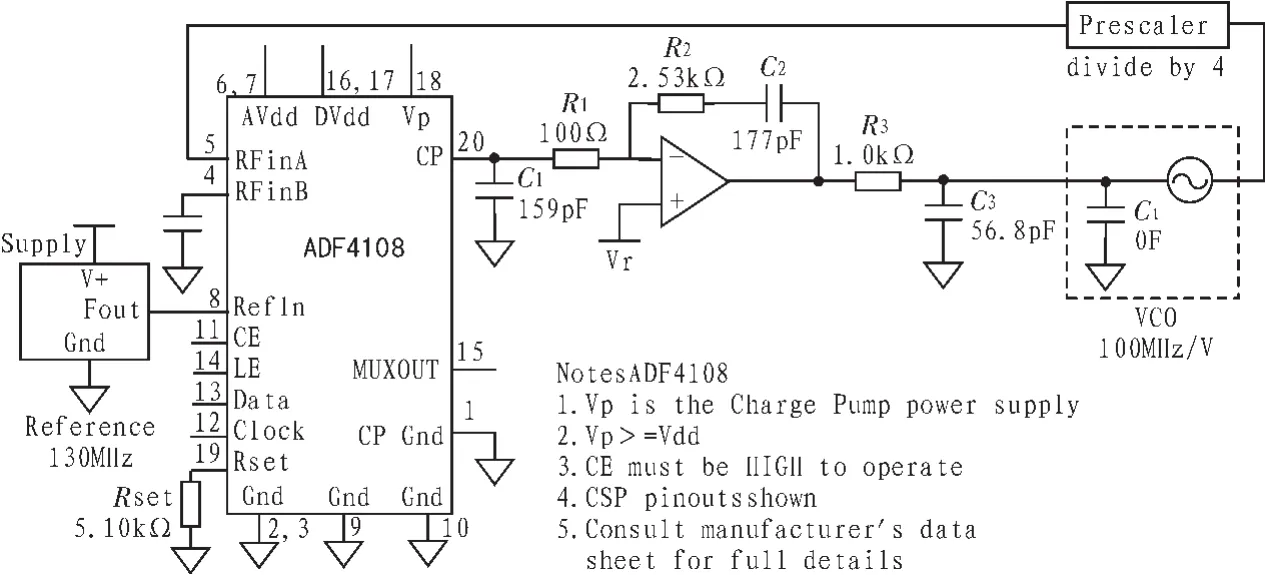

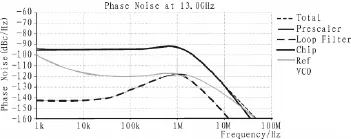

末級鎖相環路D采用ADI公司鎖相環芯片AD4108。該芯片工作頻率達8 GHz,控制簡單、功耗極低,同時具有良好的噪聲基底性能。經軟件仿真,末級鎖相環路電路參數及輸出相噪如圖4,5所示。

整個多環鎖相電路結構比較復雜,包含鎖相電路及數字控制電路等。為保證輸出信號相位噪聲和雜散抑制性能,結構設計中采取了多腔體分隔的結構,并注意微波吸收材料的使用,保證各個功能環路工作穩定且整體電磁兼容性能良好。

4 電路調試與測試結果

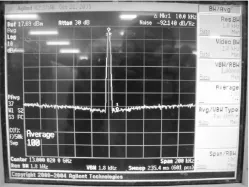

由于合理的方案設計和準確仿真,相位噪聲等主要指標均可實現。如圖6所示,全頻段輸出信號相位噪聲可達到-92 dBc@1kHz;-92 dBc@10kHz。

圖4 電路參數仿真結果Fig.4 Simulation result of PLL circuit

圖5 相位噪聲仿真結果Fig.5 Simulation result of phase noise

由于各功能環路輸出中間頻率信號較多,雜散控制是調試難點。在測試中發現,有少數頻點的近端有雜散較大,主要分布在參考100 MHz整數倍附近的細步進頻段,經分析,該類雜散的產生主要是由于環路A中DDS輸出信號與參考信號100 MHz及其諧波經鏈路泄露或空間輻射進入混頻器及鑒相器中,產生的高階交調出現在輸出信號近端,由于分布在鎖相環路帶寬以內,難以消除。該現象的產生說明,多環鎖相的細步進頻綜對模塊內部各功能單元的電磁屏蔽與隔離要求非常高。通過調試分析,可通過改變A、C環路輸出頻率和環路D的倍頻次數N的方法規避和解決。根據公式(2),通過掃頻,一旦發現存在近端雜散的頻率點,通過改變fDDS、fLO2和末級鎖相環倍頻次數N的頻率組合,同樣可以實現相同頻率的輸出,且fDDS發生改變,與100 MHz的高階交調雜散分布遠離主信號中心,可被末級鎖相環路濾波器濾除。圖7為經過后期頻率控制程序處理前后的雜散分布對比圖,可見主信號近端雜散已經明顯消除。

圖6 相位噪聲測試結果Fig.6 Test result of phase noise

經不斷調試改進,各項指標最終測試結果如表1,均滿足設計指標要求。

圖7 雜散優化前后對比Fig.7 Contrast of spur optimization

表1 頻率合成器測試結果Tab.1 Test result of frequency synthesizer

5 結 論

文中介紹了基于多環結構的鎖相寬帶頻率合成技術,在實現細頻率步進和低雜散的指標要求情況下,相位噪聲可達到≤-92 dBc/Hz@1 kHz,滿足系統對高質量頻率合成器的需求,具有較好的應用前景。

[1]梁劉永,張龍.X波段低相噪跳頻源的設計與實現[J].電子設計工程,2012(4):135-138.LIANG Liu-yong,ZHANG Long.Design of an X-band low phase noise local oscillator[J].Electronic Design Engineering,2012(4):135-138.

[2]張厥盛.鎖相技術[M].西安:西安電子科技大學出版社,2001.

[3]趙雨,陳金鷹,丁然.基于DDS和PLL的高性能信號源設計[J].中國集成電路,2012(3):39-43.ZHAO Yu,CHEN Jin-ying,DING Ran.The Design of high performance signal source based on DDS and PLL[J].China Integrated Circuit,2012(3):39-43.

[4]楊光,楊杰,蔣國瓊.基于雙環X波段低相噪頻率合成器的設計與實現[J].信息與電子工程,2012(1):68-71 YANG Guang,YANG Jie,JIANG Guo-qiong.Design and implementation ofX-band low phase noise frequency synthesizer using dual-loop technology[J].Information and Electronic Engineering,2012(1):68-71.

[5]郭映江,丁滿來,王玲.S波段捷變頻頻率源研究[J].微波學報,2010(8):342-344.GUO Ying-jiang,DING Man-lai,WANG Ling.The research of S-Band frequency agilesignalsource[J].Journalof Microwaves,2010(8):342-344.

[6]喬通,周遷.鑒頻鑒相器HMC440的C波段頻率合成中的應用[J].現代電子技術,2007(13):38-42.QIAO Tong,ZHOU Qian.Application of phase frequency detetor HMC440 in C band synthesizer[J].Modern Electronics Technique,2007(13):38-4.