基于FPGA的MIMU信號處理技術研究

高挺挺,王明明,潘 輝

(中國空空導彈研究院 河南 洛陽 471009)

由微加速度計和微陀螺儀構成的微型慣性測量組合MIMU(micro inertial measurement unit)是微機電系統的一個重要分支,是國際上近年來發展起來的新技術,是一種依靠自身設備的自主式慣性測量組合,它具有數據更新率高、短期精度和穩定性好等特點,加之其具有體積小、重量輕等優點,在姿態測控、武器制導和其他軍事及民用領域具有廣闊的應用前景[1-3]。由于MIMU慣性器件具有傳統慣性器件不具備的優點,極有可能成為未來航空航天系統的主要慣導器件,美國、日本和俄羅斯等國均已在這方面開展器件和應用研究,國內清華大學和北京大學較早開展MIMU的研究,“十一五”期間已研制出高精度MIMU樣件。

MIMU具有其他器件不可比擬的優越性但是現有MIMU的接口形式和數據傳輸協議與目前激光陀螺和光纖陀螺不一致,無法直接應用系統中去,MIMU在使用和測試上存在一定困難。本文的目的是通過MIMU信號處理電路,使MIMU的信號輸出格式與目前應用系統和地面測試系統相兼容,為MIMU的應用驗證研究提供條件,為高精度微型慣性測量組合的應用提供技術支持。

1 設計要求

1.1 MIMU接口形式

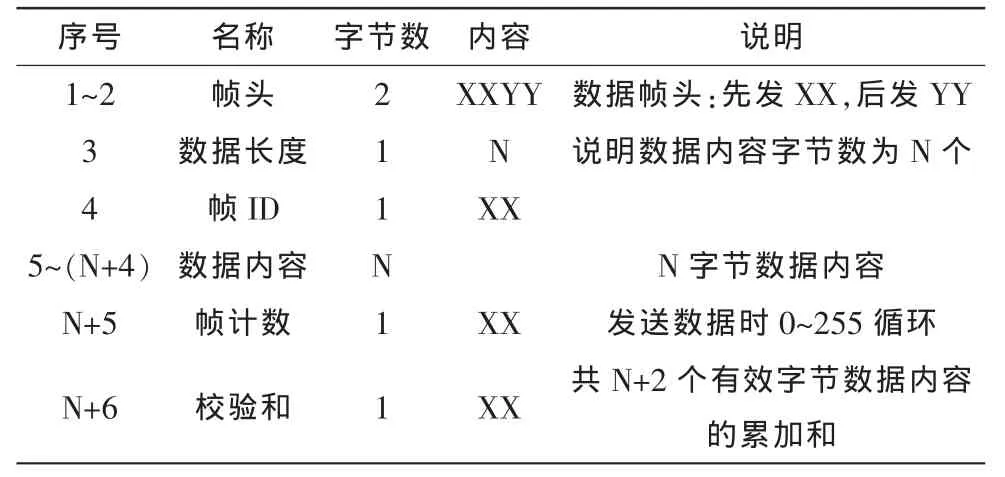

擬使用的MIMU采用標準RS422接口,波特率為230.4 kbps,通訊格式為:1個起始位,8個數據位,1個停止位,無奇偶校驗位。產品正常工作時,一幀數據有31個字節,包含有幀頭、數據長度、幀ID、加速度計數據、陀螺數據、幀計數、校驗和等內容。MIMU的數據格式如表1所示。

表1 MIMU幀數據格式Tab.1 Format of MIMU data in one frame

1.2 激光或光纖陀螺

目前IMU通常采用激光或光纖陀螺,其輸出為脈沖頻率調制方式,通過專用接口組件送到應用系統進行處理或送到性能測試系統進行測試。

因此,MIMU不能直接應用到目前的系統上進行試用和驗證,要先進行匹配性設計,設計信號處理電路,其功能是:對MIMU信號進行轉換,將標準RS422輸出轉化為目前IMU頻率調制的TTL脈沖輸出形式,使MIMU的接口與應用系統和測試系統的接口相匹配,從而實現MIMU的應用驗證研究。

1.3 技術要求

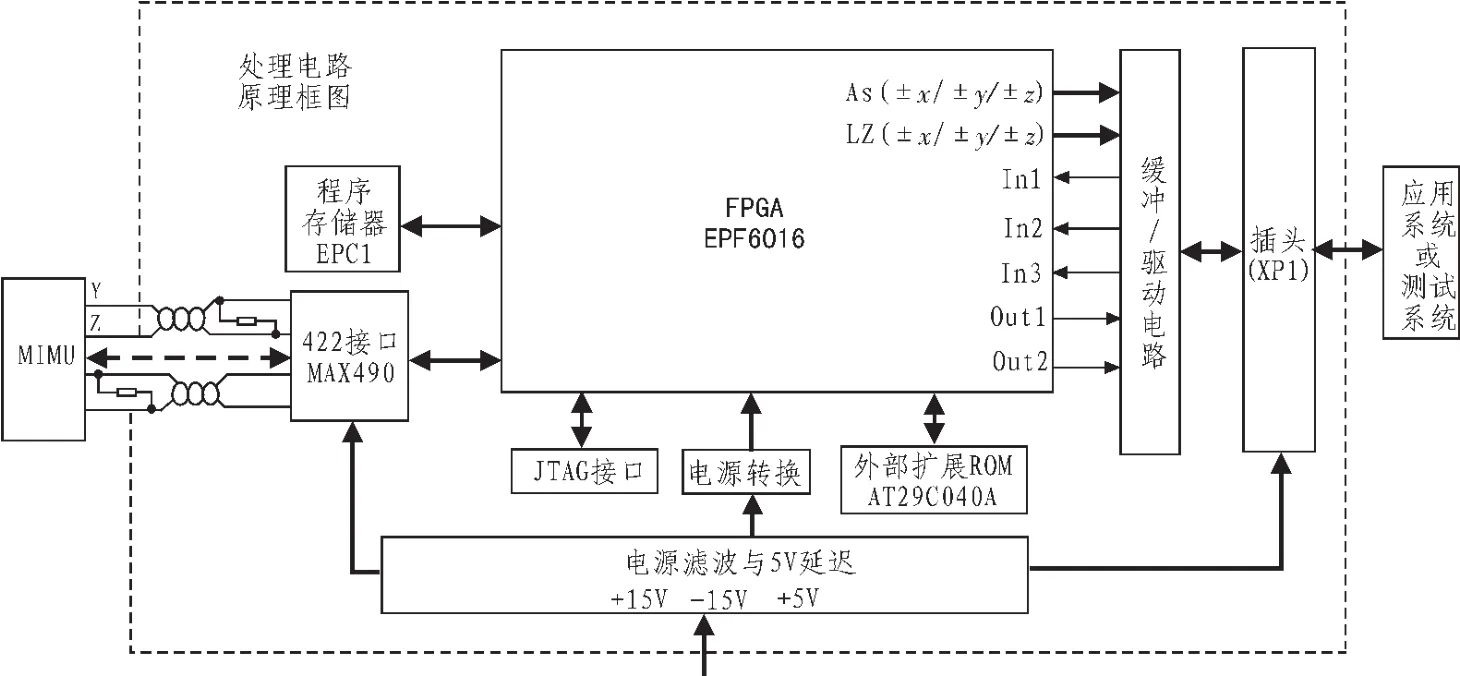

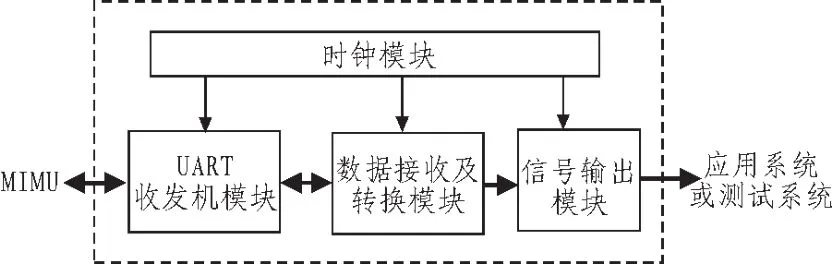

基于FPGA的MIMU信號處理電路的系統框圖如圖1所示。

從上圖中可以看出,信號處理電路要同時滿足MIMU和激光或光纖陀螺的接口指標要求,不間斷的接收MIMU發送的陀螺和加速度計信息,在硬件平臺的基礎上完成MIMU數據接收、處理和發送,然后提供足夠精度的慣性測量數據。

信號處理電路的主要技術指標有:

圖1 系統總體結構圖Fig.1 System architecture overview

1)實時接收MIMU發送的RS422格式數據,可識別幀類型,并進行校驗。

2)從信號線上分別輸出相應的計數脈沖信號,脈沖個數按照當前的有效MIMU數據計算得出。

2 硬件設計方案

2.1 主處理器的選擇

根據信號處理電路的技術要求,處理電路完成信號處理與轉換功能沒有復雜的數學運算,本設計中FPGA選用Altera公司的EPF6016芯片作為主處理器。該芯片具有豐富的硬件資源,能夠真正實現多模塊并行工作,具有低成本、低功耗、小體積等突出優點[4],在5 V供電電壓下,該芯片能夠提供大于100 mA的I/O驅動能力,能夠高速、準確地完成MIMU輸出信號的接收、處理以及飛控艙信號的輸出和驅動。

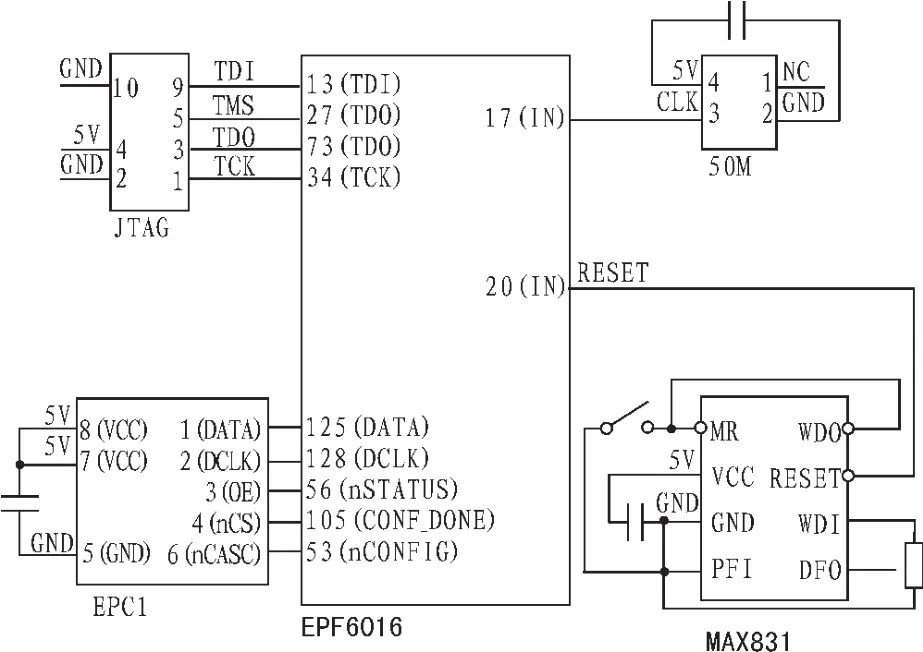

2.2 FPGA最小系統

FPGA最小系統是FPGA系統工作所需的基本電路,主要包括電源電路、時鐘電路、復位電路、JTAG電路以及配置芯片電路等。FPGA最小系統電路圖如圖2所示。

EPF6016采用被動串行(PS)配置方式。MSEL1、MSEL0是EPF6016選擇配置方式的引腳,外圍電路中均接地,選擇PS 方式[5]。

配置芯片是一種能產生配置時序的ROM,分為一次編程型和可擦除型兩種[6]。本設計采用Altera公司的EPC1系列配置芯片,在程序最終測試成功后,寫入該芯片中。FPGA在上電后,會自動從配置芯片中讀出配置數據,存入SRAM中。

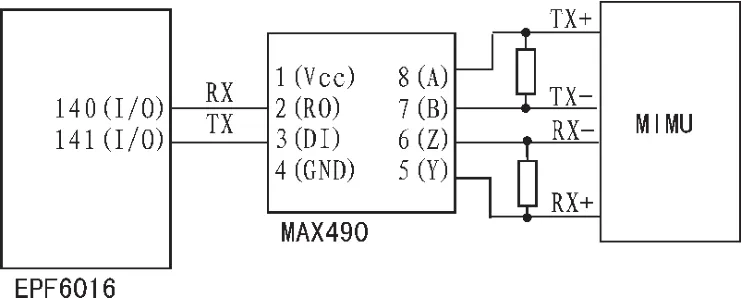

2.3 MIMU接口電路

MIMU接口電路主要包括供電電路部分和數據通信電路部分,采用31針的微矩形航空接頭。MIMU所需的供電電壓為±15 V和5 V,由外部電源提供供電。MIMU的數據通信接口采用標準的RS422異步串行口,波特率為230 400 bps,接口電路如圖3所示,主要是在MIMU接口與FPGA主處理器之間通過1個RS422收發器,將差分信號轉化為TTL電平信號。本設計中采用MAX490芯片進行差分信號轉換,可實現全雙工數據通信,快捷方便。

圖2 FPGA最小系統電路圖Fig.2 The minimal circuit of FPGA

圖3 MIMU通信接口電路圖Fig.3 The interface between MIMU and FPGA

2.4 信號輸出電路

信號輸出電路主要是提供足夠的驅動能力,輸出應用系統或測試系統所需的慣性單元接口信號。由于FPGA芯片EPF6016的I/O管腳能夠提高不小于100 mA的驅動能力,本設計直接用FPGA芯片的I/O管腳進行驅動,不再考慮增加驅動能力。

3 軟件設計方案

根據系統功能需求,軟件實現分成3部分:第一部分實現對MIMU發送RS422數據的接收與實時處理;第二部分實現向應用系統或測試系統實時發送帶有加速度角速度信息的脈沖數據;第三部分實現系統功能自檢。

信號處理電路軟件是用Verilog HDL語言編寫的FPGA程序,主要包括頂層模塊、時鐘模塊、UART發收機模塊、數據接收和轉換模塊以及信號輸出模塊等5個模塊,其原理框圖如圖4所示。

圖4 FPGA內部邏輯圖Fig.4 FPGA logic diagram

3.1 頂層及時鐘模塊

頂層模塊主要功能是確定FPGA的輸入輸出,實現輸入輸出管腳以及內部各個模塊彼此之間的連接和信號、數據的傳輸。

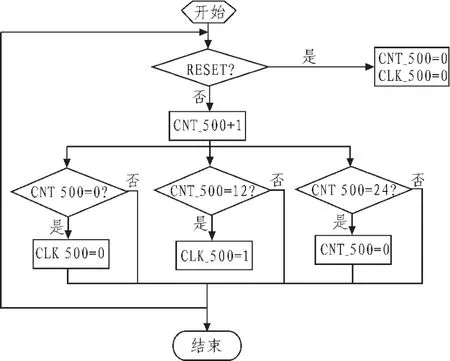

時鐘模塊主要是為信號輸出模塊提供500 ns基礎時鐘、角速度信號輸出所需的同步信號Out1以及加速度信號輸出所需的計時信號。其中500 ns時鐘是對50 MHz系統時鐘進行分頻獲得,Out1信號則是以外部輸入的信號In1為基準,而計時信號則是對外部輸入的信號In3計數產生的,以500 ns時鐘為例,流程圖如圖5所示。

圖5 時鐘模塊流程圖Fig.5 Flow chart of the clock module

3.2 UART收發機模塊

UART收發機模塊的功能是實現對標準的異步串行數據讀取,主要包括起始位檢測、同步時鐘產生、波特率計數以及數據讀取等4個部分。

根據異步串行數據的標準,在空閑狀態下,數據線上為高電平,當有數據來臨時,首先會把數據線拉低,這一位即是起始位。起始位檢測即是根據這一特性,在空閑狀態下檢測數據線的下降沿,并把標志寄存器置1,在其它狀態下則把標志寄存器置0。

波特率計數是在50 MHz系統時鐘的基礎上分頻,循環計數,產生所需的波特率。與時鐘模塊中計數不同的是,它只在起始位標志為1時或者數據狀態不為IDLE時才循環計數,其它狀態下計數寄存器都為0,不進行計數。同步時鐘則是在計數寄存器中的數值為分頻因數1/2的這一時鐘周期內為高電平,其余都為低電平。

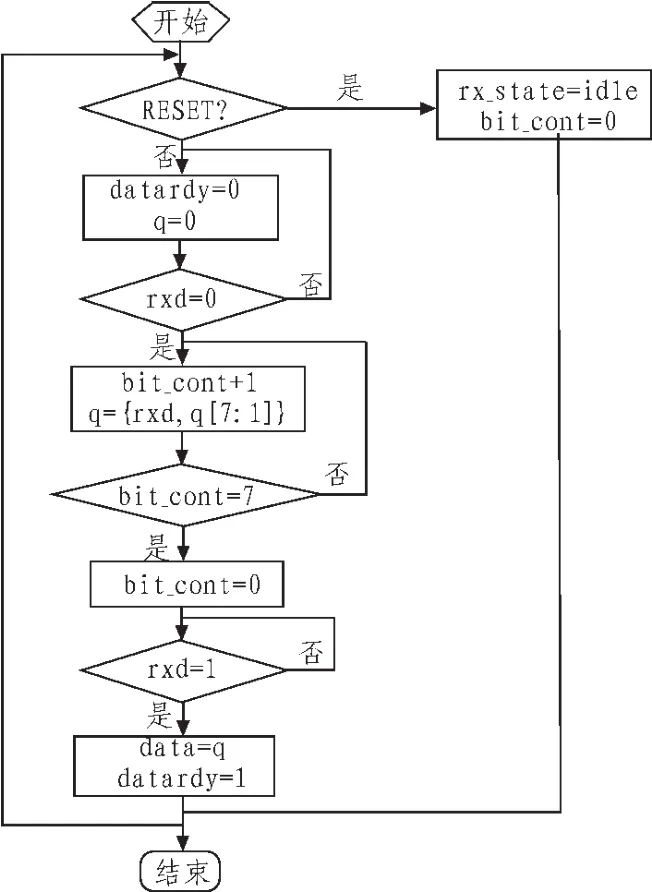

數據讀取部分采用狀態機的模式編寫,包括了idle、shift、stop 3個狀態,這3個狀態的操作都是在rxdclk為1的條件下執行。當處于idle狀態下,程序對接收完畢標志datardy以及移位寄存器q進行清零,同時對數據線rxd電平進行判斷,如果是低電平,則進入shift狀態,否則還停留在idle狀態。shift狀態中,數據位數計數器bit_cont每次加1,移位寄存器右移一位,并把數據線上當前的一位數據放置于移位寄存器的最高位。當bit_cont等于7時,跳出shift狀態,進入stop狀態。stop狀態中,檢測的停止位時,把移位寄存器q中數據賦予輸出寄存器data,并置接收完畢標志datardy為1。數據讀取部分的流程圖如圖6所示。

圖6 UART模塊流程圖Fig.6 Flow chart of the UART module

3.3 數據接收及轉換模塊

數據接收及轉換模塊包括兩個部分:一是對MIMU發出的31字節數據進行接收、校驗等;二是將MIMU的角速度、加速度數據轉換成相應的脈沖數。

數據接收部分則根據MIMU的通信協議,首先對數據幀頭進行檢測,當前兩個字節數據是幀頭數據時,則進行下面的操作,不是幀頭數據時則放棄該數據,重新檢測數據幀頭。檢測到數據幀頭后,則對接下來的28個字節數據進行接收、存儲,以及計算它們的累加和。然后接收最后一個字節數據,并與前面28字節數據的累加和比較,相等則把標志寄存器置為1,表明該幀數據接收完畢,不相等則說明這一幀數據中出現有誤碼,須舍去該幀數據。

數據轉換部分則是對上面接收的加速度、角速度值按前面介紹的增量當量和刷新時間轉換成各個通道的脈沖數。在這里考慮到角速度和加速度的量程以及精度等因數,把MIMU輸出的每個通道數據的高八位以及低十二位舍去,取其中十二位作為有效數據計算。首先,提取最高位數值,作為符號標志。當符號標志為1時,表明該數值為負數,取原數據的反碼作為其數值的絕對值;當符號標志為0時,表明該數值為正數,原數據即為其數值的絕對值。然后分別計算角速度和加速度的輸出脈沖數,并賦值予輸出接口,其中對于角速度脈沖數,當符號標志為1時,計算出的脈沖數賦予負通道,正通道賦值0;當符號標志為0時,計算出的脈沖數則賦予正通道,負通道賦值0。

3.4 信號輸出模塊

信號輸出模塊包括角速度信號輸出和加速度信號輸出兩個部分。

角速度通道輸出的脈沖為負脈沖,以固定頻率輸出脈沖,直到所需脈沖個數輸出完畢為止。另外,在Out1信號為高電平時,輸出正通道,在Out1信號為低電平時,輸出負通道。

加速度通道輸出的脈沖為正脈沖,在計時信號開始后,以固定頻率輸出脈沖,即檢測到一個In3信號,輸出一個脈沖,直至所需脈沖個數輸出完畢為止。加速度通道符號標志為1時,負通道輸出脈沖,正通道輸出低電平;符號標志為0時,正通道輸出脈沖,負通道輸出低電平。

4 結 論

本文所設計的信號處理電路充分考慮了MIMU所使用的RS422協議及幀格式要求,針對現有應用系統或測試系統所使用的特殊數據傳輸格式進行設計,實現了RS422數據信息向脈沖調制頻率信號的轉變。

通過對MIMU信號協議轉換技術的研究,實現了多標準協議相互轉換,通過MIMU信號協議轉換電路,可使MIMU的信號輸出格式與激光或光纖陀螺電氣屬性兼容進行相互轉換;設計了詳細的系統自檢功能,可在系統調試中迅速并準確定位故障位置,減少系統調試時間與工作量,縮短了系統研制進程;在MIMU信號處理平臺的設計過程中采取增加系統冗余度的設計方法,由于MIMU的信號刷新速率低,可在保證系統功能的前提下調高系統的可靠性。

MIMU信號協議處理技術研究的成功開展,可不需對現有系統進行任何修改,直接應用國內最先進的MIMU,為未來小型化、智能化的迫切需求,為開展精確制導武器專用MEMS器件設計、制造、封裝、測試等基礎工藝研究以及基于MEMS器件的新型機載制導武器系統應用基礎研究提供技術基礎。

[1]馬芮,孔星煒.MIMU在機載制導武器中的應用[J].飛航導彈,2008(6):45-50.MA Rui,KONG Xing-wen.The use of MIMU in airborne guided weapons[J].Winged Missiles Journal,2008(6):45-50.

[2]富立,時光煜.基于FPGA的組合導航系統專用接口板設計[J].中國慣性技術學報,2008,16(3):330-333.FU Li,SHI Guang-yu.Design of special interface board of integrated navigation system based on FPGA[J].Journal of Chinese Inertial Technology,2008,16(3):330-333.

[3]馬云峰.基于MIMU/GPS的組合導航計算機設計[J].計算機測量與控制,2009,17(3):549-551.MA Yun-feng.Design of MIMU/GPS Navigation Computer[J].Computer Measurement&Comtrol,2009,17(3):549-551.

[4]肖敏.PWM控制的FPGA實現[J].綿陽師范學院學報,2009,28(5):35-38.XIAO Min.FPGA implementation of the PWM control[J].Journal of Mianyang Normal University,2009,28(5):35-38.

[5]楊揚,葉芃,李力,等.基于FPGA的UART設計與實現[J].電子測量技術,2011,34(7):80-82.YANG Yang,YE Peng,LI Li,et al. Design and implementation of UART based on FPGA[J].Electronic MeasurementTechnology,2011,34(7):80-82.

[6]陳興文,劉燕.基于FPGA實現步進電機脈沖信號控制器設計[J].機械設計與制造,2006(2):86-87.CHEN Xing-wen,LIU Yan.The design of impulse signal controller in stepper motor based on FPGA[J].Machinery Design&Manufacture,2006(2):86-87.