基于Cadence的數(shù)據(jù)采集系統(tǒng)信號(hào)完整性仿真與優(yōu)化

李鵬飛,孟令軍,喬文生,于 磊

(中北大學(xué)a.電子測(cè)試技術(shù)國(guó)家重點(diǎn)實(shí)驗(yàn)室;b.儀器科學(xué)與動(dòng)態(tài)測(cè)試教育部重點(diǎn)實(shí)驗(yàn)室,山西 太原 030051)

責(zé)任編輯:時(shí) 雯

20世紀(jì)70年代初發(fā)展起來(lái)的新型半導(dǎo)體集成光電器件,經(jīng)過(guò)30多年的發(fā)展,IC輸出開(kāi)關(guān)速度不斷提高,電子系統(tǒng)的規(guī)模越來(lái)越大,工作頻率不斷提高,信號(hào)傳輸速度也越來(lái)越快,為了保證信號(hào)傳輸?shù)馁|(zhì)量,出現(xiàn)了對(duì)信號(hào)完整性的考慮和設(shè)計(jì)上的優(yōu)化。另外,對(duì)低功耗的高速信號(hào)傳輸器件(如FPGA)常見(jiàn)的內(nèi)核電壓為1.2 V,對(duì)外界環(huán)境的要求也越來(lái)越高,如系統(tǒng)能容忍的噪聲裕量,這也突出了信號(hào)完整性問(wèn)題。對(duì)于高速數(shù)據(jù)采集系統(tǒng),數(shù)字邏輯電路的頻率達(dá)到或超過(guò)50 MHz,信號(hào)傳輸速度較高,延遲等就相對(duì)減少,建立時(shí)間、保持時(shí)間均在皮秒級(jí)[1],從而增加了設(shè)計(jì)的復(fù)雜度。因此在高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)時(shí)采用了對(duì)關(guān)鍵信號(hào)進(jìn)行信號(hào)完整性的仿真,保證關(guān)鍵信號(hào)的傳輸質(zhì)量,從而得出更為合理的設(shè)計(jì)。本設(shè)計(jì)采用具有較強(qiáng)高速信號(hào)仿真功能的Cadence軟件,完成疊層參數(shù)、信號(hào)拓?fù)浣Y(jié)構(gòu)的建立以及布線(xiàn)等造成的影響、信號(hào)間的串?dāng)_等。

在高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)過(guò)程中,信號(hào)完整性上主要解決3個(gè)問(wèn)題:對(duì)關(guān)鍵信號(hào)建立正確合理的拓?fù)浣Y(jié)構(gòu);滿(mǎn)足系統(tǒng)相應(yīng)時(shí)序間的配合要求(信號(hào)的建立時(shí)間、最小脈寬、保持時(shí)間以及相位疊加等);進(jìn)行信號(hào)優(yōu)化設(shè)計(jì)。

1 數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)及原理

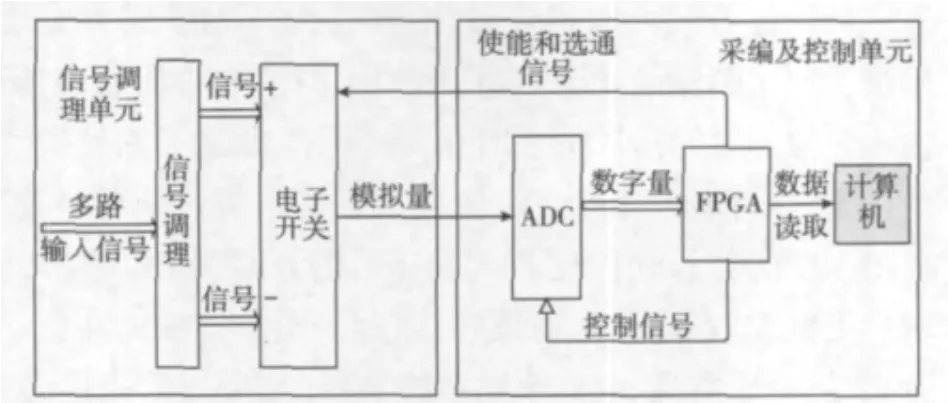

數(shù)據(jù)采集(DAQ)是指從傳感器和其他待測(cè)設(shè)備等模擬和數(shù)字被測(cè)單元中自動(dòng)采集非電量或者電量信號(hào),送到上位機(jī)中進(jìn)行分析、處理。本系統(tǒng)采用ADS8508芯片,是一種具有12位的模數(shù)轉(zhuǎn)化和250 kHz高采樣率的ADC芯片,然后將該信號(hào)送到FPGA中,本系統(tǒng)采用的FPGA選用Altera公司的Cyclone II系列EP2C8Q208。FPGA作為系統(tǒng)的核心組件,控制采集通道的換置、A/D轉(zhuǎn)換器的啟/停、數(shù)據(jù)轉(zhuǎn)換后在內(nèi)部FIFO中存放等。圖1為多路數(shù)據(jù)采集系統(tǒng)電路連接框圖。

圖1 高速數(shù)據(jù)采集系統(tǒng)電路連接框圖

該系統(tǒng)實(shí)現(xiàn)數(shù)據(jù)的多路選擇、采集、預(yù)處理和編碼功能。模擬信號(hào)源于上游各路傳感器的模擬信號(hào),經(jīng)信號(hào)調(diào)理電路進(jìn)行信號(hào)調(diào)理,通過(guò)多路模擬開(kāi)關(guān)進(jìn)行多路切換選通,將選通的多路信號(hào)輸入模數(shù)轉(zhuǎn)換器ADS8508,轉(zhuǎn)換得到的模擬量傳送到采集控制單元(FPGA)中。此外,采集控制單元還對(duì)數(shù)字信號(hào)進(jìn)行適當(dāng)?shù)臄?shù)據(jù)預(yù)處理,數(shù)據(jù)被存儲(chǔ)在FPGA內(nèi)嵌的FIFO[2]中等待Ft245讀取。同時(shí)根據(jù)對(duì)FPGA內(nèi)建的寄存器操作來(lái)實(shí)現(xiàn)采集系統(tǒng)的其他功能,如復(fù)位、標(biāo)定等。

2 信號(hào)完整性分析

信號(hào)完整性即信號(hào)在信號(hào)線(xiàn)上的傳輸質(zhì)量。問(wèn)題的主要根源是信號(hào)上升時(shí)間的減小。即使布線(xiàn)拓?fù)浣Y(jié)構(gòu)設(shè)計(jì)保持不變,如果采用了信號(hào)上升時(shí)間很小的IC芯片,現(xiàn)有設(shè)計(jì)也將處于臨界狀態(tài)或者停止工作。在高速數(shù)據(jù)采集設(shè)計(jì)中主要考慮的信號(hào)完整性問(wèn)題包括布線(xiàn)、阻抗匹配、串?dāng)_等。

2.1 布線(xiàn)

布線(xiàn)對(duì)信號(hào)完整性的影響主要包括延時(shí)和容性負(fù)載反射。實(shí)際操作中PCB布線(xiàn)會(huì)遇經(jīng)過(guò)孔、焊盤(pán)、短的stub線(xiàn)等,這樣會(huì)不可避免地引起PCB布線(xiàn)長(zhǎng)短的不一致,造成信號(hào)傳輸?shù)难訒r(shí)。此外,布線(xiàn)與過(guò)孔等相互之間均會(huì)產(chǎn)生寄生電容,必然對(duì)信號(hào)造成影響。走線(xiàn)中途的電容對(duì)信號(hào)的影響要從發(fā)射端和接受端兩個(gè)方面分析,對(duì)起點(diǎn)和終點(diǎn)都有影響。因此發(fā)生容性負(fù)載反射,對(duì)信號(hào)產(chǎn)生影響。

在高速信號(hào)中傳輸信號(hào),延時(shí)是影響信號(hào)完整性的一個(gè)考慮因素,在電子系統(tǒng)中,當(dāng)傳輸信號(hào)在PCB走線(xiàn)上的延時(shí)超過(guò)相應(yīng)信號(hào)的最小建立時(shí)間、最小脈寬、保持時(shí)間以及相位疊加等就會(huì)造成時(shí)序錯(cuò)誤,造成信號(hào)傳輸質(zhì)量下降。信號(hào)傳輸延遲主要取決于導(dǎo)線(xiàn)的長(zhǎng)度和導(dǎo)線(xiàn)周?chē)橘|(zhì)的介電常數(shù)。現(xiàn)今常見(jiàn)的PCB材料為FR4,其傳輸速度可達(dá)180 ps/in(1 in=2.54 cm)。對(duì)于同一塊高速信號(hào)傳輸?shù)腜CB板,解決延遲問(wèn)題可以通過(guò)以下途徑:縮短信號(hào)收發(fā)端間的布線(xiàn)距離;對(duì)于時(shí)序相關(guān)的信號(hào)線(xiàn)布線(xiàn)長(zhǎng)延時(shí)相差不能超過(guò)最小建立保持時(shí)間、最小脈寬以及保持時(shí)間等,從而保證信號(hào)傳輸質(zhì)量。

在信號(hào)傳輸過(guò)程中,信號(hào)遇到寄生電容時(shí),電容會(huì)快速充電,充電電流和信號(hào)電壓上升快慢有關(guān),充電電流公式為:I=C×dV/dt。在電容充電初期,阻抗很小,小于走線(xiàn)的特性阻抗[3]。信號(hào)在電容處發(fā)生負(fù)反射,這個(gè)負(fù)電壓信號(hào)和原信號(hào)疊加,使得發(fā)射端的信號(hào)產(chǎn)生下沖,引起發(fā)射端信號(hào)的非單調(diào)性。同理,信號(hào)到達(dá)接收端后,發(fā)生正反射,反射回來(lái)的信號(hào)到達(dá)電容位置,同樣發(fā)生負(fù)反射,反射回接收端的負(fù)反射電壓同樣使接收端信號(hào)產(chǎn)生下沖。

2.2 阻抗匹配

阻抗匹配是指負(fù)載阻抗與激勵(lì)源內(nèi)部阻抗互相適配,得到最大功率輸出的一種工作狀態(tài)。信號(hào)傳輸過(guò)程中負(fù)載阻抗等于信源內(nèi)阻抗(模與輻角分別相等),可以實(shí)現(xiàn)信號(hào)傳輸?shù)耐暾浴?/p>

驅(qū)動(dòng)源輸出信號(hào),經(jīng)過(guò)的互連線(xiàn)可以等效為一個(gè)具有阻抗的網(wǎng)絡(luò)。信號(hào)利用阻抗網(wǎng)絡(luò)進(jìn)行信息傳播時(shí),互連線(xiàn)構(gòu)成的阻抗網(wǎng)絡(luò)會(huì)隨著信號(hào)的電壓、電流變化引起瞬態(tài)阻抗的變化。這樣會(huì)造成信號(hào)相位疊加的不一致性,造成部分能量會(huì)被反射,剩余的能量仍會(huì)繼續(xù)傳輸。因此,在高頻電路中合適的阻抗匹配是保證信號(hào)完整性不可缺少的一個(gè)考慮因素。

2.3 串?dāng)_

信號(hào)串?dāng)_是信號(hào)高速傳輸時(shí),沒(méi)有電氣連接的信號(hào)線(xiàn)之間的電壓和電流感應(yīng)產(chǎn)生的電磁耦合現(xiàn)象,即能量傳輸網(wǎng)絡(luò)間的耦合,造成高速信號(hào)傳輸上的失真。信號(hào)線(xiàn)之間的電壓和電流感應(yīng)產(chǎn)生的耦合可以等效為天線(xiàn),產(chǎn)生交變磁場(chǎng),處于磁場(chǎng)作用區(qū)域范圍之內(nèi)的其他信號(hào)線(xiàn)會(huì)感應(yīng)出信號(hào)電壓。串?dāng)_的強(qiáng)度取決于器件及導(dǎo)線(xiàn)的幾何尺寸和相互距離。

3 數(shù)據(jù)采集系統(tǒng)仿真設(shè)計(jì)與優(yōu)化

多路信號(hào)采集系統(tǒng)采用Cadence中的SigXplorer軟件對(duì)進(jìn)行信號(hào)完整性仿真及優(yōu)化。為了驗(yàn)證系統(tǒng)方案的可行性,對(duì)系統(tǒng)前端信號(hào)進(jìn)行調(diào)理、多路選擇、信號(hào)隔離前后進(jìn)行分步仿真研究,實(shí)時(shí)監(jiān)測(cè)信號(hào)變化。

3.1 布線(xiàn)對(duì)信號(hào)完整性影響

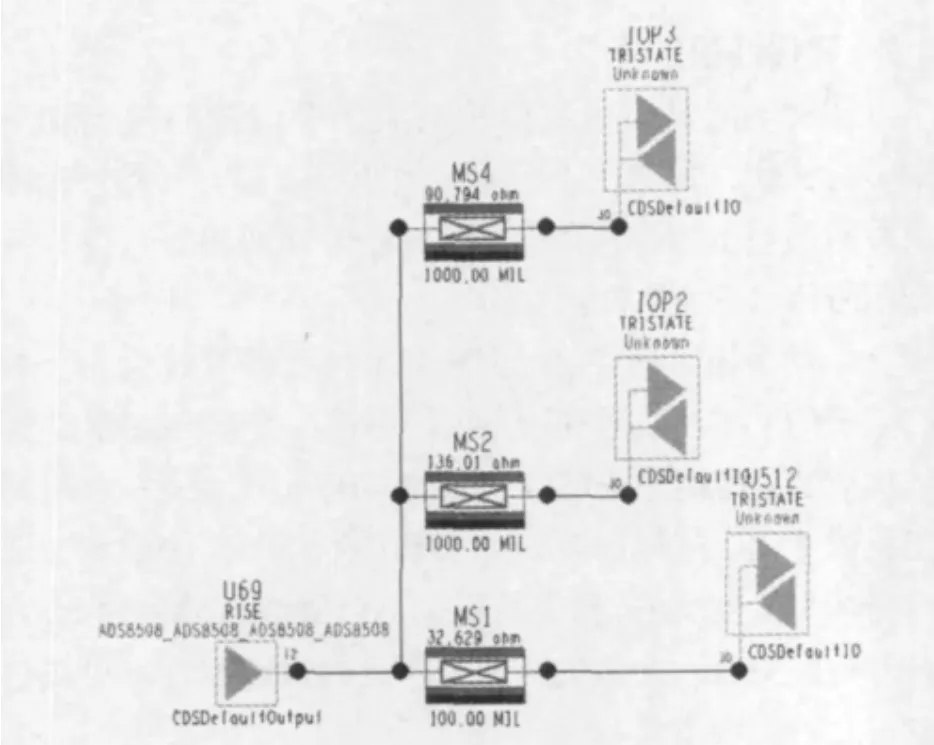

多路信號(hào)采集系統(tǒng)中采用的模數(shù)轉(zhuǎn)化芯片為ADS8508,PCB板設(shè)計(jì)時(shí)為保證單一網(wǎng)絡(luò)的信號(hào)質(zhì)量應(yīng)盡量減少布線(xiàn)造成的延時(shí),保證信號(hào)的完整性。本系統(tǒng)采用ADS8508芯片,當(dāng)ADS8508正常工作時(shí)轉(zhuǎn)化得到的數(shù)字信號(hào)在FPGA發(fā)出的Dataclk信號(hào)下降沿傳送[4]。因此,對(duì)系統(tǒng)關(guān)鍵信號(hào)Dataclk進(jìn)行信號(hào)完整性仿真及優(yōu)化設(shè)計(jì),分別選取布線(xiàn)長(zhǎng)度 100 mil(1 mil=0.025 4 mm),1 000 mil,1 000 mil布線(xiàn)寬度為5 mil,8 mil,5 mil進(jìn)行信號(hào)完整性測(cè)試比較。

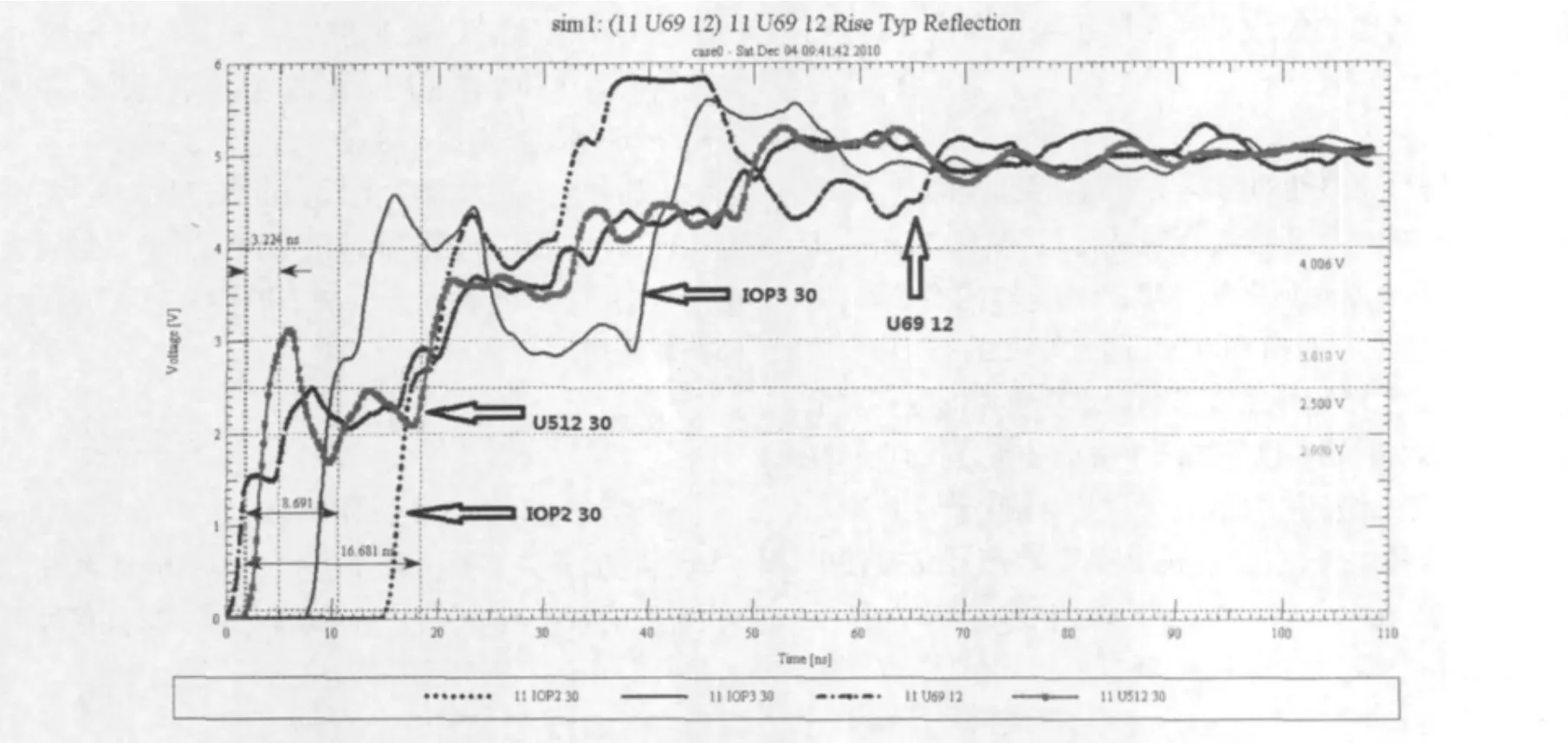

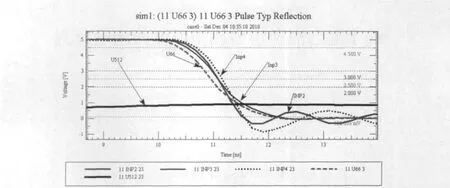

圖2為ADS8508到FPGA布線(xiàn)的Dataclk信號(hào)中利用SigXplorer軟件對(duì)進(jìn)行仿真原理圖。圖3為ADS8508到FPGA布線(xiàn)的Dataclk信號(hào)中利用SigXplorer軟件對(duì)進(jìn)行仿真波形整體比較圖。由圖3可知,布線(xiàn)長(zhǎng)度越長(zhǎng)信號(hào)的質(zhì)量越差,布線(xiàn)長(zhǎng)度為100 mil、寬度為5 mil時(shí),信號(hào)延時(shí)約為3.224 ns;布線(xiàn)長(zhǎng)度為1 000 mil、寬度為8 mil,信號(hào)延時(shí)約為8.691 ns;布線(xiàn)長(zhǎng)度為1 000 mil、布線(xiàn)寬度為5 mil時(shí),信號(hào)延時(shí)約為16.681 ns,信號(hào)失真最大。

圖2 Dataclk信號(hào)拓?fù)浣Y(jié)構(gòu)圖(截圖)

根據(jù)圖2、圖3可知,U69為ADS8508發(fā)出的信號(hào)波形圖,U69i為PCB布線(xiàn)理想狀態(tài)下0 mil時(shí)信號(hào)波形圖,U512為ADS8508將信號(hào)傳遞給FPGA第77引腳信號(hào)波形圖,假定布線(xiàn)10 000 mil時(shí)信號(hào)波形圖,此時(shí)信號(hào)失真較小。IOP3為PCB布線(xiàn)50 000 mil時(shí)信號(hào)波形圖,IOP2為PCB布線(xiàn)100 000 mil時(shí)信號(hào)波形圖,顯然PCB布線(xiàn)越長(zhǎng)信號(hào)延時(shí)越大、完整性越差。

3.2 阻抗匹配大小對(duì)信號(hào)完整性

阻抗匹配(Impedance matching)主要用于傳輸線(xiàn)上,來(lái)達(dá)至所有高頻的微波信號(hào)皆能傳至負(fù)載點(diǎn)的目的,不會(huì)有信號(hào)反射回來(lái)源點(diǎn),從而提升信號(hào)完整性以及電磁兼容性。

圖3 Dataclk信號(hào)仿真波形圖(截圖)

在多路數(shù)據(jù)信號(hào)隔離采集系統(tǒng)PCB設(shè)計(jì)中,阻抗匹配是通過(guò)改變阻抗力來(lái)進(jìn)行比較。要匹配一組線(xiàn)路,首先把負(fù)載點(diǎn)的阻抗值、傳輸線(xiàn)的特性阻抗值進(jìn)行歸一化。通過(guò)不同阻抗匹配比較,給出阻抗匹配對(duì)信號(hào)的影響程度,信號(hào)傳輸過(guò)程中負(fù)載阻抗和信源內(nèi)阻抗之間的特定配合關(guān)系。

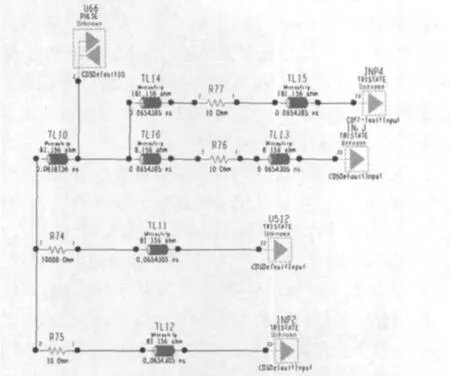

圖4為晶振Clk信號(hào)到FPGA布線(xiàn)的中利用SigX-plorer軟件對(duì)進(jìn)行阻抗匹配仿真原理圖。圖5為晶振Clk信號(hào)到FPGA布線(xiàn)的中利用SigXplorer軟件對(duì)進(jìn)行阻抗匹配仿真下降沿放大波形圖。

由圖4、圖5可知,阻抗匹配越大信號(hào)的質(zhì)量越差,阻抗匹配為10 kΩ時(shí),信號(hào)衰減最明顯,幅度小于1 V。

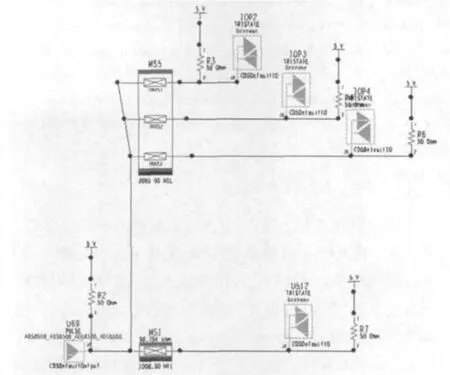

圖6為ADS8508的Dataclk信號(hào)到FPGA布線(xiàn)的中利用SigXplorer軟件對(duì)進(jìn)行信號(hào)串?dāng)_仿真原理圖。

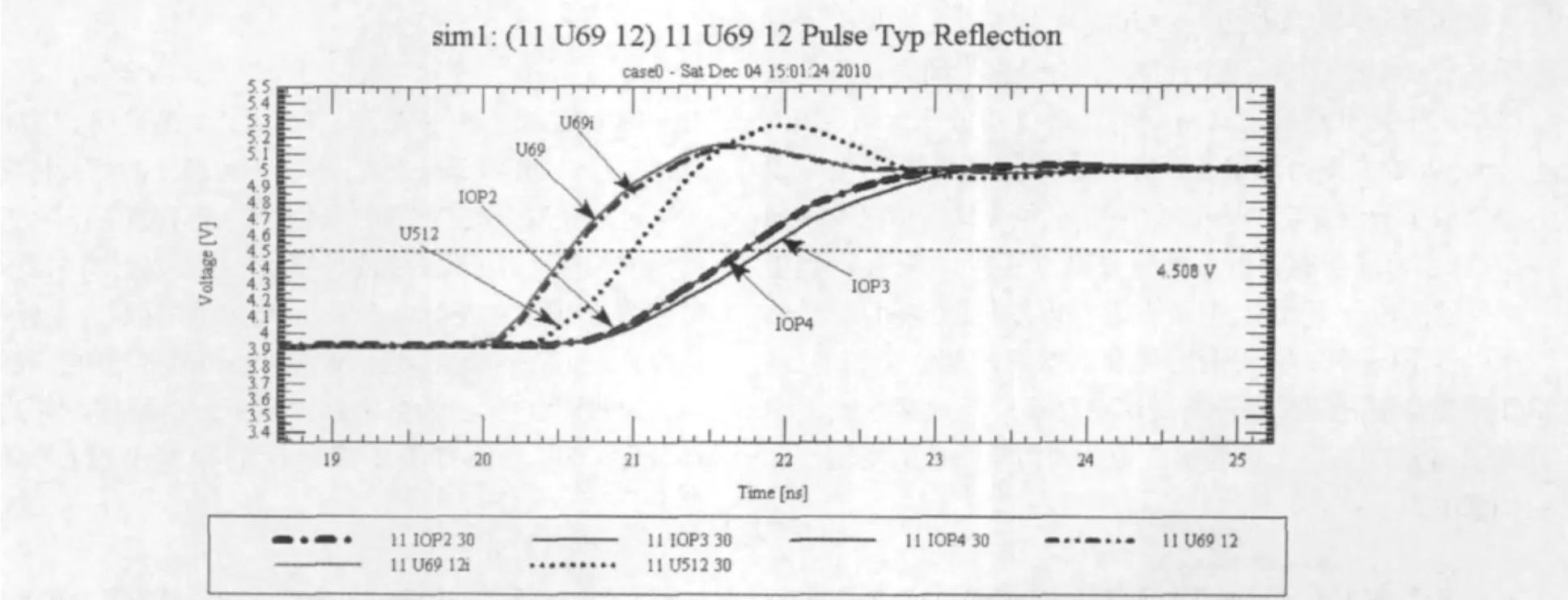

圖7為ADS8508的Dataclk信號(hào)到FPGA布線(xiàn)的中利用SigXplorer軟件對(duì)信號(hào)進(jìn)行串?dāng)_仿真整體波形放大圖。

圖4 Clk信號(hào)阻抗匹配拓?fù)浣Y(jié)構(gòu)圖(截圖)

圖5 Clk信號(hào)阻抗匹配下降沿放大波形圖(截圖)

圖6 Dataclk信號(hào)串?dāng)_拓?fù)浣Y(jié)構(gòu)圖(截圖)

由圖6、圖7可知,信號(hào)單獨(dú)走線(xiàn)的質(zhì)量遠(yuǎn)比信號(hào)相互間串?dāng)_走線(xiàn)高。信號(hào)U512為單獨(dú)走線(xiàn),IOP2/3/4為互相并行走線(xiàn)[5],顯然當(dāng)信號(hào)并行走線(xiàn)時(shí),信號(hào)完整性較差。只要有電流的存在,就會(huì)有磁場(chǎng)存在;電流發(fā)生變化,磁場(chǎng)也發(fā)生變化,電磁兼容性就降低。

4 結(jié)束語(yǔ)

本設(shè)計(jì)采用FPGA作為控制核心單元進(jìn)行高速數(shù)據(jù)采集,通過(guò)對(duì)信號(hào)完整性相關(guān)知識(shí)的了解,利用EDA工具(Cadence)對(duì)高速數(shù)據(jù)采集的關(guān)鍵信號(hào)進(jìn)行了設(shè)計(jì)仿真及優(yōu)化,分析和解決了實(shí)際電路中常見(jiàn)的幾種信號(hào)完整性問(wèn)題。通過(guò)對(duì)高速采集電路板級(jí)關(guān)鍵信號(hào)的仿真與優(yōu)化,解決信號(hào)完整性、電磁干擾等問(wèn)題,提高了信號(hào)的傳輸質(zhì)量,保證了數(shù)據(jù)采集的精度。

圖7 Dataclk信號(hào)串?dāng)_仿真波形放大圖(截圖)

[1]李新,張琳.利用Cadence Allegro進(jìn)行PCB級(jí)的信號(hào)完整性仿真[J].現(xiàn)代電子技術(shù),2002(6):83-85.

[2]張磊,雷震.高速電路設(shè)計(jì)和信號(hào)完整性分析[J].電子技術(shù)應(yīng)用,2001,27(6):70-73.

[3]李曉娟,劉學(xué)斌,胡炳,等.基于FPGA的CCD相機(jī)高速數(shù)據(jù)記錄系統(tǒng)[J].科學(xué)技術(shù)與工程,2007,19(7):4879-4884.

[4]李德明,張法碧.一種基于FPGA的雙音多頻信號(hào)設(shè)計(jì)[J].電視技術(shù),2011,35(21):48-50.

[5]朱志強(qiáng).信號(hào)完整性仿真自動(dòng)化技術(shù)基于Cadence軟件的應(yīng)用與研究[D].西安:西安電子科技大學(xué),2007.